LVPECL与LVDS电平互连:直流与交流耦合设计指南

描述

1. LVPECL 与LVDS 的互连

1.1 LVPECL 与LVDS 的直流耦合

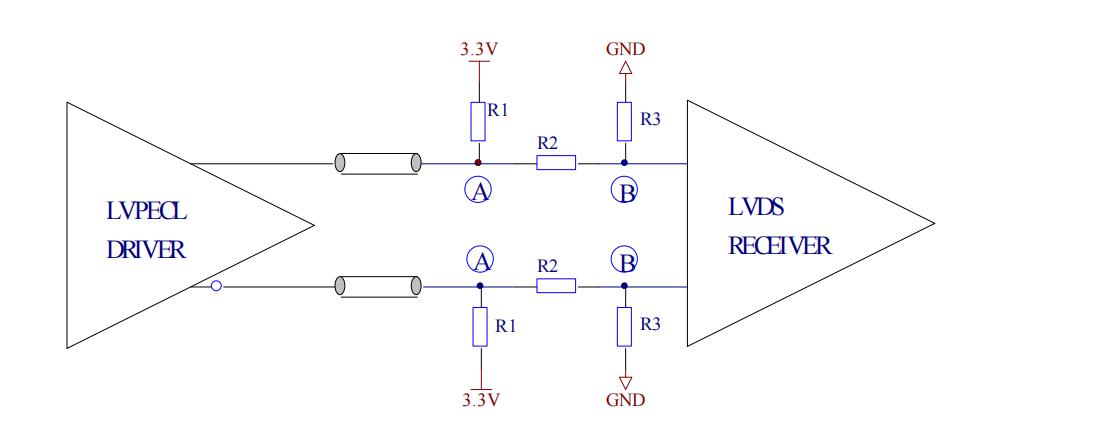

LVPECL 到LVDS 的直流耦合结构需要一个电阻网络,如图5 中所示,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到VCC-2V 时,LVPECL 的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL 输出信号经衰减后仍能落在 LVDS 的有效输入范围内。注意 LVDS 的输入差分阻抗为 100Ω,或者每个单端到虚拟地为 50Ω(图1所示),该阻抗不提供直流通路,这里意味着 LVDS 输入交流阻抗与直流阻抗不等。LVPECL 到 LVDS 的直流耦合所需的电阻网络需满足下面方程组:

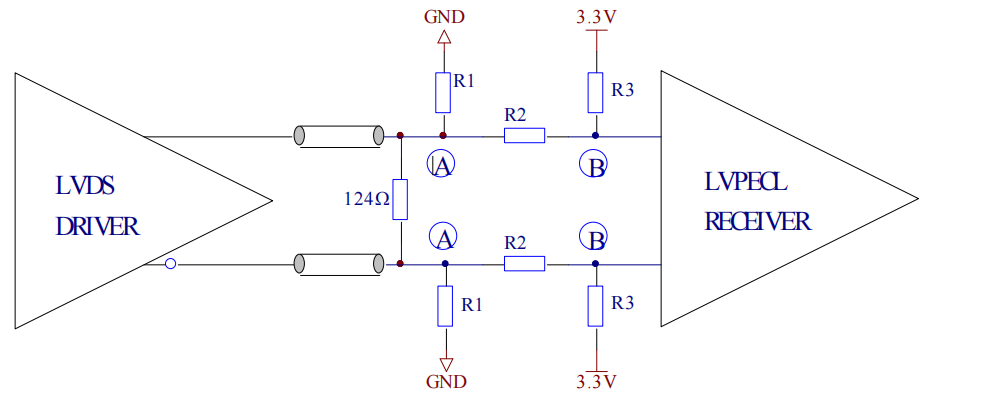

图1 LVPECL到LVDS的直流耦合

考虑VCC = +3.3V 情况,解上面的方程组得到:R1 = 182Ω,R2 = 47.5Ω,R3 = 47.5Ω,VA = 1.13V,

RAC = 51.5Ω,RDC =62.4Ω,增益 = 0.337。通过该终端网络连接LVPECL 输出与LVDS 输入时,实测得VA =2.1V,VB = 1.06V。假定LVPECL 差分最小输出电压为930mV,在LVDS 的输入端可达到313mV,能够满足LVDS 输入灵敏度要求。考虑信号较大时,如果LVPECL 的最大输出为1.9V,LVDS 的最大输入电压则为640mV,同样可以满足LVDS 输入指标要求。

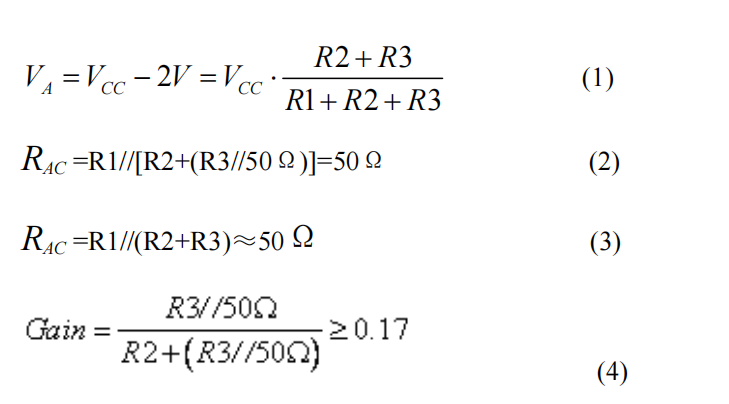

LVDS 与LVPECL 之间采用直流耦合结构时,需要加一个电阻网络,如图2 所示。该电阻网络完成LVDS

输出电平(1.2V)到LVPECL 输入电平(VCC-1.3V)的转换。由于LVDS 的输出是以地为参考,而LVPECL 的输

入是以 VCC 为参考,这需要在构建电平转换网络时注意 LVDS 的输出不会对供电电源的变化敏感;另一个

问题是需要在功耗和速度方面折中考虑,如果电阻值(R1、R2、R3)取得较小,由电阻网络和LVPECL 输入寄

生电容构成的时间常数较小,允许电路在更高的速度下工作。但是,由于这些电阻上流过较大的电流,使得

总功耗增大。这时,LVDS 的输出性能容易受电源波动的影响。还有一个问题就是要考虑阻抗匹配和网络衰

减问题,电阻值可以通过下面的方程导出。

图2 LVDS 到LVPECL 的直流耦合

在VCC 电压为+3.3V 时,解上面的方程得:R1 = 374Ω,R2 = 249Ω,R3 = 402Ω,VA = 1.2V,VB = 2.0V,

RIN = 49Ω,增益 =0.62。LVDS 的最小差分输出信号摆幅为500mVP-P,在上面结构中加到LVPECL 输入端

的信号摆幅变为310mVP-P,该幅度低于LVPECL 的输入标准,在实际应用中,读者可根据器件的实际性能做

出自己的判断。

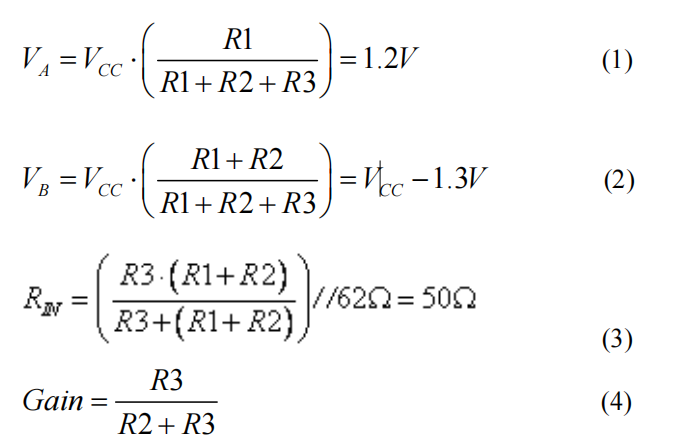

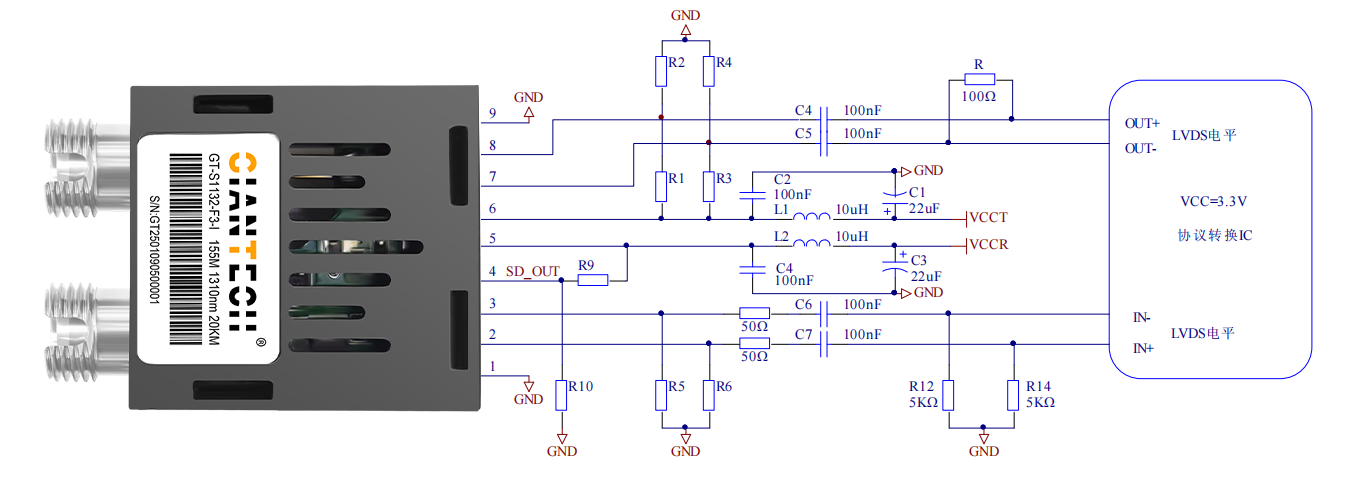

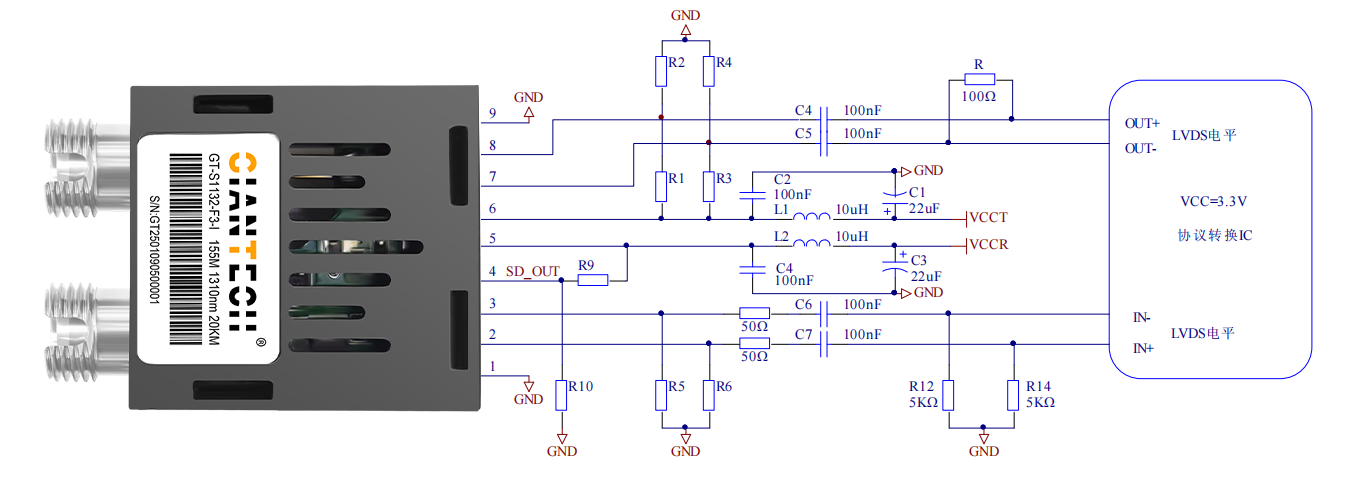

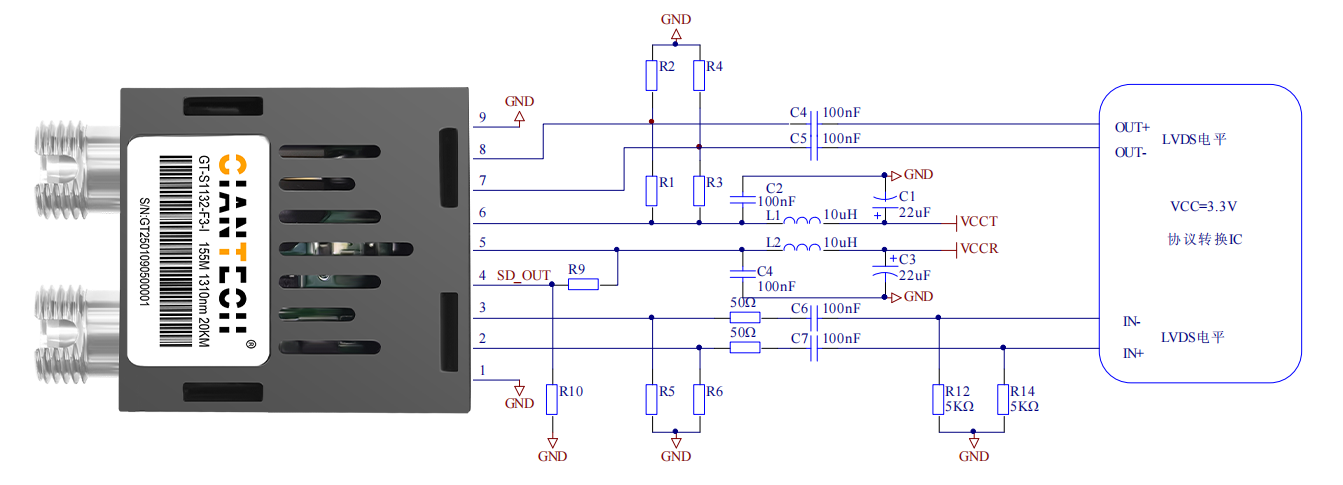

图 3 光模块与协议转换IC间LVPECL/LVDS电平的直流耦合

1.2 LVPECL与LVDS的交流耦合

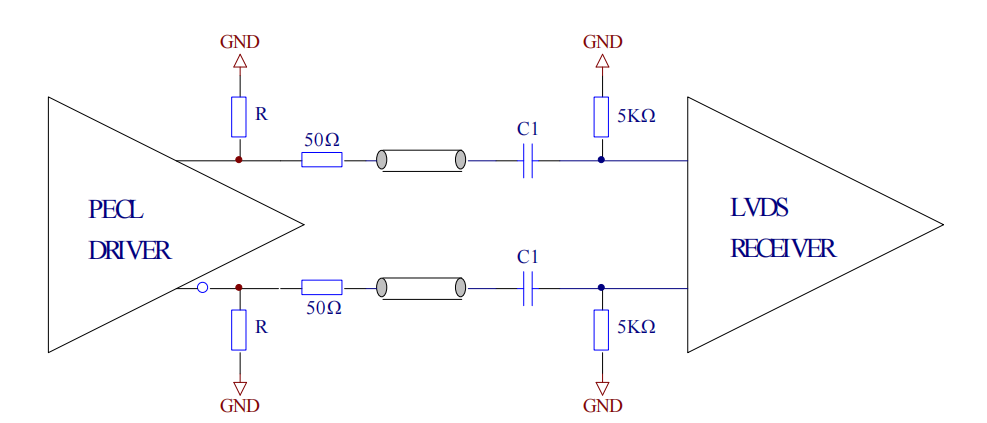

LVPECL到LVDS的交流耦合结构如图4所示,LVPECL的输出端到地需加直流偏置电阻R(142Q~200Q),同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS的输入端到地需加5.0kQ电阻,以提供共模偏置。

图4. LVPECL与LVDS之间的交流耦合

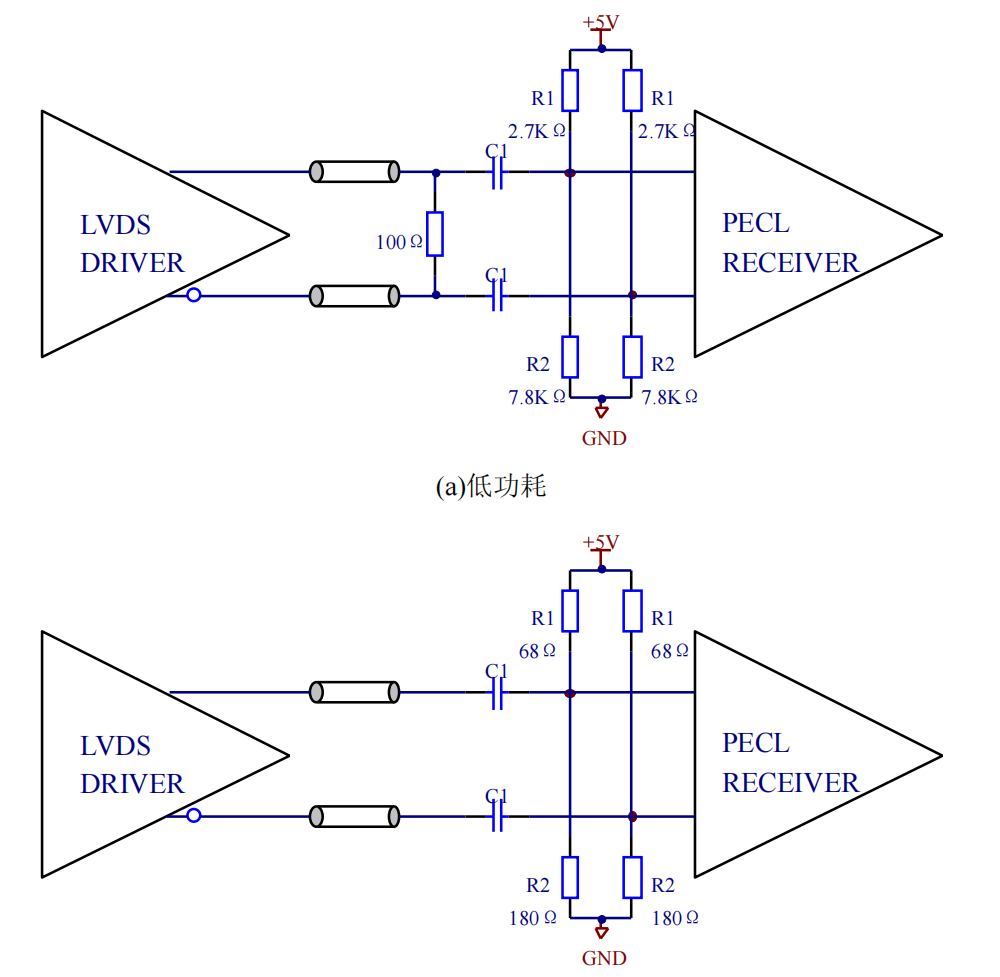

LVDS到LVPECL的交流耦合结构较为简单,如图5所示,如果芯片内部加了偏置,则可去掉R1和R2。

图5. LVDS 与LVPECL 之间的交流耦合

2. PECL 与LVDS 的互连

PECL 到LVDS 的交流耦合结构如图6 所示,PECL 的输出端到地需加直流偏置电阻R(270Ω~350Ω),

同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS 的输入端到地需加5.0kΩ电阻,以提供共模

偏置。

图6. PECL 与LVDS 之间的交流耦合

LVDS 到PECL 的交流耦合结构较为简单,如图7 所示,如果芯片内部加了偏置,则可去掉R1 和R2。

(b)普通接法

图7. LVDS 与PECL 之间的交流耦合

| 参数 | Rl=R3 | R2=R4 | R5=R6 | 备注 |

| VCC=+3.3V | 2.7K Ω | 4.7K Ω | 140Ω~200Ω |

接上电阻 R=100Ω为 低功耗电路 |

| VCC=+5V | 2.7K Ω | 7.8K Ω | 270Ω~350Ω |

(a) 低功耗匹配电路

(b)普通匹配电路

图8. 光模块与协议转换IC 间PECL/LVPECL/LVDS 电平的交流耦合

光特通信专注于光模块研发生产,支持OEM/ODM定制,集研发、销售与制造为一体的生产企业!

参考资料:

Interfacing Between LVPECL, CML, and LVDS Levels---Texas Instruments

审核编辑 黄宇

-

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析2025-08-08 1713

-

ADS5404可以使用LVDS或LVPECL的时钟源头吗?2024-12-13 383

-

LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?2024-11-11 544

-

如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计?2023-12-06 708

-

AD9680时钟为差分LVPECL的话,交流耦合如何接入呢?2023-12-01 726

-

LVPECL与LVPECL之间是如何进行连接的?LVPECL到CML的连接?2023-08-28 5598

-

浅谈FPGA输入时钟要求 LVDS与LVPECL讲解2023-08-21 15291

-

LVDS和CML与LVPECL的不同逻辑电平之间的互连教程2021-01-07 2439

-

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连2020-12-20 41579

-

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换2018-09-13 15342

-

用MLF1608C150MT000电容实现LVDS连接交流耦合的设计分析2011-07-05 2868

-

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、2009-12-19 1975

全部0条评论

快来发表一下你的评论吧 !