PD65W氮化镓快充电源应用方案

描述

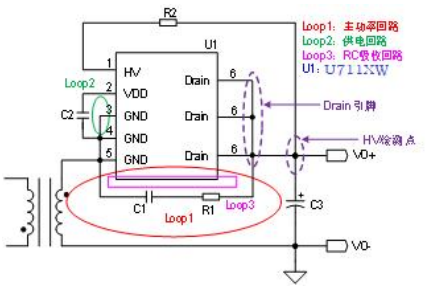

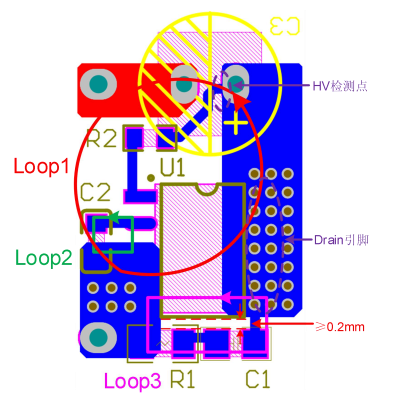

设计大电流,高开关频率同步降压电路时,要想设计一个稳定可靠的系统,PCB布局显得尤为重要。同步整流ic U7110W设计同步整流电路时建议参考下图的内容。图为PCB布局设计参考,包含U7110W、变压器副边引脚和输出滤波电容等。

1. 副边主功率回路Loop1的面积尽可能小。

2. VDD电容推荐使用1μF的贴片陶瓷电容,尽量紧靠IC,Loop2的面积尽可能小。

3. HV到Drain建议串联30~200Ω的电阻,推荐典型值100Ω。HV检测点位置对CCM应力有影响,HV检测点离Drain引脚越远,CCM应力越小。如图所示的High Side配置中,建议HV通过R2电阻连接到输出电容的正端。

4. R1和C1构成同步整流开关的RC吸收电路,RC吸收回路Loop3的面积可能小。

5. Drain引脚的PCB散热面积尽可能大。

6. 如图所示,ASOP-6的封装框架与Drain引脚电位相同,芯片切筋后,框架金属有少量暴露,考虑到绝缘要求,外围元器件应与IC本体保持0.2mm以上的绝缘距离。

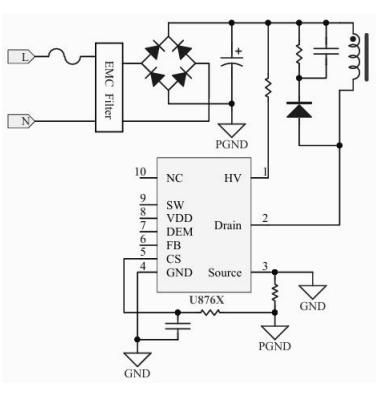

同步整流ic U7110W搭配氮化镓快充芯片U8765,可以做65W快充方案。U8765主要特性如下:

1. 集成高压 E-GaN

2. 集成高压启动功能

3. 超低启动和工作电流,待机功耗 <30mW

4. 谷底锁定模式, 最高工作频率两档可调(220kHz,130kHz)

5. 集成 EMI 优化技术

6. 驱动电流分档配置

7. 集成 Boost 供电电路

8. 集成完备的保护功能:VDD过压/欠压保护(VDD OVP/UVLO)、输出过压保护(OVP)、输入欠压保护(BOP)、片内过热保护(OTP)、逐周期电流限制(OCP)、异常过流保护(AOCP)、短路保护(SCP)、过载保护(OLP)、过流保护(SOCP)、前沿消隐(LEB)、CS管脚开路保护

9. 封装类型 ESOP-10W

氮化镓快充芯片U8765采用峰值电流控制模式,可以自适应的工作在QR和降频工作模式,从而实现全负载功率范围内的效率优化。在满载和重载工况下,系统工作在QR工作模式,可以大幅降低系统的开关损耗。芯片根据FB电压值调节谷底个数,同时为了避免系统在临界负载处的FB电压波动导致谷底数跳变,产生噪音,U8765采用了谷底锁定工作模式在负载一定的情况下,导通谷底数稳定,系统无噪音。

高效快充方案的核心是要选对同步整流ic与快充芯片。深圳银联宝科技推出的多套氮化镓快充芯片+同步整流ic+协议ic电源方案,通过内置同步整流功能或外部组合,实现电源应用的高转换效率、低功耗和小型化!

-

PD 40W氮化镓快充电源方案:U8725AHE+U7110W2025-06-26 1778

-

拆解报告:橙果65W 2C1A氮化镓充电器2023-06-16 1883

-

65W氮化镓(1A2C) PD快充电源方案2023-04-21 4182

-

65W氮化镓(GaN)充电头PD快充方案2023-04-20 3018

-

爱美雅推出M版多协议兼容65W氮化镓快充头方案2023-04-11 1410

-

65W-1A2C接口氮化镓(GaN)PD快充电源方案2023-04-07 1808

-

GaN/氮化镓65W(1A2C)PD快充电源方案2023-03-01 2624

-

FM2842替代料65W氮化镓pd充电器方案PN82132022-06-13 960

-

氮化镓充电器电源方案的特点是怎样的2022-06-02 3981

-

NCP1342国产化65W氮化镓pd充电器方案-PN82132022-05-17 939

-

PN8213 65w氮化镓充电器芯片应用方案2022-05-09 4115

-

展嵘电子助力布局氮化镓适配器方案携手智融SW351X次级协议45W69W87W成熟方案保驾护航2021-04-16 1859

-

拆解报告:SlimQ 65W氮化镓USB PD快充充电器1A1C2021-01-06 5319

-

氮化镓GaN 来到我们身边竟如此的快2020-03-18 2916

全部0条评论

快来发表一下你的评论吧 !