LMKDB1108EVM评估模块技术解析与应用指南

描述

Texas Instruments LMKDB1108EVM评估模块提供了一个设置来评估LMKDB1108 LP-HCSL时钟缓冲器性能,支持PCle Gen 1至Gen 6。该模块还允许对LMKDB1108时钟缓冲区进行合规性测试和系统原型设计。LMKDB1108EVM 模块 可以使用带有TICS pro软件GUI的PC通过板载USB微控制器接口进行配置。该模块具有集成LDO,可通过3.3V的工作电源电压实现出色的电源噪声抑制。LMKDB1108EVM模块盒包含LMKDB1108EVM板 (DC255A) 和3 英尺 mini-USB 电缆 (MPN 3021003-03)。该模块用于服务器主板、硬件加速器和NIC/SmartNIC。

数据手册:*附件:Texas Instruments LMKDB1108EVM 驱动评估模块用户指南.pdf

特性

- 支持PCIe Gen 1至Gen 6和DB2000QL-compliant缓冲区

- 板载输入/输出扩展器,用于通过引脚控制来启用/禁用输出

- 外部和USB电源选项

- 通过TICS pro软件图形用户界面 (GUI) 进行编程

输入接口

一、核心特性

- PCIe全代际支持:兼容Gen1至Gen6标准

- 灵活供电配置:支持USB(默认)和外部1.8V/3.3V双电源输入

- 多重控制接口:提供SMBus、3/4线SBI和独立OE#引脚控制

- 先进监测功能:集成信号丢失检测(LOS)和自动输出禁用(AOD)

- 低抖动性能:典型相位噪声-150dBc/Hz@1MHz偏移(156.25MHz时钟)

二、硬件架构解析

1. 电源管理系统

评估板提供两种供电模式:

- USB模式(默认) :

- 通过板载LDO(U4)提供3.3V电源

- 典型功耗:85mA@3.3V(全输出使能)

- 外部电源模式:

- 支持1.8V±10%和3.3V±10%双电压输入

- 通过J8 SMA接口接入

- 切换方法:将JP12跳线从2-3改为1-2位置

关键电源参数:

- VDDA(模拟电源):1.8V±10%

- VDD(核心电源):3.3V±10%

- 电源序列要求:无严格上电顺序限制

2. 时钟通道设计

输入接口配置:

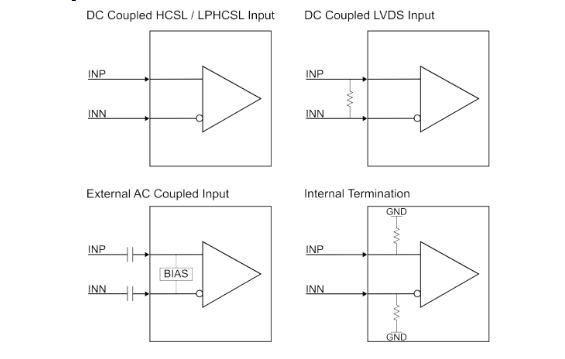

- 支持4种输入模式(通过TICS Pro GUI选择):

- DC耦合HCSL/LP-HCSL(默认)

- DC耦合LVDS(需安装R102 100Ω电阻)

- 外部AC耦合(需替换R101/R103为0.1μF电容)

- 内部50Ω对地端接

输出特性:

- 8路差分LP-HCSL输出(CLK0-7_P/N)

- 默认激活CLK0和CLK4输出通道

- 输出阻抗:85Ω差分(典型值)

- 可编程压摆率控制(16级调节)

三、评估系统搭建

1. 硬件连接步骤

- 电源配置:

- USB模式:连接J3 Mini-USB接口

- 外部模式:通过J8接入1.8V/3.3V电源

- 时钟输入:

- 连接100MHz参考时钟至J10/J11(CLKIN_P/N)

- 输入电平要求:400mVpp(典型)

- 输出监测:

- 使用SMA电缆连接J13-J28至测试设备

- 注意:禁止直接连接RF设备(DC耦合限制)

2. 软件配置流程

TICS Pro操作指南:

- 安装TICS Pro软件(版本需≥2.0.12)

- 选择设备型号:Clock Distribution → LMKDB1108

- USB通信验证:

- 点击"Identify"按钮

- 观察D4 LED应呈现0.5Hz闪烁

- 关键参数设置:

- 输入接口类型(Input Interface Type)

- 自动输出禁用(AOD)使能

- 输出压摆率(SLEWRATE_OPT)

寄存器配置技巧:

- 使用"Read All Regs"获取当前配置

- "Export Register"功能保存配置模板

- 通过SMBus Address Decode(表3-7)设置器件地址

四、典型测试结果

1. 相位噪声性能

在156.25MHz输入时钟条件下:

- 10kHz偏移:-110dBc/Hz(典型)

- 1MHz偏移:-150dBc/Hz(典型)

- 集成抖动(12kHz-20MHz):80fs RMS

2. 电源抑制比(PSRR)

- VDDA:-60dB@100kHz

- VDD:-55dB@1MHz

五、应用设计建议

1. PCB布局要点

- 电源层处理:

- 使用星型拓扑连接去耦电容

- VDDA与VDD采用独立铺铜区域

- 信号完整性:

- 保持差分对长度匹配(±50mil公差)

- 避免90°拐角,使用弧形走线

- 热管理:

- 在器件底部布置散热过孔阵列

- 推荐四层板设计(顶层-地层-电源层-底层)

2. 系统集成注意事项

- SMBus上拉电阻:2.2kΩ(3.3V系统)

- 时钟走线阻抗控制:100Ω差分

- 电源滤波建议:

- VDDA:10μF+0.1μF陶瓷电容

- VDD:22μF+1μF陶瓷电容

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPS55065EVM评估模块使用指南:设计与应用全解析2026-04-25 227

-

深入解析TPS43331EVM评估模块:设计与应用指南2026-04-24 302

-

TPS23754EVM - 383评估模块:技术解析与应用指南2026-04-23 107

-

INA-DDF-EVM评估模块技术解析与应用指南2025-09-07 1300

-

TPSM33625EVM评估模块技术解析与应用指南2025-09-03 1099

-

LMKDB1120EVM评估模块技术解析与应用指南2025-08-08 1175

-

Texas Instruments LMKDB1204EVM 评估模块(EVM)数据手册2025-07-29 737

-

Texas Instruments LMKDB1104EVM评估模块数据手册2025-07-28 864

-

Texas Instruments LMKDB1x02EVM 评估模块数据手册2025-07-23 811

-

Texas Instruments TRF1108EVM射频放大器评估模块数据手册2025-07-06 997

-

LMH5401EVM评估模块(EVM)用户指南2025-01-02 557

-

LMKDB1108评估模块2024-11-22 333

全部0条评论

快来发表一下你的评论吧 !