使用示波器进行验证和调试

模拟技术

描述

验证(Verification),就是测试设计是否和它对应的各种标准(行业标准或者自定义标准)相符,以及有多少冗余量。验证和调试,是示波器的主要用途。

在使用示波器进行调试时,我们关心的主要指标是:

波形捕获率——决定仪器能够多快发现故障

触发系统——决定仪器能够多精确地定位故障

分析能力——决定仪器能够从波形里提取出多少有用信息。

而在使用示波器进行验证时,我们更关心的指标是:信号保真度——决定采集的样点是否能够真实反映信号特性;采样率和内存深度——决定单次捕获可以以多快的速度以及抓取多少样点供验证测试;分析工具——决定深入分析的程度和准确性。

信号保真度是一个比较复杂的问题,涵盖了示波器的带宽、采样率、内插、抖动噪底、本底噪声、时间测量精度、探头系统等多个方面。业界对此的讨论很多,也有很多相关文章,所以本文不再做详细分析,只强调示波器的频率响应对验证的影响。

频率响应,在示波器指标上反映为带宽和上升时间。带宽表征的是示波器的稳态响应能力,而上升时间是瞬态相应。经验上,带宽和上升时间(10~90%)的乘积是一个常数,这个常数和示波器的放大器模型有关。如高斯响应的放大器模型,这个常数是0.35;而高性能的示波器放大器模型比较复杂,该常数一会在0.4~0.55之间。当然,从用户的角度看,这个常数应该越小越好:常数越小,则表示相同的带宽(稳态响应)下,该示波器的上升时间更快,也就是说瞬态响应更好;而上升时间一样的情况下,乘积小的示波器需要的带宽会相对低一些——而对示波器,带宽和价格是正比的,也就是说乘积小的示波器性价比更高。

我们验证测试对象一般都是脉冲(非正弦)信号,如通信信号、串行总线信号、高速脉冲信号、调制信号等等,所以示波器的瞬态响应相比起来更加重要。泰克DPO示波器在相同带宽下,能提供最快的上升时间,对于瞬态信号的测试非常有帮助。

另外一方面,高带宽示波器的不同设计结构,也会影响到验证测试的正确性、精度和速度:

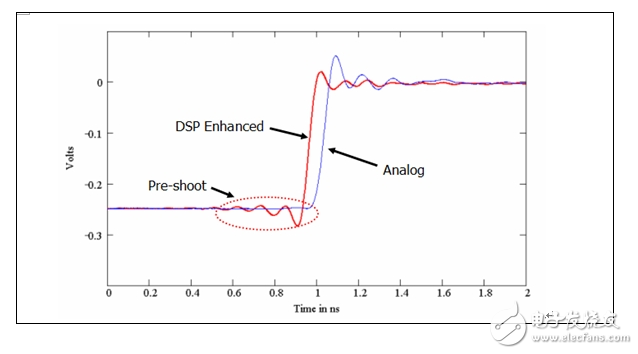

近几年示波器带宽不断高速提升,如何在提升带宽的同时,保证带内幅度响应的平坦和相位响应的线性,成了一个重要的问题。有经验的工程师都知道,要完全从硬件入手,是不可能得到理想的平坦幅度响应和线性相位响应的。所以在高性能示波器的放大器技术中,各大示波器生产商都在使用软件提升带宽和优化响应的DSP技术。DSP技术的使用,确实能得到比较理想的幅度和相位响应,但是它并不是有利无害的。下图是示波器对阶跃信号的响应,蓝色为完全的模拟响应,而红色是DSP处理后的响应。

DSP 提升、修正幅度和相位响应后,示波器可以更加精确地测量上升时间、眼图冗余等指标,有利于对数字通信信号、计算机总线信号等的验证测试。但是从红色的波形可以看到:虚线框部分,我们叫做“预过冲”,是一种不存在于现实信号中“假波形”,是由DSP处理产生出来的失真——对于阶跃信号来说,没有理由当上升能量还没有产生时,波形就开始振荡。所以当使用示波器测量高速脉冲、激光脉冲或类似信号时,DSP的处理就不再是测试人员期望的了——失真的波形错误指示了各个时间点的物理行为。

当然,DSP还有其它一些问题,如过驱动的信号的错误显示、较低的数据吞吐速度、DSP之前的原始数据无法导出等。所以当用户需要观测过驱动信号(如脉冲顶端的过冲细节)、需要使用示波器采集的原始数据做自定义分析(如激光脉冲测量)或者需要较高的处理速度时,都要求示波器不使用DSP功能。

泰克在所有2.5GHz带宽以上的DPO中都使用了DSP的频响修正和通道匹配功能,DPO72004还有DSP的带宽提升功能。但是泰克公司也深知DSP功能的利弊,所以在其它公司“悄悄”使用DSP功能时,泰克唯一让用户有了“知情权”和“控制权”,即用户可以知道示波器是否正在使用DSP功能,同时还可以根据需要打开或者关闭DSP提升功能。这样,如进行需要示波器原始采集数据的脉冲测试,用户可以选择关闭DSP功能;而进行串行信号一致性测试时,泰克建议可以打开DSP功能。

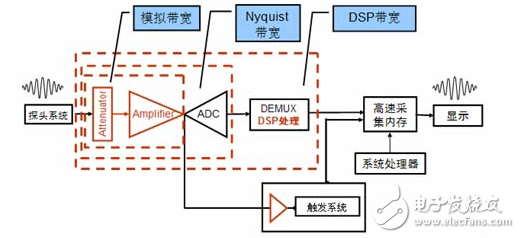

除了应用上需要注意以上这些事项以外,DSP功能还有一些要求。从上图我们可以看到,DSP要求必须满足奈奎斯特采样率实时采样。有一些厂家的示波器当采样率不满足奈奎斯特带宽时,会有难以预料的波形幅度失真,大多来自于这个原因。

同时,高性能示波器一般都是4通道。但是要在四个通道上同时实现标定带宽,还需要采样率的支持。业界一般公认2.5倍于带宽的采样率是保证带宽的最低要求。这样,如果使用8GHz以上的示波器做信号验证(一般都是单次采集),泰克的DPO可以同时在4条通道同时提供全带宽性能(每通道50G的采样率可以有效保证最高20GHz的带宽),而采用共享放大器和ADC结构的示波器最多只能在两条通道上达到全带宽指标,有的甚至仅仅能保证一条通道的性能。

存储深度方面,很多验证测试需要足够的数据。如目前在高速串行信号的抖动和眼图测试过程中都要求一次捕获大量的数据,以进行精确的抖动测量和预估,同时保证低误码率。以避免捕获少量数据进行分析的结果的偶然性和不确定性。类如HDMI测试规范(CTS1.2 a Page 15)要求捕获1百万个比特数据进行眼图分析,则需要示波器两通道在10Gs/S的采样率下使用16M的存储深度。FBD Sigtest(Release notes Page6)推荐捕获1百万个比特数据进行眼图分析.PCIE 2.0的规范(Page239)规定强制要求捕获1Mlillion数据进行眼图抖动分析。则需要示波器单通道在40Gs/S的采样率下使用8M的存储深度。

另一个例子:为了减少EMI的串扰和辐射,在大多数高速串行信号中均使用了加入了扩频时钟(spread spectrum clock),它可以使串行信号的速率在一个适当的范围内进行漂移,从而使其频谱在一个较宽的范围内扩散,尖峰值显著降低,可以有效减少EMI问题。例如 FBD规范(Page15)明确规定需要支持频率很低的30-33K的频率的扩频时钟,其他如PCIE,SATAI,SATAII同样要支持此功能。为了验证Motherboard上的诸如此类的串行信号是否支持扩频时钟,而且确认其调制频率是否在30-33K之间。就必须一次捕获足够长时间的信号进行频率抖动分析。一次抓取的采样点数可以用下面的公式计算:每个扩频周期约位1/33k=30uS,由于是捕获高速串行信号,采样率至少为40Gs/S,即采样间隔为25pS,则捕获单个周期的总采样点数为30uS/25ps=1.2M,为了实现准确的扩频时钟的测量,一般建议捕获10个以上的扩频时钟周期, 所以总的采样点数为1.2M*10=12M.需要强调的是,此12M的存储深度必须使用在40Gs/s或更高的采样率下才有意义。

有些示波器设计时采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SOC芯片实现,由于有太多功能在一个芯片内部实现,导致片内高速内存容量的限制(在40GS/s下不大于2M),而且无法对内存扩展升级。为了弥补这种设计结构的缺陷,这类示波器会采用在芯片外部添加低速存储器弥补片内高速内存的限制,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,样点间隔500ps,无法在信号边沿采集足够样点,甚至出现会出现混叠,所以它无法提供高精度时间测试结果。泰克DPO可以提供每通道200M的存储深度,且无任何使用限制,是业界最高的能力。这一能力让使用DPO进行验证测试的工程师在工作里游刃有余。

在分析工具方面,工程师一般会按优先顺序考虑以下三个方面:第一是准,即分析工具能够精确地得出结果;第二是全,即分析工具能够尽可能多地完成要求的测试项;第三是快,即在保证“准”和“全”的基础上,分析工具还能迅速、自动地工作,最好能够生成标准的测试报告。

“ 准”是第一要求,工业的标准文档一般会推荐一些解决方案,这些解决方案通常是标准工作组正在使用的方案,当然这类方案可以满足“准”的要求。还有一些所谓的“执行标准”,就是在标准工作组推荐的多个方案中,主要厂商或者行业领导者选择的方案。这类方案有最多的采用者,当然使用这类方案,可以得到业界最主要厂商的认同,所遇到的兼容性问题也最小。

建立在“准”基础上的“全”也是一个重要条件。一种分析工具,如果能够提供尽可能多的测试项,最好还能用户自定义测试点,那么将会为工程师带来很大的便利。行业规范以及业界认可的设备对验证测试非常重要,不同厂家的设备虽然都对外宣称可以支持某一项标准的一致性测试,但由于硬件平台以及软件实现方式的不同,使测试项目的完整性,覆盖率以及测试结果存在很大差异。这种测试结果的差异会大大降低客户对测试报告的认可程度,对于OEM/ODM厂商这一点尤其需要重视。

“快”的要求,必须要建立在“准”和“全”的基础上——高效必须以质量为前提。

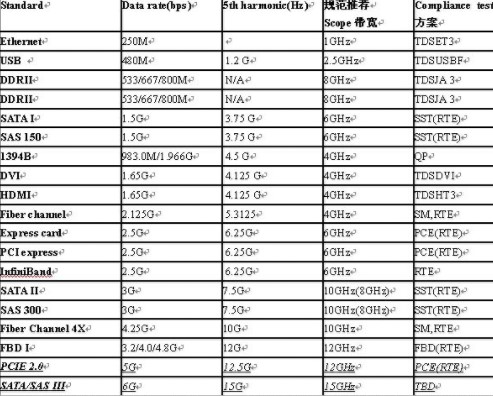

以高速计算机总线测试为例,下表列出泰克的解决放案,其中大部分方案都是标准规范所推荐的。值得注意的是,唯有泰克的DPO70000系列实时数字荧光示波器可以涵盖所有的标准一致性测试要求的带宽:

另外,在通信规范的验证上,泰克的Pinpoint触发系统提供通信相关触发,它使用硬件时钟恢复电路恢复高速串行数据的嵌入式时钟,从而可以进行等效眼图测试。泰克示波器也是业界唯一可以实现标准等效眼图测试的实时示波器。

-

使用MXO示波器的快速FFT功能进行EMI调试2024-05-25 1452

-

使用 MSO 验证信号质量时典型的调试方法2023-08-07 1459

-

如何使用示波器调试电源固件2021-09-29 824

-

怎样调试混合信号示波器2021-08-23 2952

-

如何使用示波器对嵌入式系统进行调试2020-11-18 1249

-

BUCK电路设计的电感参数、示波器测量波形调试分析2019-04-23 12364

-

如何使用Xilinx AXI进行验证和调试2018-11-20 4660

-

使用数字荧光示波器检测电路故障并进行调试2018-10-12 5952

-

怎样使用 MSO 和 MDO 系列示波器的基本逻辑分析仪功能迅速验证和调试数字电路2017-09-16 1755

-

示波器制作调试2016-12-15 634

-

如何通过混合信号示波器进行数字电路调试2015-05-27 1794

-

用高带宽混合信号示波器进行DDR验证和调试的技巧2010-03-02 929

-

超越边沿触发:如何使用示波器触发进行调试2009-11-09 477

-

怎样使用示波器触发进行调试2009-10-10 4884

全部0条评论

快来发表一下你的评论吧 !