新转换器架构在50kHz都不用磁芯,不是50MHz

电子说

描述

Ćuk博士设计的Ćuk DC-DC转换器以其输入和输出纹波电流低而闻名,可作为升降压转换器使用。本设计实例示出了Ćuk博士的一个新转换器架构,这是一种谐振转换器,即便在相当低的频率(例如50kHz)下运行,仍然可以通过极少量的电感与大电容产生谐振。Ćuk博士倾向于保持低开关频率,但提高频率却能以较小的LC值获得较快的瞬态响应。

很多工程师都知道Slobodan Ćuk (发音类似chook) 博士,他是Ćuk DC-DC转换器架构的设计者,这种转换器以输入和输出纹波电流低而闻名,也可作为降压-升压器使用。

所以最近当我注意到Ćuk博士又发布了一个新的转换器架构时,我的兴趣马上就被调起来了。

我一直与这位和善的博士保持着联系,但是不太清楚他的新设计情况。原型好像已经建成,不过细节还没有透露。

该设计被认为是一种谐振转换器,即便在相当低的频率(例如50kHz)下运行,仍然可以通过极少量的电感(甚至可以只是PCB走线)与大电容谐振。

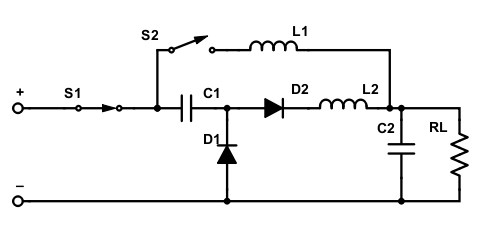

图1:Ćuk博士提出的谐振降压转换器兼电荷泵。

我发现现有的电路描述有点难以理解(这无疑说明我的能力还不够),下面只是我对该设计的一些粗浅领会。

如果忽略电感器(用短路替换),它基本上就是一个电荷泵,以2:1的比例运行。

设想电路或多或少处于平衡状态,开关如图1所示:输入电压将在C1和C2之间被分压。当开关翻转时,C1将与C2并联(通过S2和D1),传输一些电量以补充C2。

通过使用电感器,每个电荷泵(CP)相位是谐振周期的一半。这样可以减少标准CP设计中出现的电流尖峰,并且可以在不损失效率的情况下实现输出电压的占空比控制(因为电感会降低电荷传输速率)。我想控制电路也必须采取突发模式,以便在低负载时保持输出电压不上升,因为在电荷转移阶段,L2的能量将不断转移到电容器中。

D1和D2可以是实际的二极管,如果不介意损耗的话,但在大多数情况下应该是同步开关。Ćuk博士指出,在这种情况下替代D2的FET可能需要在开路时阻断电流,就像二极管一样,但是其源极代替D2阴极的N沟道FET(如Ćuk博士的一个电路原理图中所示的)将使一个体二极管指向错误的方向。背靠背FET可能是必要的,但是要有正确的控制电路,我认为源可能在左边。

通过这个设计,我相信我的分析能力得到了提高,但如果你认为我的分析哪里不对,请分享你对该电路的理解和看法。这是对我需要提高仿真技能的提醒吗?我们拭目以待。

Ćuk博士似乎偏爱保持低开关频率,但我认为没有理由不提高频率,这样可以较小的LC值获得较快的瞬态响应(但这样会增加开关损耗)。具体有什么益处呢?让我们看一些例子:

50kHz: 1000µF, 10nH 500kHz: 22µF, 4.6nH 2MHz: 6.8µF, 1nH

有时,平方根运算真是有用的。

那么,你对这个设计的潜在价值有何看法?

-

带宽为50MHZ的宽带放大器2010-04-30 2891

-

使用CR90CR285进行Cameralink的数据转换,在放大器之后,ADC之前的模拟信号上测量到50MHz的噪声,怎么解决?2024-12-04 0

-

为什么8902A调谐射频电平性能测试采用30MHz测试频率而不是50MHz?2019-09-30 0

-

50MHz生成400Hz资料下载2021-07-22 0

-

正激转换器磁芯复位技术的原理2021-12-13 0

-

有没有50MHz的PWM输出呢2022-12-01 0

-

50khz频率光发射电路2008-12-21 968

-

50Khz调频光接收电路图2008-12-23 1141

-

50MHZ光电检波电路图2008-12-24 1398

-

与50kHz调频发射机配用的接收机电路图2009-04-01 1579

-

50kHz振荡器电路图2009-04-15 1550

-

步进为50khz的100-200Mhz直接编程频率合成器2009-09-05 1187

-

50MHZ射频(RF)电桥2009-09-23 1430

-

50MHZ射频电桥原理图2011-09-02 6773

-

50MHZ,50.000MHZ,50.000000MHZ哪个精度高?2022-05-19 1223

全部0条评论

快来发表一下你的评论吧 !