一种基于CPLD的可编程频率电压变换电路介绍

可编程逻辑

描述

摘要:文章介绍了一种可编程的频率电压变换电路(F/V),将频率信号通过复杂可编程逻辑器件(CPLD)变换为与频率成正比的脉宽信号,脉宽信号控制模拟开关对基准电压信号进行斩波,斩波信号经低通滤波后输出直流电压信号。

0 前言

电气自动化和过程自动化及自动检测领域常常用到频率电压变换器F/V,需要将频率信号转换为电压信号。F/V变换器的实现方法一般有3种:一是基于专用F/V转换芯片(如LM331),二是基于模拟电路,三是基于微处理器和D/A转换器。前两种F/V变换器的共同缺点是量程单一,频率变换范围不能在线改变或不能方便地改变。第三种F/V变换器需要较高速度的微处理器和高分辨率D/A转换器,成本较高。本文介绍一种基于CPLD的可编程F/V变换电路,该电路简单、频率变换范围可任意连续设置、精度高,具有较好的实用价值。

1 电路的基本原理

F/V变换电路的基本结构,频率信号经K分频电路转换为占空比为50%的方波信号;方波信号经频率/脉宽变换电路转换为脉宽与频率成正比的脉冲调宽信号;脉冲调宽信号的高电平控制模拟开关与电压基准接通,低电平控制模拟开关与信号地接通,模拟开关的输出经低通滤波器将脉冲宽度信号转换为直流电压信号。

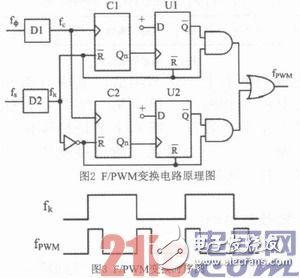

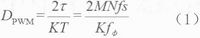

图2为F/PWM变换电路的原理图,fs为被变换频率信号,f0为参考时钟信号,D1为M分频器,D2为K分频器,C1、C2为n位二进制计数器,U1、U2为上升沿触发的D触发器。当K分频器输出fk为0时,计数C1器清零,U1触发器的输出置1,当fk为1时,计数器C1在M分频器的输出fc的作用下增量计数。当计数器C1计数由N-1变为N时,其计数器C1的Qn脚输出由0变为1,触发D触发器1的输出为逻辑0。当K分频器输出fk为1时,计数C2器清零,U2触发器的输出置1,当fk为0时,计数器C2在M分频器的输出fc的作用下增量计数。当计数器C2输出由N-1变为N时,其计数器C2的Q脚输出由0变为1,触发D触发器U2的输出为逻辑0。两组计数一触发电路逻辑相反,经过逻辑组合输出得到脉宽与频率fk成正比的输出波形fPWM。频率脉宽变换时序图如图3所示。

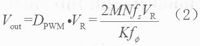

设被变换频率信号fs的周期为T,则K分频信号fk的周期为KT,脉宽调制信号的宽度为τ,设计数器对fc的计数为N,则τ=MN/f0,脉宽调制信号fPWM的占空比DPWM与fs成正比。

由于DPWM≤1,所以被变换信号的频率上限fsmax为Kf0/2MN,显然,通过改变分频数M或K或计数值N,均可改变被变换的频率上限。

图4为将PWM信号变换为直流电压信号的原理图。PWM信号的高电平控制模拟开关与电压基准VR接通,低电平控制模拟开关与信号地接通,模拟开关的输出经低通滤波器将脉冲宽度信号转换为直流电压信号Vout。

2 实验结果

采用Xilinx公司的CPLD芯片XC9572来实现图2描述的逻辑功能,将频率信号变换成脉冲宽度信号。CPLD输出的与频率信号成正比的脉冲宽度信号连到模拟开关ADG408芯片的1脚,作为通道选择信号。基准电压信号VR为5V且连到ADG408的5脚,ADG408的8脚输出的电压信号经低通滤波电路滤波,输出与频率信号成正比的直流电压信号Vout。参考时钟f0的频率为80MHz,CPLD内部D1和D2为2分频器,C1、C2为12位二进制计数器,基准电压信号VR为5V,根据公式fsmax=Kf0/2MN,可变换的最大频率为19.531kHz。不同参考时钟分频数M对应的频率信号变换范围如表1所示。不同计数器计数值N对应的频率变换信号范围如表2所示。

3 结论

本文介绍了一种基于CPLD的可编程频率电压变换电路,该电路先将频率信号转换成PWM信号,再将PWM信号转换成对应的直流电压信号。由于使用了可编程的逻辑器件,本电路简单、频率变换范围可任意连续设置、精度高,具有较好的实用价值。

-

基于复杂可编程逻辑器件(CPLD)的120MHZ高速A/D采集卡的设计2011-03-05 2110

-

单片可编程恒流源是一种新的基本构件2019-09-11 1840

-

如何设计一种基于CPLD的可编程高精度CCD信号发生器?2021-04-13 1358

-

求一种可利用复杂可编程逻辑器件设计技术实现的专用键盘接口芯片方案2021-04-15 1090

-

求大佬分享一种简单易行的可编程振荡器构建方法2021-06-17 1344

-

PLD可编程逻辑器件2021-07-22 2327

-

基于复杂可编程逻辑器件(CPLD)的120MHZ高速AD采集2010-01-17 855

-

采用FPGA的可编程电压源系统原理及设计2010-03-22 2844

-

可编程微电流放大电路的设计2011-04-22 2747

-

基于CPLD的数字可编程延迟单元的设计2011-09-20 1227

-

电压一频率、频率一电压变换电路介绍2016-05-11 963

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 920

-

采用5管单元的SRAM结构实现CPLD可编程电路的设计2020-04-25 2588

-

可编程逻辑阵列fpga和cpld说明2021-03-30 1234

-

一种简单易行的可编程振荡器构建方法2024-01-15 892

全部0条评论

快来发表一下你的评论吧 !