FPGA学习系列:12. 边沿检测设计

描述

设计背景:

在我们工程设计中,有时会需要到上升沿和下降沿这么一个说法,通过上升沿和下降沿来驱动一个电路,那么学习边沿检测就非常的重要了。

设计原理:

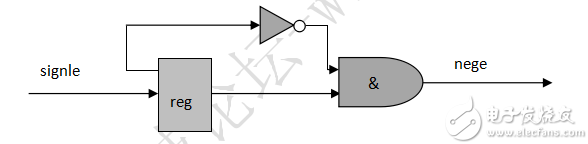

在学习边沿检测前我们先学习一下下面的电路,这样方便我们学习,边沿检测。

这个电路的意思就是,输入一个信号后我们经过一个寄存器,然后把这个寄存器的输出,和下次输出的值取反后相与,那么我们就可以这么想,如果一个高平的值经过这个寄存器后延迟一个上升沿后输出也为高电平,那么当输出的时候会有一个新的电平值,也就是一个电平的到来,然后通过低电平的值取反后和寄存器输出的高电平值得与得到一个高电平的脉冲值,然后对低电平转化为高电平也是一样的道理,这样我们就可以得到时钟上升沿和下降沿的高脉冲,这样就得到了我们设计的目的。

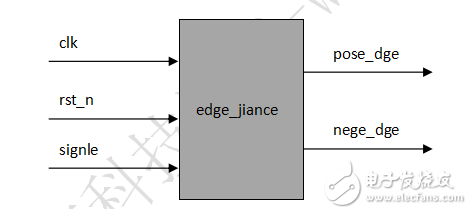

设计架构图:

设计代码:

设计模块

0 module edge_jiance(clk,rst_n,signle,nege_dge,pose_dge);

1

2 input clk;

3 input rst_n;

4 input signle; //输入信号

5

6 output nege_dge; //输出下降沿的脉冲

7 output pose_dge; //输出上升沿的脉冲

8

9 reg [1:0] signle_s;

10 always @ (posedge clk or negedge rst_n)

11 if(!rst_n)

12 begin

13 signle_s <= 2'b11;

14 end

15 else

16 begin

17 signle_s[0] <= signle; //把输入信号给一个寄存器

18 signle_s[1] <= signle_s[0];

19 end

20

21 assign pose_dge = signle_s[0] && ~signle_s[1]; //取反相与得到上 升沿的高脉冲

22 assign nege_dge = ~signle_s[0] && signle_s[1]; //取反相与得到下 降沿的高脉冲

23 endmodule

测试模块

0 `timescale 1ns/1ps

1

2 module edge_tb();

3

4 reg clk;

5 reg rst_n;

6 reg signle;

7

8 wire nege_dge;

9 wire pose_dge;

10

11 initial begin

12 clk = 1'b1;

13 rst_n = 1'b0;

14 signle <= 1'b1; //复位赋值

15

16 #100.1 rst_n = 1'b1;

17

18 #36 signle <= 1'b1; //模拟下降沿

19 #36 signle <= 1'b0;

20

21 #100

22 #36 signle <= 1'b0; //模拟上升沿

23 #36 signle <= 1'b1;

24

25 #100

26 $stop;

27 end

28

29 always #10 clk = ~clk; //产生晶振时钟

30

31 edge_jiance edge_dut( //模块例化

32 .clk(clk),

33 .rst_n(rst_n),

34 .signle(signle),

35 .nege_dge(nege_dge),

36 .pose_dge(pose_dge)

37 );

38 endmodule

仿真图:

我们模拟的上升沿和下降沿在仿真中可以清楚的看到,然后我们通过边沿检测电路,可以得出我们一个高电平的上升沿,和一个低电平的下降沿。

- 相关推荐

- 热点推荐

- FPGA

-

FPGA设计经验之边沿检测2012-03-01 5370

-

FPGA设计中的边沿检测问题2012-02-01 1065

-

FPGA设计经验:边沿检测2017-08-16 2163

-

fpga应用篇(二):边沿检测2017-04-06 3946

-

至芯昭哥带你学FPGA之FPGA_100天之旅_边沿检测2017-08-17 3592

-

FPGA_100天之旅_边沿检测2017-09-28 2161

-

关于FPGA进行外部边沿检测,检测不准确问题?2021-08-21 3306

-

基于FPGA边沿检测的理解问题?2023-05-10 3512

-

F2产品技术培训_12.模数转换(ADC)2017-03-15 827

-

边沿检测与提取-轮廓跟踪知识详解2018-01-29 652

-

边沿检测的目的及电路原理分析2019-11-19 11724

-

FPGA学习-边沿检测技术2022-11-26 2663

-

Verilog边沿检测的基本原理和代码实现2023-05-12 5444

-

什么是边沿检测2023-06-17 3821

-

Verilog实现边沿检测的原理2023-06-28 4352

全部0条评论

快来发表一下你的评论吧 !