MSP430F5438 32位硬件硬件乘法器的介绍和使用详细概述

电子说

描述

32 位硬件乘法器是一个并行器件,而不是 CPU 内核的一部分。这也就意味着:它在工作时不会涉及 CPU 的活动。硬件乘法寄存器是可以通过 CPU 汇编指令的读或着写进行操作。

硬件乘法器特点:

○无符号乘法;

○ 有符号乘法;

○ 无符号乘加操作;

○ 由符号乘加操作;

○ 8 位,16 位,24 位,和 32 位操作数;

○ 整数乘法

○ 小数乘法

○ 8位和 16 位操作数与 16 位硬件乘法器兼容;

○ 8位和 24 位在没有符号位扩展的情况下,依然可以进行乘法操作;

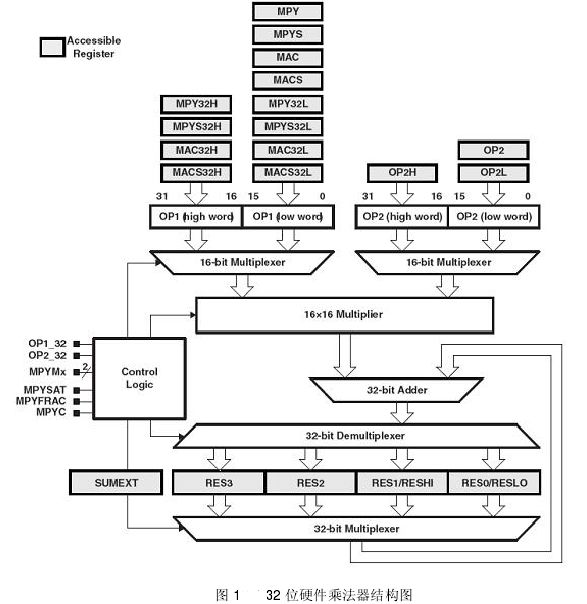

硬件乘法器结构图:

硬件乘法器支持 8 位,16 位,24 位,32 位无符号操作数,有符号操作数,无符号乘、加操作和有符号乘、加操作。操作数的大小,可以通过对"字"或者"字节"的定义来确定。操作数的类型可以通过第一个操作数的写入进行选择。

硬件乘法器有两个 32 位操作数寄存器,操作数 OP1 和操作数 OP2,以及一个 64 位结果寄存器,而这个寄存器需要使用 RES0 和 RES3 寄存器。为了兼容 16 X 16 硬件乘法器,8 位或者 16 位操作数的结果需要使用 RESL0,RESL1 和 SUMNEXT这三个寄存器。RESL0 用于存储 16 X 16 结果的低“字”,RESL1 用于存储 16 X 16 结果的高“字”。以及 SUMEXT 用于存储结果的信息。

硬件乘法器操作:

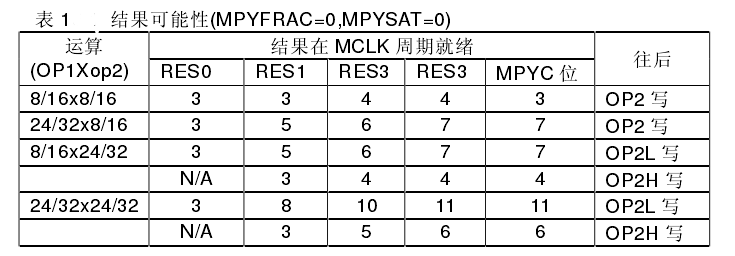

表1总结了针对各种操作数可能的结果的每一个"字"。此表展示了两点,一个是 OP2L 的写入操作,另一个时 OP2H 的写入操作。而最糟糕的情况就是实际结果的可能性。

8 位或者 16 位操作数通常在 3 个 MCLK 周期内准备好,并且在写入 OP2 操作数后的下一个指令就可以读出结果。 如果使用了间接寻址方式进行操作,在结果计算出之前,一个 NOP指令是必需的。

在 OP2 操作数,或者 OP2H 进入 RES0 时 24 位或者 32 位的结果可以通过连续指令的方式进行读取。当时用间接寻址方式进行读结果操作时,一条 NOP 指令时必须的。

由于有一个 32 位第二个操作数的存在,OP2L,OP2H 寄存器都要被使用。又由于两个 16 位部分的被使用,从而使得结果变得复杂。

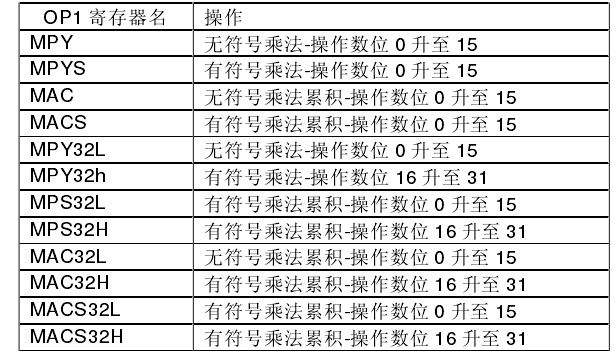

操作数寄存器OP1 :

OP1 操作数寄存器内置 12 个寄存器,如表所示,这些寄存器通常用来装载数据到乘法器,并且也用来选择乘法器模式。写入第一个操作数的“低字”到由乘法操作数类型所确定的地址的乘法操作,才能够开始操作。当写入一个双个“字”到后缀为:32H 的高字寄存器(此时假定 OP1 为 32 位宽)。对于写入 OP2 操作来说,最新的地址写入的优先级通常定义了第一个操作数的宽度。例如:如果 MPY32L 被 MPY32H 写入,则所有的 32 位都将被使用并且 OP1将被设置为:32 位。如果 MPY32H 被 MPY32L 写入,则乘法操作将不会使用 MPY32H,并且假设 MPY32L 将数据写入到 16 位宽的 OP1。

在 OP1 操作数用于连续的操作时,重复性乘法操作就可以被执行,而此时无需载入 OP1 操作数。

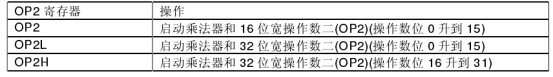

操作数寄存器OP2:

写入第二个操作数到 OP2 寄存器通常会初始化乘法操作。写入 OP2 将会使得一个 16 位宽的第二个操作数和 OP1 中的值开始进行选择操作。写入 OP2L 通常会使得一个 32 位宽的第二个操作数,和被要求写入高字的 OP2H 的乘法器开始进行操作选择。

对于 8 位,24 位操作数寄存器来说,可以通过字节指令进行操作。用一个字节指令进行的乘法器操作,在单独操作期间,乘法器模块将会自动的有一个符号字节的扩展。对于 24 位操作数来说,只有一个高字将会作为字节写入。如果 24 位操作数通过寄存器被定义了符号位扩展,那么作为符号位将会有一个低字的写入,因为寄存器定义了操作数是否有无符号。

一个 32 位操作数的高字在保持不变的条件下,当改变操作数的大小至 16 位,可以通过修改操作数的大小,或者写入操作数寄存器来实现。在 16 位操作执行器件,高字的内容忽略。

注意:

在乘法操作期间改变第一个或者第二个操作数,在默认的条件下,在选择乘法操作时,改变 OP1 或者 OP2,而所得的结果均不正确,因为那时操作数在正在改变。对 OP2 或者 OP2L 的写入,将会对任何正在进行的计算操作进行放弃;同时,也将开始进行一个新的操作。而此时没有计算出的结果对接下来的 MAC 和MACS 操作 不再可靠。

注意要避免 MPYDLYWRTEN 位被置 1。所有写入 MPY32 寄存器的操作通常会由于MPYDLY32=0 而延迟,直到 64 位结果准备好或者 MPYDLY32=1,且 32 位结果算出。

结果寄存器:

乘法操作结果通常都是 64 位宽。而这要使用 RES0,RES3 寄存器。使用一个单操作指令MPYS 或者 MACS,结果将会有符号位的扩展。在 MACS 操作之前如果结果寄存器载入初始值,用户的软件必须仔细关注所写入带符号位的 64 位值。

备注:

在乘法操作期间改变结果寄存器的值 在写入OP2 或者 OP2L 之后,直到初始化操作完成之前,结果寄存器不可以被用户软件修改。

除了 RES0 和 RES3。为了兼容 16 X 16 硬件乘法器,一个 8 位或者 16 位操作的 32 位结果通常使用 RESL0 和 RESL1 以及 SUMEXT。在这种情况下,结果的低位寄存器 RESL0 保存了计算结果的低16位,并且结果保存在寄存器RESH1高16为中。RES0和RES1等同于RESL0和 RESH1。

结果扩展寄存器 SUMEXT 的内容依靠乘法操作并且这些操作在表中以列出。如果所有的操作是 16 位宽或者小于 32 位的结果通常决定符号和 carry。如果操作数中的一个比 16 位数大,则结果将会是 64 位。

MPYC 位通常反映了乘法器的 Carry,而这也列在表中。因而,将会反映在第 33 位或者第 65 位的结果中。当然,前提是小数模式,和连续模式没有被选择.

MACS 下溢出和溢出:

乘法器在 MACS 模式中通常不会自动监测下溢出和溢出。例如: 工作于 16 位输入数据和 32 位结果中,使用 RESL0 和 RESH1,正数的范围的可能数字将在 0 到 07FFF FFFFh,并且负数的结果范围将在:0FFFF FFFFh 到 08000 0000h。

下溢出出现时两个负操作数的相加的计算结果范围在正数范围内。

当两个正操作数相加的结果为负数时,溢出的结果出现!

SUMEXT 寄存器包含了结果符号位(在上面的两种情况下),offffh 通常针对一个 32 的溢出,0000h 通常针对一个 32 位的下溢出。在 MPY32CTL0 中 MPYC 位能够被用来监测溢出状态。如果 Carry 寄存器不同于 SUMEXT 寄存器内容则溢出出现。用户软件必须能够处理这些状态。

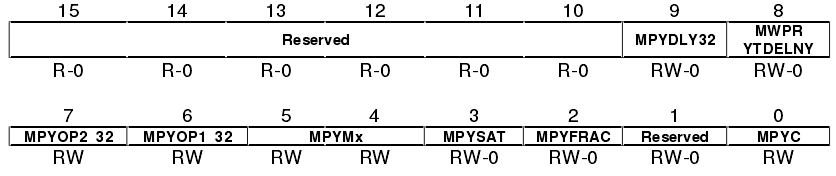

乘法控制寄存器:

Reserved 位 15-10 保留

MPYDL32 位 9 延时写模式

0 写延时在 64 位结果(RES0-RES3)之前是有效的。

1 写延时在 32 位结果(RES0-RES3)之前是有效的。

MPYDLYWRTEN 位 8 延时写使能

64 位(MPYDLY32=0)或 32 位(MPYDLY32=1)结果准备好之前,所有写入到任何 MPY32 寄存器的操作会被延迟。

0 写是不延时

1 写是延时的

MPYOP2_32 位7 乘法器操作数2的位宽度

0 16位

1 32位

MPYOP1_32 位6 乘法器操作数1的位宽度

0 16位

1 32位

MPYMx 位5-4 乘法器模式

00 MPY 乘法

01 MPYS 有符号乘法

10 MAC 乘法积累

11 MACS 有符号乘法积累

MPYSA 位3 饱和模式

MPYFRAC 位2 小数模式

Reserved 位1 保留

MPYC 位0 乘法器的进位标志如果未选择小数模式或饱和模式时可以被看作是第

33或65位结果,因为当切换到小数模式或饱和模式时MPYC位不改变。

举例:

例如 配置 8 * 8 无符号累加硬件乘法

MPY = 0x12; //第一操作数

OP2 = 0x56; // 第二操作数

MAC = 0x12; // 16 位累加乘法器

OP2 = 0x56;

-

为了让生活美好

2019-09-07

0 回复 举报感谢楼主!看英文文档真是头疼啊! 收起回复

为了让生活美好

2019-09-07

0 回复 举报感谢楼主!看英文文档真是头疼啊! 收起回复

- 相关推荐

- 热点推荐

-

关于msp430F5438的程序2013-08-10 1870

-

msp430f5438如何用2013-08-30 1989

-

MSP430F5438例程2013-10-15 8995

-

硬件乘法器2015-11-03 4204

-

msp430f5438资料2016-04-26 3374

-

硬件乘法器的相关资料分享2021-12-09 2232

-

硬件乘法器是怎么实现的?2023-09-22 674

-

基于msp430f5438芯片的控制器2016-04-28 837

-

MSP430F5438数字低频功率放大器2017-03-05 1102

-

msp430F5438用户指南2017-10-12 1169

-

MSP430F5系列16位超低功耗单片机模块原理102018-04-23 1058

-

搜集的很多msp430f5438示例代码2018-05-04 1140

-

MSP430教程Chapt12-硬件乘法器2018-05-07 1341

-

硬件乘法器是什么?2018-05-11 9486

-

MSP430X1XX系列硬件乘法器,比较器,flash讲解2021-11-26 885

全部0条评论

快来发表一下你的评论吧 !