基于FPGA的PCIe设备如何才能满足PCIe设备的启动时间的要求?

可编程逻辑

描述

根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspci可能无法检测到基于FPGA的PCIe设备,需要reboot服务器。众所周知,FPGA芯片规模越来越大,那么如何做才能满足PCIe设备的启动时间的要求呢?

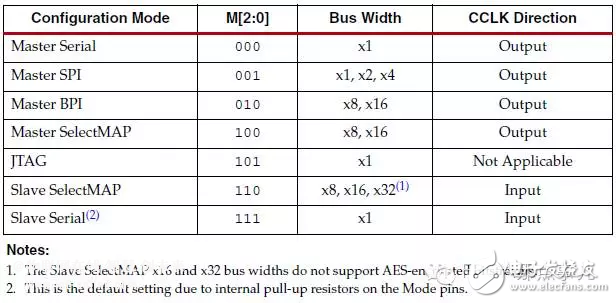

7系列FPGA常见的配置模式如下图所示:

SelectMAP和Master/SlaveSerial是Xilinx早期的FPGA两类配置模式,SPI配置模式为SPI接口允许FPGA把标准的工业SPI Flash作为配置数据存储介质串行读取,同理BPI配置模式指FPGA可以从一个工业标准的并行NOR Flash读取配置数据。显然,对于单FPGA芯片的设计,BPI配置模式为最快速的配置FPGA的方法。在BPI配置模式下,配置时钟可以选择内部CCLK或者外部EMCCLK。下面的公式为计算FPGA配置时间的公式,从公式中可以看出,对于同型号的FPGA,bitstream size越小(7系列bitstream size 大小见附录1),配置时钟的频率越高,数据线位宽越大,则配置时间越短。

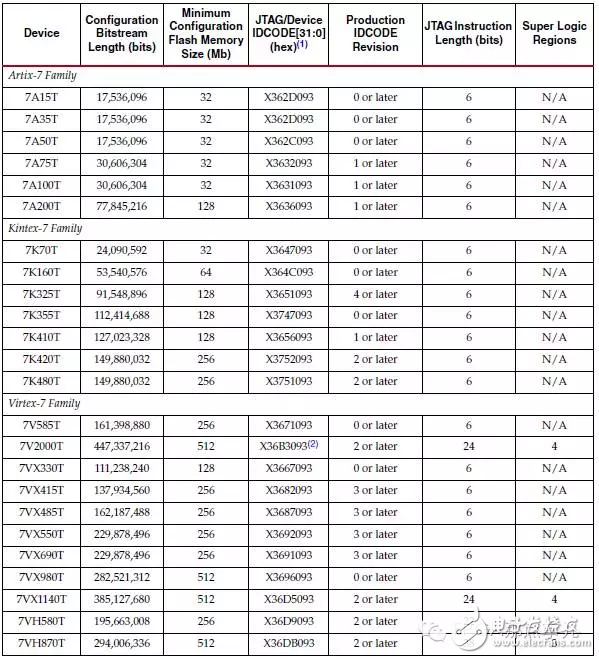

如果使用CCLK,配置速率最大为66Mhz,所以在高速配置FPGA的需求下,需要外部EMCCLK来满足配置时间的要求。EMCCLK最大频率计算方法见下面的公式,并且不能超过DS181, DS182, 和 DS183文档中定义的最大值。在7系列中,常见的EMCCLK时钟频率为100Mhz。比如对于K7325T,通过查阅bitstream size的大小为91,548,896 bits(87.3Mb),EMCCLK时钟频率为100Mhz,数据位宽为16,则配置时间为57ms,可以满足PCIe设备启动时间的要求。

在确定了采用BPI模式配置及外部配置时钟EMCCLK后,FPGA设计应该如何做呢。首先必须把EMCCLK引入到FPGA中,所以在逻辑顶层,要有EMCCLK的定义,如下所示:

Input emcclk;

在生成bitstream的时候,需要对EMCCLK做管脚约束,如下所示:

set_property IOSTANDARD LVCMOS18[get_ports emcclk]

set_property PACKAGE_PIN R24[get_ports emcclk]

还需要在xdc中添加如下约束,也可以在图形界面中完成,添加在xdc里可以减少图形界面的交互,提高设计效率。

set_propertyBITSTREAM.CONFIG.EXTMASTERCCLK_EN DIV-1 [current_design]

set_propertyBITSTREAM.CONFIG.BPI_SYNC_MODE TYPE2 [current_design]

如果通过上述公式的计算,发现仍然不能满足100ms的要求,还可以尝试如下方法解决配置FPGA的问题。第一种比较简单,生成bitstream的时候,可以选择压缩bitsteam的大小,这个设置可以通过图形界面完成,也可以通过在xdc里添加Compress参数实现。第二种方法比较麻烦,可以使用Tandem Configuration,具体请参考xapp1179。通过公式的计算,以及上述几种方法的选择,最终可以使设计满足PCIe设备启动时间的要求。

附录:7系列FPGAbitstream size

-

基于ZCU106实现PL PCIE Tandem PROM功能 从而满足100MS之内主板能识别PCIE接口2022-08-02 4500

-

CPM PCIE做RC时如何完成对复位信号的控制2024-12-04 2560

-

FPGA的PCIE接口应用需要注意哪些问题2024-05-27 3450

-

PCIe协议分析仪能测试哪些设备?2025-07-25 1701

-

求助:PCIE设备数据交换2014-12-25 7740

-

寻求fpga大牛开发一个简单的fpga pcie设备2019-02-11 4684

-

使用Zynq设备和Tandem配置的PCIe BOOTUP时间有什么要求?2020-06-09 4300

-

PCIe设备的低功耗状态2021-12-28 1428

-

PCIe设备的低功耗状态要求2022-01-03 3433

-

可以将多个PCIe设备连接到一般的单个PCIe控制器吗?2023-05-05 588

-

Xilinx7系列基于PCIe的设计如何满足PCIe启动时间的要求2017-02-07 4422

-

PCIe总线体系概述与基于FPGA的PCIe接口的实现2017-10-13 1485

-

PCIe 9110IM PCIe总线转CAN设备手册2022-10-17 944

-

PCIe 5.0均衡模式:缩短链路启动时间2023-05-26 3527

-

访问PCI/PCIe设备的流程2023-07-30 2691

全部0条评论

快来发表一下你的评论吧 !