如何通过HiFive1套件实现快速原型开发

描述

嵌入式系统开发人员一直在想方设法进一步缩短开发时间,特别是针对概念验证和快速原型开发。虽然开发套件已成为捷径之选,但设计人员需要找到一个平衡点,既兼顾外形尺寸和广受支持的生态系统,又要考虑性能要求。

Arduino Uno 开发板就是这种需要找到平衡点的很好例子。由于成本低廉,并在理论上具有数百个可提供 Arduino I/O 插件扩展功能的 Arduino 盾板,其外形尺寸在这一领域极其流行。但是,针对特定嵌入式应用,某些开发人员可能需要比 8 位微控制器所能提供的更高性能。

对于他们来说,Crowd Supply 的 HiFive1 开发套件可能才是解决方案。本文将介绍低成本的 HiFive1 开发套件,讨论如何通过其功能实现高性能嵌入式系统的快速原型开发。此外,本文将介绍帮助设计人员入门的可用开发工具。

什么是 HiFive1?

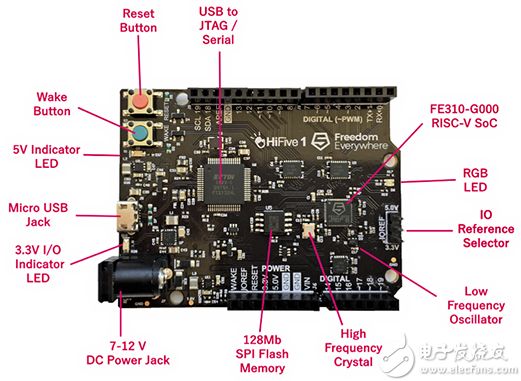

HiFive1 开发套件基于一款集成 32 位 RISC-V(读音“risk-five”)处理器内核的微控制器(图 1)。该开发板可接受 Arduino 式盾板,从而大幅提升了其对嵌入式设计快速原型开发的实用性。

图 1:HiFive1 Arduino 兼容开发板使用一个基于 32 位 RISC-V 处理器内核的微控制器。(图片来源:SiFive)

HiFive1 的核心是 RISC-V 处理器内核。这就需要 Arduino 开发板背后的开源概念,并将其一直扩展到处理器本身。RISC-V 是开放式指令集架构 (ISA),基于两个基础:自 20 世纪 80 年代以来一直采用的精简指令集计算 (RISC) 概念,以及开源原则。因为 RISC-V ISA 是开源的,所以可自由地用于任何目的。任何人都可以设计、制造和销售基于 RISC-V 的芯片和软件,而无需支付版税。

HiFive1 板上基于 RISC-V 的微控制器可通过编程支持芯片内执行 (XIP) 模式,以便在指令高速缓存重新填充期间降低 SPI 指令执行时间。微控制器的四路 SPI (QSPI) 端口支持 32 字节猝发读取,使用存储器的 XIP 模式,加快来自 QSPI 闪存的指令高速缓存重新填充,进而提升性能。

微控制器可在高于 320 MHz 的时钟速率下运行,但在 HiFive1 板上,应限制时钟速率不高于 133 MHz,以便保持微控制器的 SPI 串行时钟在开发板的 128 Mbit QSPI 闪存限制范围内工作。

Arduino 式针座(包含注意事项)

HiFive1 开发套件复制了 Arduino 独特的 I/O 针座布局。它可以接受数以百计可用 Arduino 盾板中的多数类型,但有几点需要注意。

首先,微控制器没有模拟输入引脚。HiFive1 开发套件的 Arduino 式针座只能进行数字 I/O、中断和脉冲宽度调制 (PWM) 引脚分配。Arduino Uno 开发板上 A0 至 A5 模拟引脚所用的物理针座位置在 HiFive1 开发板上标注为 D14 至 D19 数字 I/O 引脚。如果有必要添加模拟功能,可使用众多可用模数转换器 (ADC)、数模转换器 (DAC) 或组合 ADC/DAC Arduino 盾板中的一种。

另请注意:

-

设计人员可将多达 9 个 PWM 发生器分配到 HiFive1 开发套件上的 Arduino 式针座引脚。

-

HiFive1 开发套件的所有 19 个 Arduino 式针座 I/O 引脚均可用作中断输入。

板载电压转换器可根据跳线设置,灵活地将所有 HiFive1 开发套件的数字 I/O 引脚设置为 3.3 V 或 5 V 逻辑电平。单跳线设置(图 1 开发板上带 IOREF 标志)可定义 HiFive1 开发套件的 Arduino 式针座上所有 I/O 引脚的逻辑电平。

这就引出了第二个注意事项:迄今为止,只有以下两款 Adafruit Arduino 盾板通过了 HiFive1 测试,因为只有针对这两款盾板的 Adafruit 支持库已移植到 HiFive1 库:

-

Adafruit 的电阻式触摸屏和 LED 显示屏

-

Adafruit 的 BLE SPI Friend

即便如此,尽管支持库可能需要微调,但任何与 SPI、UART 或数字 I/O 通信的盾板都应该易于搭配 HiFive1 使用。HiFive1 外设盾板支持库还处于初期阶段:预计支持的盾板数量会增加。

好硬件需要好软件支持

GitHub 上提供了针对 HiFive1 开发套件的软件开发工具。这些工具包括用于 RISC-V 处理器架构的 C 编译器和汇编器、用于 RISC-V 处理器的 GDB 主机驻留调试器和 OpenOCD(片上调试器)的 RISC-V 版本。

一旦程序被编写、编译和汇编,开发人员就可以通过 USB 调试接口将其上传到 HiFive1 开发套件。HiFive1 将该程序存储在其板载 SPI 闪存芯片中。板载闪存芯片的容量为 16 Mb,比 8 位 Arduino Uno 板上的代码存储容量大得多。地址空间扩展只是诸如 RISC-V 的 32 位处理器架构的众多优点之一。该微控制器的片上 16 Kb SRAM 也相对较大。

处于开发板核心地位的芯片

接下来将详细介绍 HiFive1 开发套件的核心,即微控制器(图 2)。

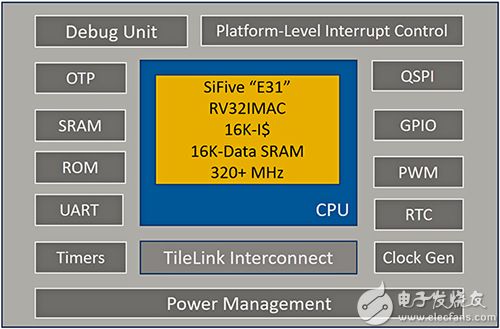

图 2:基于 RISC-V 的开源微控制器的简化框图。(图片来源:SiFive)

该微控制器的中心是基于开源的 32 位 RISC-V ISA 的 CPU 内核。就 RISC-V 而言,核心是 RV32IMAC 处理器,这意味着它使用的是基本 32 位 RISC-V 整数指令集 (RV32I),具有整数硬件乘除 (M) ;原子、实时指令 (A);以及对 16 位精简 (C) 指令集的附加支持。另外还有 64 位和 128 位版本的 RISC-V ISA。该内核还包括 16 Kb 的指令缓存(在框图中标记为“I $”)和 16 Kb 的暂存器 SRAM。几个标准外设包括定时器、PWM 信号发生器、实时时钟、UART、QSPI 串行接口以及围绕处理器内核的一个片上硬件调试模块。

RISC-V 架构幕后有谁或者说有什么?为什么?

HiFive1 开发套件和微控制器实际上是开源 RISC-V 处理器架构的硬件演示工具,是一个假设论证:世界真的需要另一种处理器架构吗?

RISC-V 项目始于加州大学伯克利分校,最终超越了大学研究的范畴,充分发挥了更多自愿参与者和电子行业人士的想象力。该项目的最终结果是开源代码 RISC 处理器 ISA(指令集架构),与其他任何 32 位 RISC ISA 几乎一样。不同之处在于任何人都可以自由地将 RISC-V ISA 用于任何目的。

它需要一个生态系统

就 HiFive1 开发板而言,嵌入式系统开发人员需要的不仅仅是处理器或微控制器芯片。对于 RISC-V,嵌入式开发人员需要工具、示例代码、库和软件堆栈等形式的开发支持。这类支持来自围绕成功的处理器架构和用户而发展的生态系统。RISC-V 处理器架构相对较新,其生态系统也一样,但它在不断发展。除了上面讨论的 SiFive 开发工具外,RISC-V 生态系统中的其他开发工具目前还包括:

总结

经济实惠的 Arduino Uno 开发板外形小巧轻便,可访问数百个 I/O 和外设盾板。HiFive1 开发套件利用这些现有盾板,通过紧密复制紧凑型 Arduino Uno 开发板的外形尺寸和独特针座配置,将其与基于 RISC-V 的 32 位微控制器配接。

HiFive1 开发套件具有 16 Mb 板载闪存,可提供更高的代码存储能力。尽管它是一款新的架构,但崭露头角的开源 RISC-V 生态系统提供了一套扩展的软件开发工具,包括编译器、汇编器、调试器和 Arduino IDE 库。

-

开源 GNU MCU Eclipse:一系列基于 GNU 工具链的 Eclipse 多平台嵌入式开发插件和工具。

-

Segger 的 Embedded Studio for RISC-V:一款用于嵌入式 C/C ++ 软件开发的跨平台 IDE 以及该公司的 J-Link 调试探测器。

-

-

LSICVM02套件快速安装指南2023-08-23 1320

-

RL78/G1M 快速原型开发板快速入门指南2023-03-13 439

-

在Arduino中怎样才能快速的安装STM32套件呢2021-12-15 1784

-

IHM001套件和IHM002套件有什么区别?2021-07-21 929

-

使用英特尔物联网开发人员套件实现快速原型设计2020-05-31 2563

-

EVAL-ADICUP3029套件如何设置并使用工具和软件2019-07-31 2855

-

如何使用EVALSTPM34套件?2019-07-23 1037

-

HiFive1 Rev B与HiFive1的区别2019-04-04 6967

-

什么是HiFive1?详细介绍HiFive1开发套件的核心2018-06-05 11350

-

恩智浦推快速物联网原型套件 可加速PoC开发进程2018-03-09 2359

-

为加速原型开发,ADI推出FPGA夹层卡快速原型开发套件2013-02-28 1096

-

莱迪思MachXO2套件:专用原型开发套件2012-10-30 2148

全部0条评论

快来发表一下你的评论吧 !