德州仪器CDCE6214Q1TM超低功耗时钟发生器技术解析

描述

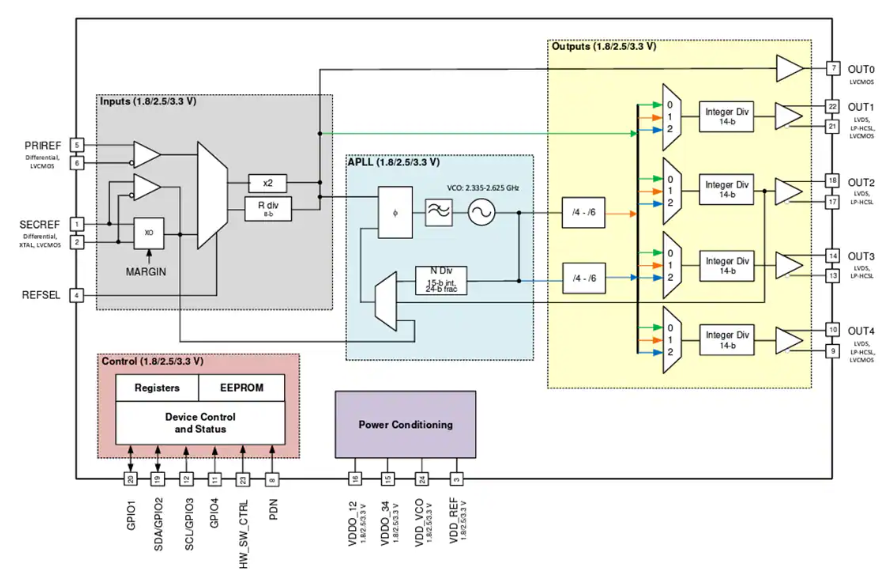

Texas Instruments CDCE6214Q1TM超低功耗时钟发生器是是一款适合汽车应用的4通道、中级抖动时钟发生器,可生成五个独立时钟输出。这些输出在各种驱动器模式之间可选。输入源可以是单端或差分输入时钟源,也可以是晶体。CDCE6214Q1TM具有一个分数N PLL,可在任何输入频率下合成不相关的基础频率。

数据手册:*附件:Texas Instruments CDCE6214Q1TM超低功耗时钟发生器数据手册.pdf

特性

- 符合汽车应用类AEC-Q100标准

- 温度等级2(–40°C至+105°C)

- 支持功能安全

- 来辅助功能安全系统设计的文档

- 可配置的高性能、低功耗、frac-N PLL,具有带杂散(12kHz至20MHz,FOUT>100MHz)的RMS抖动:

- 整数模式

- 最大差分输出:典型值350fs,最大值600fs

- LVCMOS 输出:典型值1.05ps,最大值1.5ps

- 分数模式

- 差分输出:典型值1.7ps,最大值2.1ps

- LVCMOS输出:典型值2.0ps,最大值4.0ps

- 整数模式

- 支持PCIe Gen1/2/3/4(有SSC)和Gen 1/2/3/4/5(无SSC)

- 2.335GHz至2.625GHz内部VCO

- 典型功耗:4输出通道为65mA,单输出通道为23mA。

- 通用时钟输入,两个用于冗余的参考输入

- 差分交流耦合或LVCMOS:10MHz至200MHz

- 晶振:10MHz至50MHz

- 灵活的输出时钟分配

- 四通道分频器,具有多达五个独特输出频率,范围为24kHz至328.125MHz

- OUT0 – OUT4引脚具有类似LVDS、LP-HCSL或LVCMOS输出

- 无中断输出分频器开关和输出通道同步

- 通过低电平有效GPIO和寄存器实现独立输出使能

- 频率裕量选择

- DCO模式:频率以10ppb或更小的阶跃幅度递增/递减

- 完全集成、可配置的环路带宽:100kHz至1.6MHz

- 单电源或混合电源可进行电平转换:1.8V、2.5V、3.3V

- 可配置的GPIO和灵活的配置选项

- 兼容I^2^C的接口,高达400kHz

- 具有两个页面和外部选择引脚的集成EEPROM,可现场编程。

- 支持100Ω系统

- 低电磁辐射

- 小尺寸:24引脚 VQFN (4mm × 4mm)

功能框图

德州仪器CDCE6214Q1TM超低功耗时钟发生器技术解析

一、产品核心特性

CDCE6214Q1TM是德州仪器推出的汽车级超低功耗时钟发生器,具有以下突出特性:

1. 高性能时钟生成

- 集成frac-N PLL,支持整数/分数模式

- VCO频率范围:2.335GHz至2.625GHz

- 支持PCIe Gen1-5时钟生成(带/不带SSC)

2. 多模式输出

- 4个差分输出通道(OUT1-OUT4)

- 1个LVCMOS输出(OUT0)

- 支持LVDS、LP-HCSL和LVCMOS输出格式

3. 超低功耗设计

- 4通道输出典型功耗65mA

- 单通道输出典型功耗23mA

- 0.6μA超低关断电流

4. 汽车级可靠性

- AEC-Q100 Grade 2认证(-40℃至+105℃)

- 24引脚VQFN封装(4×4mm)

二、关键参数对比

| 参数 | 条件 | 典型值 | 单位 |

|---|---|---|---|

| 抖动性能 | 差分输出,整数模式 | 350fs | RMS |

| 输出频率范围 | 差分输出 | 24kHz-328.125MHz | - |

| 输入频率范围 | 晶体模式 | 10-50MHz | - |

| 电源电压 | 核心/输出 | 1.8/2.5/3.3V | - |

| 工作温度 | 全范围 | -40至+105 | ℃ |

三、典型应用设计

1. PCIe时钟生成方案

配置要点:

- 使用25MHz晶体输入

- 配置为100MHz LP-HCSL输出

- 启用0.5%下行扩频(SSC)

- 寄存器配置:

- PLL_NDIV = 96

- PSA = 4, IOD = 6

- SSC_SEL = 3h(25MHz PFD,-0.5%下行扩频)

实测性能:

- RMS相位抖动:475fs(12kHz-20MHz)

- 满足PCIe Gen3规范要求

2. 汽车信息娱乐系统时钟树

设计优势:

- 单一器件生成多路时钟:

- 24.576MHz音频时钟(LVCMOS)

- 100MHz处理器时钟(LVDS)

- 148.5MHz显示时钟(LP-HCSL)

- 支持频率微调(DCO模式,步进≤0.1ppm)

四、设计要点

1. 电源设计建议

- 去耦方案:

- 每电源引脚配置:

- 4.7μF陶瓷电容(X7R)

- 470nF陶瓷电容

- 100nF陶瓷电容

- 每电源引脚配置:

- 布局要点:

- 电源走线宽度≥0.2mm

- 使用多个过孔连接电源平面

2. 热设计指南

- 热阻参数:

- θJA = 32.5°C/W

- θJC = 12.2°C/W

- 推荐措施:

- 使用2oz铜厚PCB

- DAP焊盘配置12个φ0.3mm散热过孔

- 顶层铜箔面积≥15mm²

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析CDCE937/CDCEL937:灵活低功耗LVCMOS时钟发生器2026-02-09 447

-

CDCE6214:超低功耗时钟发生器的卓越之选2026-02-08 324

-

汽车级时钟发生器CDCE6214Q1TM:特性与应用解析2026-02-06 264

-

CDCE6214 超低功耗时钟发生器技术文档总结2025-09-12 907

-

CDCE6214Q1TM 超低功耗时钟发生器技术文档总结2025-09-11 841

-

CDCI6214超低功耗时钟发生器(具有PCIe支持、四路可编程输出和EEPROM)数据表2024-08-21 597

-

CDCE6214-Q1超低功耗时钟发生器数据表2024-08-20 440

-

CDCE6214超低功率时钟发生器数据表2024-02-28 548

全部0条评论

快来发表一下你的评论吧 !