FPGA和CPU如何搭配?

描述

一个故事理解流水线、并行、缓存、内存、存储

蛋蛋花了一天给小蛋蛋做了一个玩具汽车,没想到做的太好了,同学们都来买。蛋蛋一个人忙不过来,就一家人合作生产。蛋蛋负责把原料分类摆放在桌上,小蛋蛋拧螺丝组装,蛋妈把玩具放到包装盒里。三个人采用流水线的方式,每个人都没闲着,生产效率大为提高,一天能造50个玩具。

隔壁老王看到蛋蛋做玩具赚钱了,也一家三口加入造玩具大军,慢慢整个小区家家冒烟,户户生产。五十家人采用并行工作的方式,一天能造2500个玩具。

本来,蛋蛋家里的工作台旁边有个箱子,叫做缓存。把玩具生产的原料和生产好的玩具放在自己家里,离得又近又速度快。

小区里家家冒烟后,原料供应和玩具运输需求量大增。居民们在小区中央建了一个仓库,叫做内存,里面放了很多原料和玩具,看门大爷每天推着手推车到每家每户去送原料,收玩具,人们给他起了个外号——总线。

镇长看到蛋蛋家园小区交的玩具税日渐增长,为了增加收入,决定建设玩具小镇,于是镇上每个小区都开始生产玩具,玩具生产规模日渐扩大。镇中心建了一个大仓库,集中存放原料和玩具,仓库太大了,如果一个个领取太不方便,所以每次提货或者送货必须以500个为单位批量领取,这个大仓库叫做硬盘。

在我们的计算机中,CPU采用流水线的方式工作,把一个任务分成十几个步骤,用十几级流水线计算,速度增长了十几倍。多核CPU就是并行工作,又能把计算速度提升几倍。计算速度快了之后,对数据的读写速度要求变高,所以,现代CPU设计了先进的缓存系统,可以说,对现代通用CPU来说,缓存才是核心。

可是对某些应用来说,CPU有点走歪了,它擅长的是用高频率把顺序执行的任务分解成很多级流水线高速执行,但是对于深度学习等计算,需要的是大量的并行计算,这时候,CPU的核心数成了限制。

FPGA的并行性

蛋蛋设计了一个复杂的机器叫CPU,它能一条条读取并执行蛋蛋写好的指令,把任务分解成很多级流水线,生产出各种各样复杂的玩具。

玩具市场总是有新的流行风尚,最近突然乐高玩具开始大火,每一个积木都长得差不多,但是很多的积木就可以搭出复杂的形状。现在的家长都希望寓教于玩,让孩子玩游戏也能动脑筋,蛋蛋看到了这个趋势,也想生产乐高积木。可是他发现复杂的机器CPU的生产效率太低了,他需要的是同时大批量几百上千个机器并行生产,而CPU最多只能同时生产十几个。所以,蛋蛋又钻研了一段时间,研制出新的机器——FPGA。这台机器里面有几千个小引擎,按照蛋蛋设定好的任务,大家热火朝天地生产自己的小积木。

我们上大学学习的C语言是给CPU编程的语言,它的特点就是写一个main函数,里面有很多内容,程序启动后,从头按顺序执行到结尾。这是因为只有一个CPU在运行,程序会转化为指令让CPU一条条执行。

FPGA是并行计算机,它的基础编程语言叫做Verilog,在这种语言中,每一段程序,都会转化为FPGA芯片里面的一个小计算引擎,大家并行执行,热火朝天的干自己的活。

FPGA和CPU如何搭配

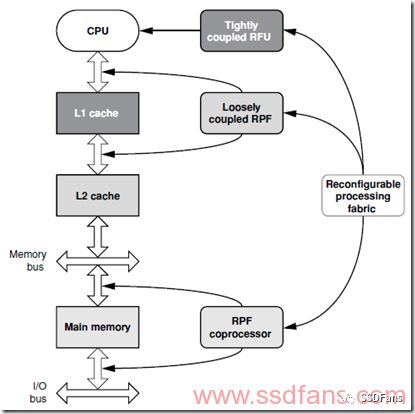

FPGA作为可重构计算引擎,一般要和CPU搭配使用。如下图,可重构计算引擎要么直接和CPU紧密相连,要么和缓存相连,前者叫紧耦合,后者叫松耦合。还有一种情况下,FPGA是作为协处理器coprocessor连到内存总线上,和CPU共享内存。

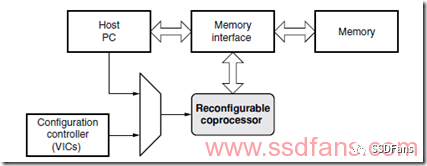

如下图,FPGA作为协处理器,CPU把指令写入内存,FPGA从内存读取指令执行,并把计算结果写入内存。这种模式的优点是简单易行,协处理器和CPU分离。瓶颈在于共享内存,限制了性能,同时由于通过内存交互,CPU和FPGA之间通信延迟变长了。所以适合于FPGA能独立执行的加速任务,比如视频编解码、数据加解密等。

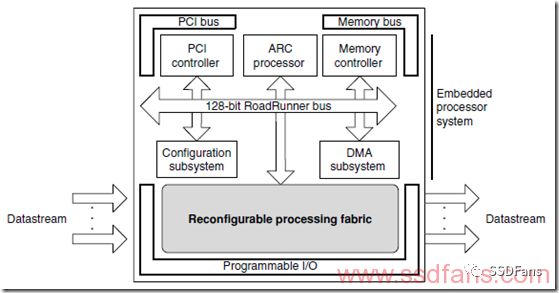

下图是一个松耦合的例子。CPU(ARC)和可重构计算逻辑放在一颗芯片里面,CPU可以直接访问可重构计算引擎,而且共享内存,可重构计算引擎可以通过DMA方式直接读写内存。同时,我们看到可重构计算引擎有自己的数据读写接口,所以可以脱离CPU独立工作,打工创业两不误。

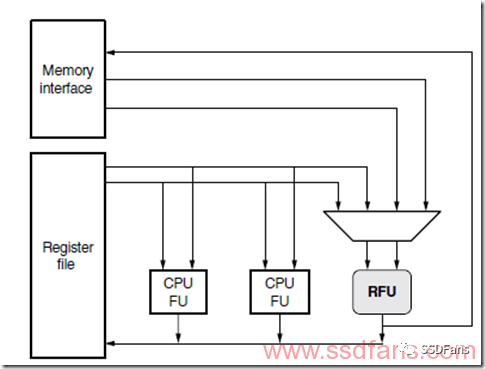

再来看一个紧耦合的例子。如下图,CPU FU是一般CPU的基本计算单元,例如ALU、乘法器、浮点处理器等,RFU跟这些基本单元一样,放在芯片里面,而且可以直接被CPU的寄存器控制,还能访问缓存中的数据。

总结一下,协处理器相当于外地当官的,只能接受皇帝的命令工作。松耦合就是京城里的官员,可以定期去皇宫跟皇帝唠唠嗑。紧耦合已经到了外戚和太监的地步,能在皇宫里经常值班。

松耦合和紧耦合都要在芯片里面放可重构计算引擎,成本比较高,但是效率也很高。相当于CPU里面有个FPGA,随时可以编程让它做不同的计算。处理视频时,配置成视频编解码逻辑,做AI计算时配置成深度学习计算器,一个芯片既有CPU,又有可以配置的硬件计算引擎。

-

TKW794785136

2019-06-19

0 回复 举报通俗易懂,赞一个 收起回复

TKW794785136

2019-06-19

0 回复 举报通俗易懂,赞一个 收起回复

-

FPGA比CPU和GPU快的原理是什么2018-05-31 17327

-

FPGA真的能取代CPU和GPU吗?2016-05-16 17987

-

混合CPU_FPGA系统的调试方法2009-07-23 718

-

FPGA、CPU、DSP的竞争与融合2011-09-23 928

-

三步教你如何DIY电脑主板和CPU的搭配2017-11-27 16705

-

FPGA与CPU有什么关系_FPGA与CPU的联系2018-01-02 17149

-

简单了解CPU和内存搭配规律2018-07-09 34779

-

FPGA为什么比CPU和GPU快2018-02-20 1920

-

如何才能合理的搭配CPU和主板2019-10-26 7209

-

使用FPGA实现CPU设计的毕业论文总结2020-08-03 1510

-

如何使用CPU配置FPGA的详细资料说明2020-08-13 1392

-

如何使用FPGA实现八位RISC CPU的设计2020-08-19 1355

-

为什么FPGA主频比CPU慢,但却可以用来帮CPU做加速2020-11-20 4629

-

FPGA+GPU+CPU国产化人工智能平台2025-01-07 1836

-

fpga和cpu的区别 芯片是gpu还是CPU2025-02-01 3221

全部0条评论

快来发表一下你的评论吧 !