SN74AHCT125四总线缓冲门技术解析与应用指南

描述

Texas Instruments SN74AHCT125/SN74AHCT125-Q1四路总线缓冲门是采用具有三态输出的独立线路驱动器的四路总线缓冲门。当相关输出使能 (OE) 输入为高电平时,输出被禁用。当OE为低电平时,各自栅极将数据从A输入传递到Y输出。为确保上电或断电期间的高阻抗状态,OE应通过上拉电阻连接到VCC;驱动器的电流吸收能力决定电阻的最小值。Texas Instruments SN74AHCT125-Q1器件符合汽车应用类AEC-Q100认证。

数据手册:

特性

- 输入兼容TTL电压

- 闭锁性能超过250mA,符合JESD 17标准

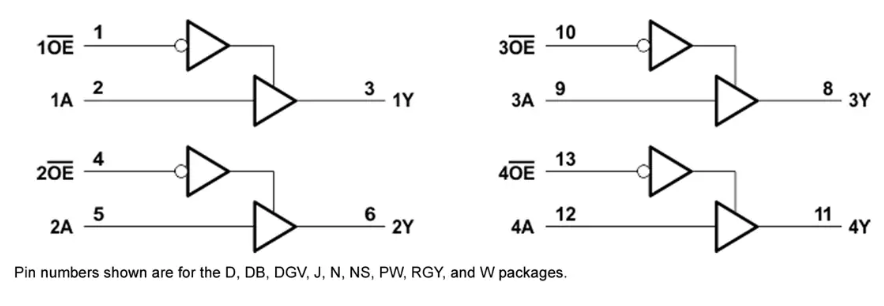

功能框图

SN74AHCT125四总线缓冲门技术解析与应用指南

一、产品核心概述

SN74AHCT125是德州仪器(TI)推出的四总线缓冲门集成电路,采用先进的AHCT技术,提供3态输出控制功能。该器件支持宽电压工作范围,是数字信号隔离与驱动的理想解决方案。

核心特性:

- 工作电压范围4.5V至5.5V

- 4个独立控制的总线缓冲通道

- 典型传播延迟5.5ns(15pF负载)

- 输出驱动能力±8mA

- 符合TTL电平输入兼容性要求

- 提供14引脚多种封装选项(SOIC/SSOP/TSSOP/VQFN等)

二、功能架构解析

1. 内部逻辑结构

每个缓冲通道包含:

- TTL兼容输入级(带施密特触发)

- CMOS输出驱动级

- 独立输出使能控制(OE)

- 过流保护电路

2. 关键参数指标

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| VOH | IOH=-8mA | 3.94 | 4.4 | - | V |

| VOL | IOL=8mA | - | 0.36 | 0.44 | V |

| ICC | 静态工作 | - | 1.35 | 20 | µA |

| tPLH | CL=15pF | 1 | 3.8 | 6.5 | ns |

三、引脚配置说明

1. 引脚功能定义

| 引脚号 | 名称 | 类型 | 功能描述 |

|---|---|---|---|

| 1,4,10,13 | 1OE-4OE | 输入 | 输出使能控制(低有效) |

| 2,5,9,12 | 1A-4A | 输入 | 数据输入端 |

| 3,6,8,11 | 1Y-4Y | 输出 | 3态输出端 |

| 7 | GND | 电源 | 接地 |

| 14 | VCC | 电源 | 正电源(4.5-5.5V) |

2. 封装选项

- D(SOIC-14) :标准小外形封装

- DB(SSOP-14) :薄型收缩小外形封装

- PW(TSSOP-14) :超薄收缩小外形封装

- RGY(VQFN-14) :无引线四方扁平封装

- N(PDIP-14) :塑料双列直插封装

四、典型应用场景

1. 数字信号隔离

- 微控制器IO口扩展

- 总线竞争隔离

- 多主机系统仲裁

2. 电平转换接口

- TTL到CMOS电平转换

- 5V系统与3.3V器件接口

- 混合电压系统互连

3. 信号驱动增强

- 长线传输驱动

- 多负载驱动

- 高容性负载驱动

五、设计指南

1. 电源设计要点

- 建议每个VCC引脚配置0.1μF陶瓷去耦电容

- 电源走线宽度≥0.3mm(1oz铜厚)

- 避免电源环路面积过大

2. PCB布局建议

- 关键信号远离高频噪声源

- 使能信号走线应尽量短

- 输出走线避免直角转弯

- 散热焊盘区域保证足够过孔

3. 热管理方案

| 封装类型 | θJA(°C/W) |

|---|---|

| SOIC(D) | 124.5 |

| SSOP(DB) | 96 |

| TSSOP(PW) | 147.7 |

| VQFN(RGY) | 87.1 |

六、注意事项

- 未使用引脚处理:

- 所有未使用的输入端必须接VCC或GND

- 未使用的输出端可悬空

- 上电顺序:

- 建议OE引脚通过上拉电阻接VCC

- 上电期间避免输出冲突

- 负载限制:

- 总输出电流不超过50mA

- 容性负载≤50pF以保证信号完整性

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74AHCT126四路总线缓冲器技术解析与应用指南2025-08-22 2132

-

SN74AHC125四路总线缓冲门技术解析与应用指南2025-08-15 1303

-

SN74AHCT1G126 单总线缓冲门技术解析与应用指南2025-08-08 1267

-

具有三态输出的四总线缓冲门SN74LV125A-Q1数据表2024-05-27 533

-

具有三态输出的四路总线缓冲门SN74AHCT125-EP 数据表2024-05-24 444

-

具有三态输出的四总线缓冲门SN54BCT125A SN74BCT125A数据表2024-05-13 444

-

具有三态输出的四总线缓冲门SN54ABT125 SN74ABT125数据表2024-05-10 550

-

具有三态输出的汽车类四路总线缓冲门SN74AHCT125-Q1数据表2024-05-07 504

-

具有三态输出的单路总线缓冲门SN74AHCT1G125数据表2024-04-29 441

-

SN74AHCT125 具有三态输出的四路总线缓冲器闸2018-10-16 1417

全部0条评论

快来发表一下你的评论吧 !