DS90UB638-Q1 FPD-Link III解串器技术解析与应用指南

描述

Texas Instruments DS90UB638-Q1 4.16Gbps单输入解串器是一款多功能解串器,可通过FPD-Link III接口从一个源接收串行传感器数据。与DS90UB635-Q1串行器配合使用时,DS90UB638-Q1接收来自成像仪的数据,支持卫星雷达、2MP/60fps和4MP/30fps摄像头以及其他传感器(如LIDAR和ToF)。接收的数据在符合MIPI CSI-2标准的输出端呈现,从而与下游处理器互连。为2通道运行配置CSI-2接口时,会提供一个完全相同的MIPI CSI-2时钟通道来提供复制输出。复制模式可创建两个接收视频流副本,用于并行处理和数据记录。

数据手册:*附件:Texas Instruments DS90UB638-Q14.16Gbps单输入解串器数据手册.pdf

Texas Instruments DS90UB638-Q1符合AEC-Q100标准,旨在通过50Ω单端同轴电缆接收数据。该解串器非常适合同轴电缆供电(PoC)的应用。接收均衡器会自动适应来补偿电缆损耗特性(无需额外编程),包括随时间推移而出现的电缆老化。每个FPD-Link III接口包括一个单独的低延迟双向控制通道(BCC)。BCC可连续传送I^2^C、GPIO和其他控制信息。用于传感器同步和诊断功能的GPIO信号也使用BCC。

特性

- 符合汽车应用类AEC-Q100标准

- –40℃ 至+105℃环境工作温度范围(温度等级2)

- 符合ISO 10605和IEC 61000-4-2 ESD标准

- 兼容同轴电缆输电 (PoC) 的收发器

- 兼容MIPI DPHY版本1.2/CSI-2版本1.3

- CSI-2数据速率可扩展至每个数据通道400Mbps/800Mbps/1.5Gbps /1.6Gbps

- 支持1、2、3和4数据通道

- 支持多达四个虚拟通道

- 可编程数据类型

- 高级数据保护和诊断,包括CRC数据保护、传感器数据完整性检查、I^2^C写保护、远程电压和温度测量、可编程警报、BIST、图形生成以及线路故障检测

- 超低数据和控制路径延迟

- 支持单端同轴电缆

- 单输入解串器

- 自适应接收均衡

- 具有快速模式增强版的I^2^C(速度高达1Mbps)

- 用于摄像头同步和诊断的灵活GPIO

- 用于防伪保护的唯一DIE-ID

- 支持单端同轴或屏蔽双绞线 (STP) 电缆

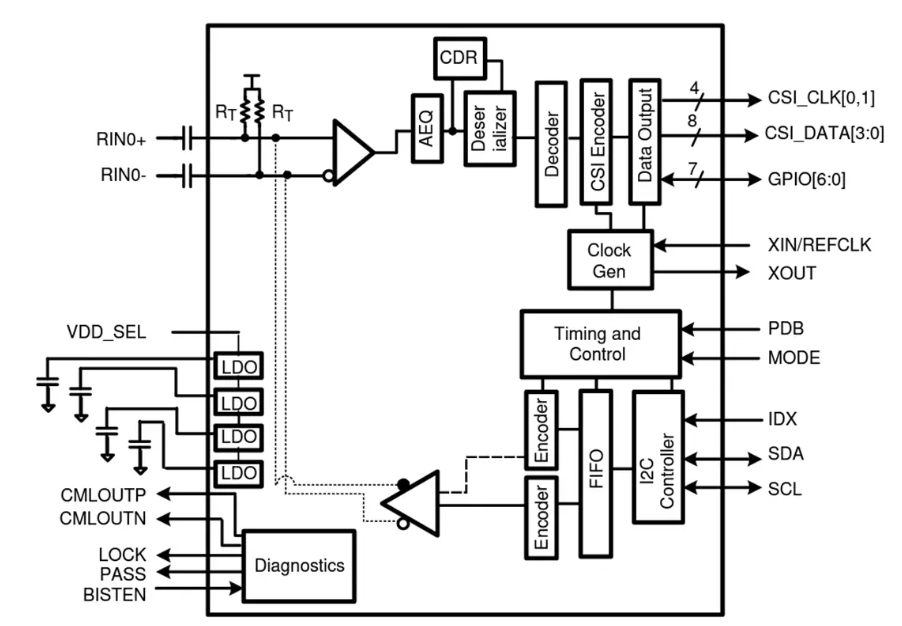

功能框图

DS90UB638-Q1 FPD-Link III解串器技术解析与应用指南

一、产品概述

DS90UB638-Q1是德州仪器(TI)推出的一款汽车级FPD-Link III单输入解串器,专门设计用于高级驾驶辅助系统(ADAS)和汽车视觉应用。该器件支持4.16Gbps高速数据传输,具有MIPI CSI-2输出接口,满足现代车载摄像头系统的严苛要求。

关键特性:

- AEC-Q100 Grade 2认证(-40°C至+105°C工作温度范围)

- 兼容ISO 10605和IEC 61000-4-2 ESD标准

- 支持Power-over-Coax(PoC)应用

- MIPI DPHY v1.2/CSI-2 v1.3兼容

- 自适应接收均衡和超低延迟控制路径

- 独特DIE-ID提供防伪保护

二、主要技术参数

电气特性

- 电源电压:

- VDD18:1.71V至1.89V

- VDD11:1.045V至1.155V(VDD_SEL=HIGH时)

- 工作温度:-40°C至+105°C环境温度

- 功耗:

- 典型总功耗:473mW(CSI-2 4数据通道+1时钟通道)

- 待机功耗:15mA(VDD_SEL=LOW时)

接口性能

- FPD-Link III接收:

- 支持单端同轴或屏蔽双绞线(STP)电缆

- 最大线速率:4.16Gbps

- 自适应均衡范围:0x00至0x3F

- CSI-2输出:

- 支持1/2/3/4数据通道配置

- 每通道数据速率:400Mbps/800Mbps/1.5Gbps/1.6Gbps

- 支持最多4个虚拟通道

三、典型应用场景

DS90UB638-Q1专为以下汽车应用优化:

- ADAS系统:

- 前视摄像头(FC)

- 环视系统(SVS)

- 后视摄像头(RVC)

- 驾驶员监控系统(DMS)

- 自动驾驶系统:

- 卫星雷达和激光雷达模块

- ToF和激光雷达传感器模块

- 其他汽车视觉应用:

- 电子后视镜显示

- 车载监控系统

四、功能架构解析

接收通道设计

器件采用自适应均衡技术,可自动补偿电缆损耗特性,无需额外编程。接收端包含:

- CDR(时钟数据恢复)电路

- FPD-Link III解码器

- 自适应均衡器(AEQ)

- 数据缓冲FIFO

CSI-2传输层

支持MIPI CSI-2协议的所有关键特性:

- 短包和长包格式

- 8位字长

- 虚拟通道交织

- 帧开始/结束、行开始/结束特殊包

- 16位CRC校验

控制通道

集成双向控制通道(BCC)提供:

- I2C通信(支持Fast-mode Plus达1Mbps)

- GPIO控制(最多7个可编程GPIO)

- 帧同步信号传输

五、关键设计考虑

1. 电源管理

- 电源时序要求:PDB信号应在电源稳定后保持低电平,待所有电源达到最小要求电平后再拉高

- VDD_SEL配置:

- LOW:使用内部1.1V LDO

- HIGH:使用外部1.1V电源

2. 布局建议

- 电源去耦:

- VDD18:推荐0.1-0.01μF+最小4.7μF电容

- VDD11:需10μF共享电容(VDD_SEL=HIGH时)

- 接地:中心DAP焊盘必须连接到地平面

3. 信号完整性

- 差分对走线长度匹配:±50mil以内

- 阻抗控制:

- 单端:50Ω

- 差分:100Ω

- CSI-2信号:

- 保持对称布线

- 避免穿越电源分割区域

六、寄存器配置指南

基本初始化流程

- 设置I2C器件地址(寄存器0x00)

- 配置GPIO功能(寄存器0x10-0x16)

- 使能接收端口(寄存器0x0C)

- 设置CSI-2输出模式(寄存器0x33)

- 配置FPD-Link III模式(寄存器0x6D)

关键寄存器功能

- AEQ控制:寄存器0xD2-D5控制自适应均衡算法

- BIST模式:通过寄存器0xB3启用内置自测试

- 帧同步:寄存器0x18-0x1C配置内部帧同步生成

七、故障排查

常见问题及解决方案

- 无LOCK信号:

- 检查电缆连接和终端

- 验证参考时钟(23-26MHz)质量

- 检查电源电压和时序

- CSI-2数据错误:

- 验证线速率设置

- 检查PCB布局是否符合MIPI规范

- 使用BIST模式测试链路完整性

- 控制通道故障:

- 确认I2C地址配置

- 检查上拉电阻(2-4.7kΩ)

- 验证BC_FREQ_SELECT设置

-

汽车级FPD-Link III解串器DS90UB914A-Q1的深度剖析与应用指南2025-12-23 616

-

DS90UB940-Q1:1080p FPD-Link III 至 CSI-2 解串器的全面解析2025-12-22 709

-

汽车级FPD - Link III解串器DS90UB934 - Q1:技术详解与应用指南2025-12-19 529

-

DS90UB940N-Q1:高性能 FPD-Link III 转 CSI-2 解串器解析2025-12-18 618

-

汽车ADAS应用利器:DS90UB638-Q1解串器深度解析2025-12-16 523

-

DS90UB926Q-Q1 5至85MHz 24位彩色FPD-link III解串器数据表2024-07-05 544

-

DS90UB638-Q1 FPD-link III 4.16Gbps单输入解串器数据表2024-07-03 705

-

DS90UB962-Q1四路3Gbps FPD-link III解串器集线器数据表2024-06-29 606

-

DS90UB934-Q1 12位100MHz FPD-link III解串器数据表2024-06-24 532

-

DS90UB954-Q1双路4.16Gbps、MIPI CSI-2输出、FPD-link III解串器集线器数据表2024-06-19 848

-

DS90UB947-Q1,一款OpenLDI到FPD-Link III桥接器件详解 pdf2018-02-05 3007

全部0条评论

快来发表一下你的评论吧 !