德州仪器ADC34RF52:14位1.5GSPS射频采样ADC的技术解析

描述

Texas Instruments ADC34RF52 14位RF采样模数转换器(ADC)是一款单核14位、1.5GSPS、四通道ADC,支持RF采样,输入频率高达2.5GHz。该设计的噪声频谱密度为-153dBFS/Hz,最大限度地提高了信噪比(SNR)。通过使用额外的内部ADC和片上信号平均,噪声密度可提高到-156dBFS/Hz。

数据手册:*附件:Texas Instruments ADC34RF52 14位RF采样ADC数据手册.pdf

每个ADC通道都可以通过48位NCO连接到双频带数字下变频器(DDC)。此功能支持相位相干跳频,通过使用GPIO引脚进行NCO频率控制,可在不到1µs的时间内实现。Texas Instruments ADC34RF52支持具有子类1确定性延迟的JESD204B串行数据接口,使用高达13Gbps的数据速率。每个ADC通道只有2条串行器/解串器通道。高能效ADC架构在1.5GSPS时的功耗为0.73W/ch,并以较低的采样率提供功率调节。

特性

- 14位四通道1.5GSPS ADC

- 噪声频谱密度

- 未求平均值时为-153dBFS/Hz

- 取2次平均值时为-156dBFS/Hz

- 单核(非交错)ADC架构

- 孔径抖动:50fs

- 低近端残留相位噪声:-133dBc/Hz(10kHz偏移时)

- 频谱性能(f

IN=900MHz,-4dBFS)- 2x内部平均

- SNR:65.2 dBFS

- SFDR HD2/3:74dBc

- SFDR最严重毛刺:90dBFS

- 满量程输入:1.0/1.1Vpp(1/1.8dBm)

- 全功率输入带宽(-3dB):1.6GHz

- JESD204B串行数据接口

- 最大通道速率:13Gbps

- 支持子类1确定性延迟

- 数字下变频器

- 每个ADC通道最多两个DDC

- 复杂输出:4x至128x抽取

- 48位NCO相位相干跳频

- 快速跳频:<1μs

- 功耗:0.73W/通道(1xAVG)

- 电源:1.8V、1.2V

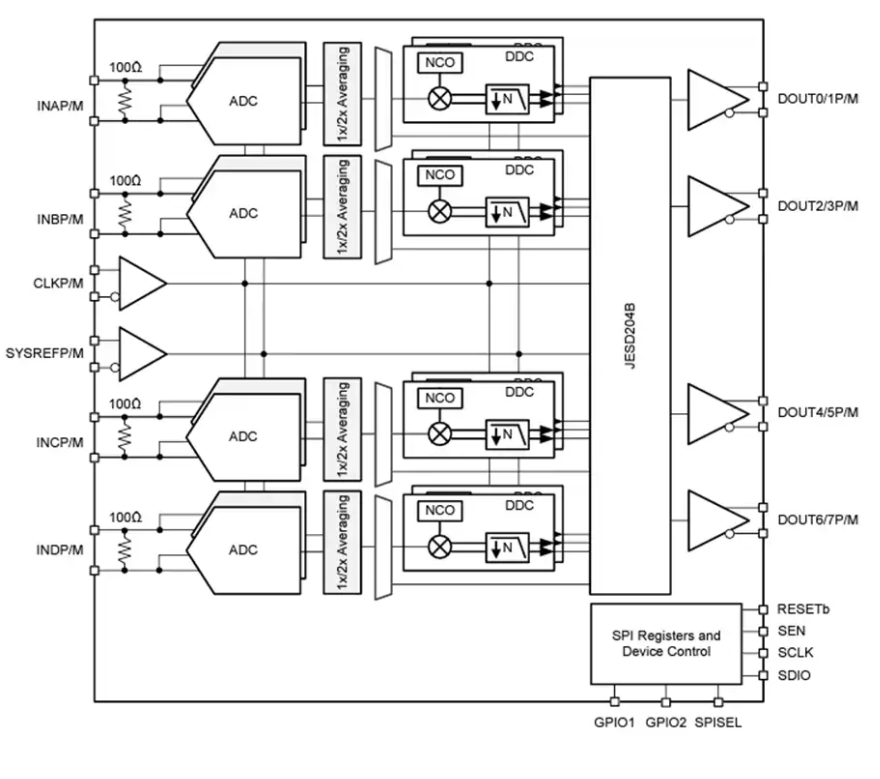

功能框图

德州仪器ADC34RF52:14位1.5GSPS射频采样ADC的技术解析

一、产品概述

德州仪器(TI)的ADC34RF52是一款高性能四通道14位1.5GSPS射频采样模数转换器,采用单核(非交织)ADC架构,专为直接射频采样应用设计。该器件具有出色的噪声性能(-153dBFS/Hz噪声谱密度)和低残余相位噪声(-133dBc/Hz@10kHz偏移),特别适合雷达、频谱分析和软件定义无线电等高要求应用。

二、关键特性

1. 射频采样性能

- 14位分辨率,四通道1.5GSPS采样率

- 直接射频采样支持高达2.5GHz的输入频率

- 噪声谱密度:-153dBFS/Hz(无平均),-156dBFS/Hz(2倍平均)

- 孔径抖动:50fs

- 全功率输入带宽:1.6GHz(-3dB)

- 输入满量程:1.0/1.1Vpp(1/1.8dBm)

2. 数字处理功能

- 片上数字下变频器(DDC) :每通道最多两个DDC

- 复数输出:支持4x至128x抽取

- 48位NCO:支持相位相干频率跳变

- 快速频率跳变:<1μs切换时间

3. 接口与功耗

- JESD204B串行数据接口:最高13Gbps通道速率

- 功耗:0.73W/通道(1x平均模式)

- 电源电压:1.8V和1.2V

三、应用领域

ADC34RF52特别适合以下应用场景:

- 相控阵雷达系统

- 频谱分析仪

- 软件定义无线电(SDR)

- 电子战系统

- 高速数字化仪

- 通信基础设施

四、架构与功能详解

1. 模拟输入设计

ADC34RF52采用非缓冲模拟输入设计以降低功耗,标称差分输入阻抗为100Ω。器件提供了两种内部ADC核心配置选项:

- 单ADC模式:标准工作模式,功耗最低

- 双ADC平均模式:启用额外ADC核心进行数字平均,改善噪声性能

输入带宽和满量程范围可通过SPI寄存器配置,支持100Ω或50Ω差分终端匹配。

2. 时钟子系统

器件采用专为低残余相位噪声设计的时钟路径,需要专用低噪声电源供电。关键特性包括:

- 内部残余时钟相位噪声敏感度低

- 建议时钟幅度大于1Vpp以获得最佳性能

- 100Ω差分内部终端匹配

- 支持500MHz至1.5GHz输入时钟频率

3. 数字下变频器(DDC)

每个ADC通道可连接至双波段数字下变频器,主要特点:

- 支持复数抽取(80%通带带宽)和实数抽取(40%通带带宽)

- 抽取因子从4x到128x可编程

- 48位NCO支持精确频率调谐

- 提供20位输出模式以避免高抽取率下的量化噪声限制

4. JESD204B接口

支持JESD204B子类1确定性延迟,关键配置选项:

- 最多8个通道,最高13Gbps速率

- 支持多种LMFS配置模式

- 可编程测试模式(PRBS、斜坡等)

- 支持通道重映射和输出多路复用

五、设计考虑因素

1. 前端设计建议

- 推荐使用1:2或1:1巴伦变压器将单端RF输入转换为差分信号

- 巴伦输出应通过100pF电容AC耦合至ADC输入

- 选择具有良好幅度(<2dB)和相位平衡(<2度)的巴伦

- 背对背巴伦配置通常可提供更好的SFDR性能

2. 时钟设计要点

- 时钟输入必须AC耦合至器件

- 需要低抖动(<50fs)时钟源以实现额定SNR性能

- 建议使用带通滤波器减少宽带时钟噪声

- 对于多器件系统,推荐使用LMK04828/32系列时钟发生器

3. 电源设计

ADC34RF52需要四种电源:

- AVDD18、AVDD12和CLKVDD:为模拟和时钟电路供电

- DVDD:为数字逻辑和JESD204B接口供电

推荐采用两级调节架构:

- 高效率开关稳压器作为第一级

- 低噪声LDO(如TPS7A8400)作为第二级

六、典型应用配置

宽带射频采样接收机设计

- 输入信号路径:

- 使用适当带限滤波器抑制接收信号中的不需要频率

- 采用1:2或1:1巴伦转换为差分信号

- 100pF AC耦合电容

- 时钟系统:

- 低抖动时钟发生器(如LMK04832)

- 带通滤波去除宽带噪声

- 数字接口:

- 配置JESD204B接口参数(LMFS模式)

- 实现与FPGA的可靠数据连接

七、性能表现

在典型工作条件下(FS=1.5GSPS,FIN=900MHz):

- SNR:65.2dBFS(1x平均),67.9dBFS(2x平均)

- SFDR:74dBc(HD2,3),90dBFS(最差杂散)

- IMD3:81dBFS(双音测试)

-

德州仪器ADC32RF52:高性能RF采样数据转换器解析2026-01-26 399

-

ADC12D500RF 12 位中高速 RF 采样 ADC 技术文档总结2025-11-18 881

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1473

-

ADC34RF52 四通道 14 位 1.5GSPS 射频采样模数转换器(ADC)技术文档总结2025-10-29 858

-

ADC32RF52 射频采样模数转换器技术总结2025-10-28 772

-

ADC34RF72 四通道、16位、1.5GSPS、超低噪声频谱密度(NSD)射频采样接收器技术手册2025-10-22 1000

-

高性能射频采样ADC:ADC32RF5x系列技术解析2025-08-15 1433

-

德州仪器ADC34RF55:14位3GSPS RF采样ADC技术解析2025-08-14 1585

-

ADC32RF42双通道14位1.5GSPS模数转换器数据表2024-07-22 562

-

ADC34RF55四通道14位3GSPS射频采样数据转换器数据表2024-07-15 626

-

德州仪器推出业界首款具备缓冲输入的12位1GSPS ADC2009-11-04 1529

全部0条评论

快来发表一下你的评论吧 !