如何提高磁致伸缩位移传感器采样电路信噪比

电子说

描述

下面是一套系统化、工程可实施的做法和思路,帮助提高磁致伸缩位移传感器(及其采样电路)的信噪比 SNR。我把方法分为硬件端(传感器到 ADC 的模拟链路)、数字端(采样/滤波/算法)、PCB/布局/机箱,以及测量验证四个部分,并提供关键公式和示例计算,便于大家实际应用与权衡。

关键概念

SNR(线性) = 信号 RMS / 噪声 RMS;以 dB 表示:SNR(dB) = 20·log10(signal/noise)。

平均(非相干噪声)提升:平均 N 此后 SNR 提高 10·log10(N) dB(因为噪声幅值随 √N 减小)。

热噪声电压谱密度:v_n = sqrt(4·k·T·R) (V/√Hz),k=1.38e-23,T≈300K。

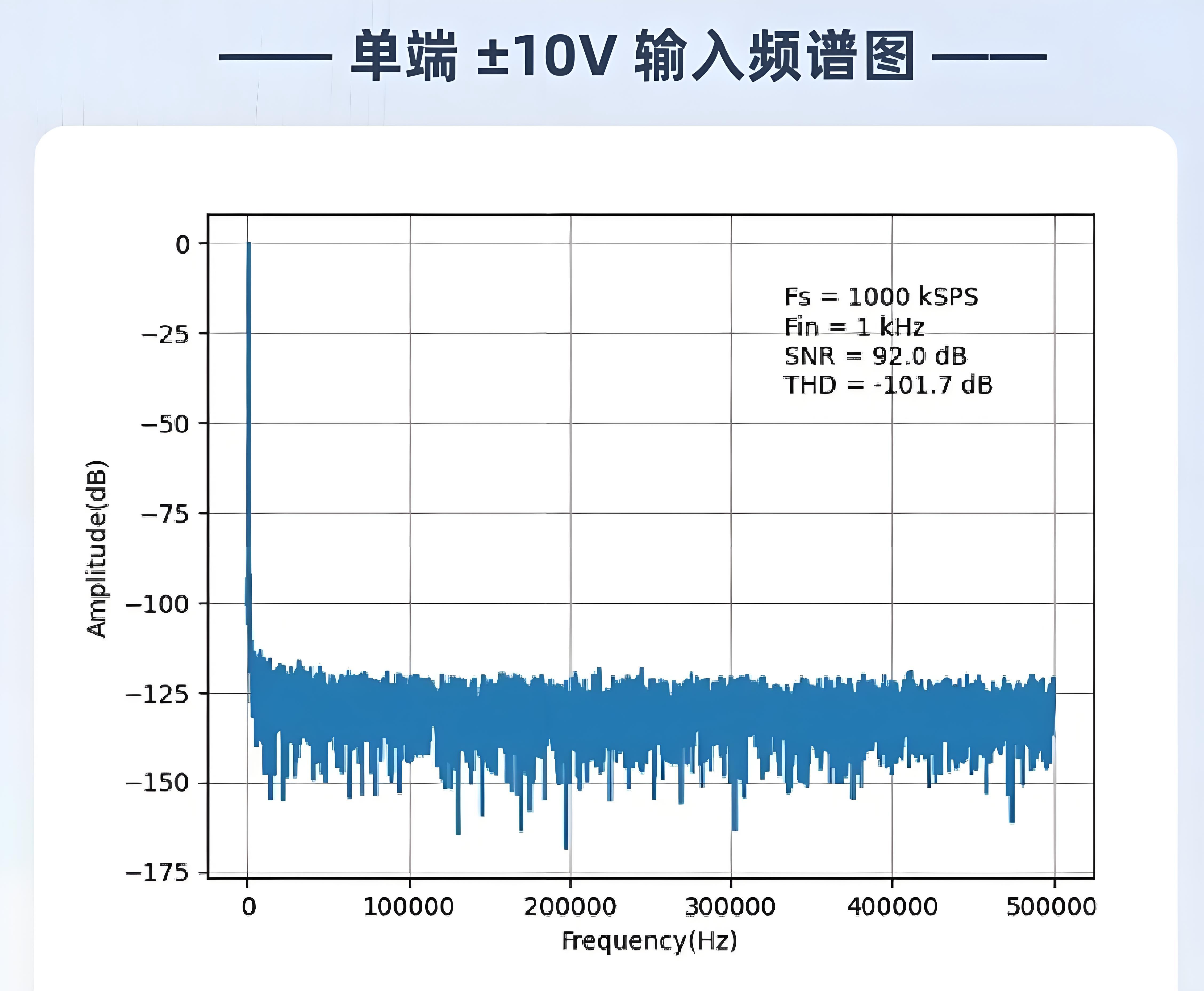

ADC 理论量化噪声:SNR_q ≈ 6.02·ENOB + 1.76 dB(ENOB = 有效位数)。

一、模拟前端

把信号做放大,尽量在 ADC 满量程附近工作

使用低噪声放大器(LNA)把磁致伸缩位移传感器输出放大到接近 ADC 的满量程(但不饱和)。放大量越大,后级噪声对整体影响越小。

选择输入噪声谱密度低的放大器(例如输入噪声 < 5 nV/√Hz 为佳;若 1/f 噪声重要,考虑斩波/零漂放大器)。

差分输入 & 仪表放大器

若磁致伸缩位移传感器/传输线可做差分,使用差分放大器或仪表放大器可以显著提高共模干扰抑制(CMRR)和抗干扰能力。

带宽限制(抗混叠 + 降低宽带噪声)

只放宽到你真正需要的带宽。噪声功率与带宽成正比,带宽减半噪声 RMS 减少约 √2。

在 ADC 前用有良好相位/增益特性的低通滤波器(LC、二阶或更高有源滤波)作为反混叠滤波器。

选择合适阻值以降低热噪声

热噪声与电阻成正比,尽量使用较小的源阻抗,或用紧耦合的放大器减小阻抗转换带来的噪声放大。

示例:R=10k 时噪声密度约 12.9 nV/√Hz(在 300K 下)。(可以参考:v_n = sqrt(4kTR))

优化 ADC 前端(采样保持、驱动)

若 ADC 是 SAR,确保驱动放大器有足够短的建立时间和低输出阻抗,避免采样时产生额外噪声/失真。

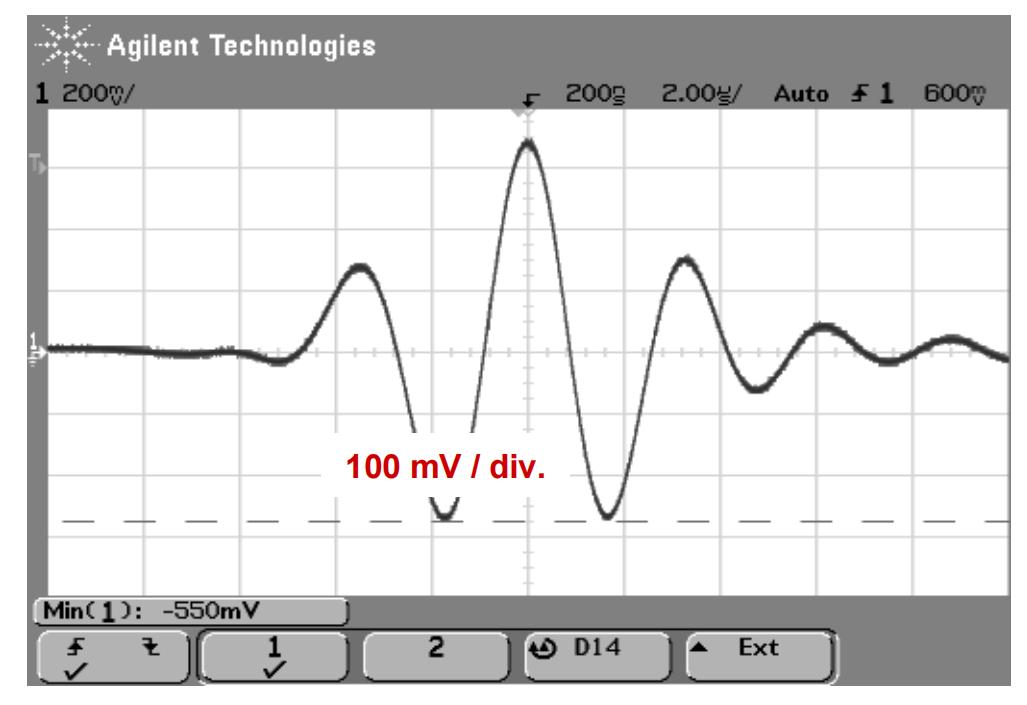

对高速 ADC,可加采样保持(S/H)或缓冲器,减小带宽需求与振铃。

使用同步检测 / 锁相放大(Lock-in)

如果你的信号有已知频率或脉冲(很多磁致伸缩传感器基于发射-回波/时域信号),用同步检测能把窄带信号从强噪声中提取出来,SNR 可大幅提升(等同窄带滤波 +相位相干增益)。

直流与低频噪声(1/f)处理

对低频或慢漂信号使用斩波/零漂放大器或进行周期性校准以抑制 1/f 噪声与漂移。

二、数字端(采样与处理)

提高采样率 + 过采样 + 数字低通滤波/降采样(decimation)

过采样可以把宽带量化噪声平均掉(并允许用数字滤波器实现更陡峭的带通/带阻),过采样率 N 带来 10·log10(N) dB 的噪声改善(通过集成/降采样实现)。

例如:过采样 16× 大致可获得 12 dB 左右的改善(理论)。

数字滤波器(FIR/IIR)与平均

选择合适窗函数的 FIR 能实现线性相位和陡峭截止,IIR 可节省运算。

窄带应用可采用带通或同步检测后低通滤波。

平均 vs 加权平均 vs 卡尔曼滤波

简单平均对非相干噪声很好;对时间变化信号,用指数平滑或卡尔曼滤波可以在降低噪声的同时保留动态响应。

抖动与时钟质量

对于窄脉冲/TOF(time-of-flight)测量,采样时钟抖动会引入噪声误差,选择低抖动时钟并优化 ADC 抖动性能。

校准/温度补偿

数字上做温度补偿、非线性校正和漂移补偿可以在长期和不同温度下提高“有效 SNR”(即有用信号的可用比率)。

三、PCB 布局 / 接地 / 护罩(细节决定成败)

模拟和数字分区(分层)

将模拟、数字供电与地分开,模拟地(AGND)和数字地(DGND)最终在单点相连(star ground)或通过 EMI 抑制阻抗连接。

走差分线 / 最小化环路面积

磁致伸缩位移传感器到放大器关键路径走短线路、使用屏蔽层,减小环路面积来抑制磁/电场耦合噪声。

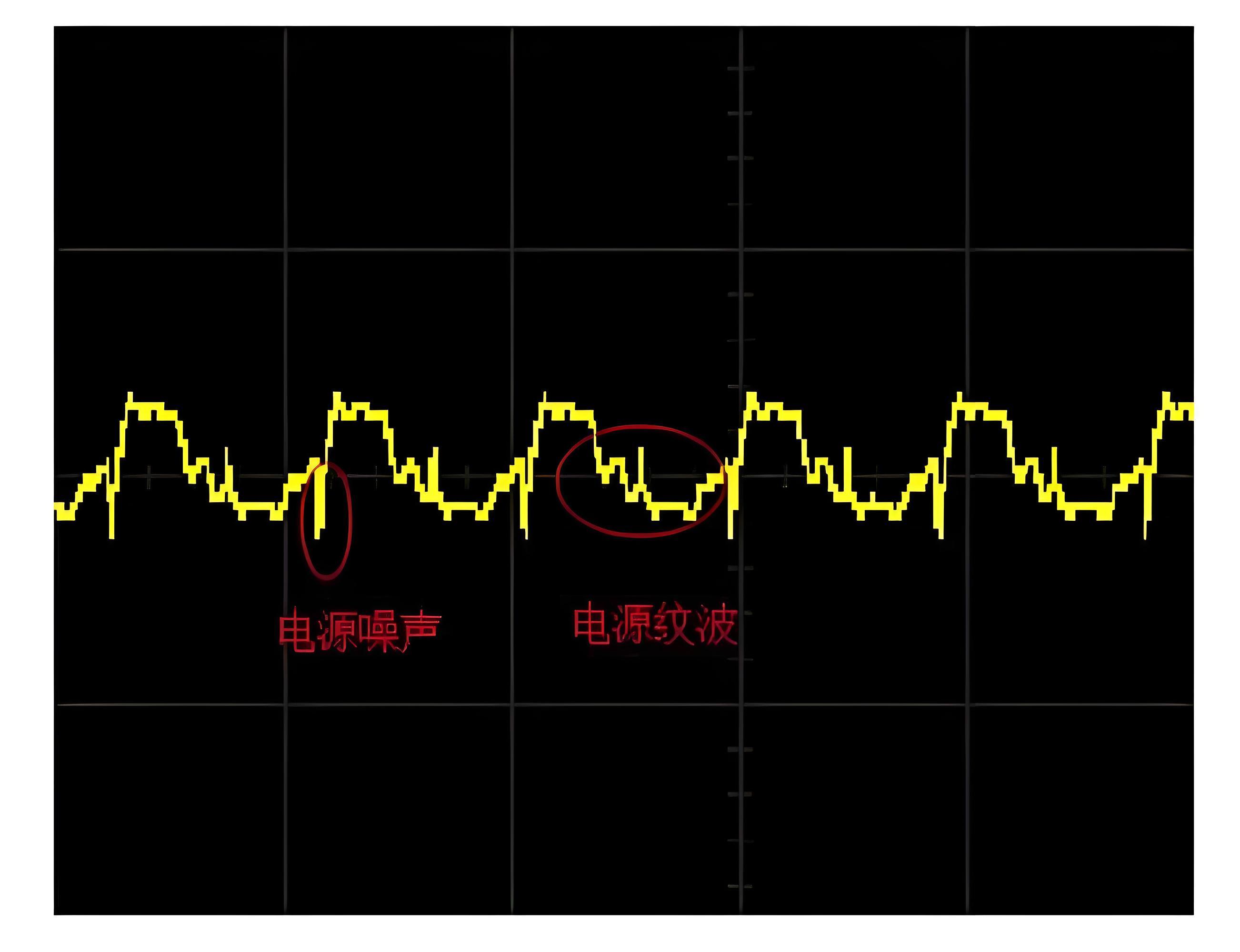

去耦与稳压

模拟放大器附近加低 ESR 电容、L/C 滤波,使用线性稳压器或低噪声 LDO。数字部分的开关噪声不要耦到模拟电源。

屏蔽与接地盒

金属屏蔽罩,感应信号线屏蔽以降低外部 EMI。屏蔽层与系统地的连接方式要谨慎(避免地环路)。

防浪涌与保护电路

输入端适当的 TVS、RC 滤波以减少带宽外高能干扰进入,注意保护电路不要显著提高源阻抗或引入额外噪声。

四、器件与规格选择(要点)

放大器:选择低输入噪声、电流噪声合适、带宽匹配信号带宽、若低频重要选择低 1/f 的零漂或斩波型放大器。

ADC:按带宽 vs 精度权衡:若带宽低、精度要高,选高分辨率 ΣΔ ADC(内置过采样+滤波);若需要高采样率且中等分辨率,选高速 SAR/PIPELINE。

参考电压:稳定、低噪声参考对 SNR 也很重要。

滤波器:有源二阶或更高阶滤波器可在模拟端减少噪声进入 ADC。

五、噪声估算与示例计算

热噪声密度示例:R = 10 kΩ 时,v_n ≈ sqrt(4·k·T·R) ≈ 12.9 nV/√Hz(T=300K)。

若系统带宽 B = 10 kHz,则该电阻在此带宽内的噪声 RMS ≈ 12.9 nV/√Hz × sqrt(10000) = 1.29 µV RMS。

若信号幅度为 100 mV RMS,则 SNR ≈ 20·log10(0.1 / 1.29e-6) ≈ 97.8 dB(只考虑该阻抗的热噪声,不含放大器/ADC 等其他噪声贡献)。

平均 100 次的数字平均:SNR 增益 10·log10(100) = 20 dB(理论上)。

六、测量与验证(实操步骤)

测噪声底噪:短接输入或接 0V,测 ADC 的噪声谱密度(用 FFT 做噪声谱),区分 1/f、白噪声、干扰线(50/60Hz)等。

增量法建立噪声预算:分别测放大器输出短接、传感器接入但不激励、ADC 输入短接等,分解每一段的噪声贡献。

时域统计:记录大量样本,计算 RMS 与直方图,确认是否有脉冲噪声或间歇性干扰。

频域分析:用谱分析定位干扰频率(开关电源、PWM、无线、工频等)。

EMC 环境测试:在实际安装环境下重复测量(屏蔽/地改动前后对比)。

七、优先级建议(做事顺序)

确定所需带宽与动态范围(决定 ADC 类型与放大倍数)。

设计低噪声前端:低噪声放大器 + 差分信号路径 + 反混叠滤波。

优化 PCB 布局、接地与电源去耦。

在数字域做过采样 / 同步检波 / 滤波。

测量并迭代:用谱仪/示波器/数据记录器验证每一步提升。

八、常见坑与避免

在模拟输入加过多的保护元件(大电阻、二极管)导致源阻抗增加,噪声上升或带宽受限。

把模拟地和数字地随意相连,导致数字开关噪声耦入模拟回路。

放大后 ADC 没有足够的分辨率(ENOB)来利用放大收益。

忽视时钟抖动问题(在对时间/相位敏感的应用尤其重要)。

审核编辑 黄宇

-

STM32的磁致伸缩智能位移传感器研究2025-03-20 1686

-

磁致伸缩位移传感器隔离电路2025-03-01 1251

-

磁致伸缩位移传感器工作原理及结构2024-06-19 4275

-

磁致伸缩位移传感器—精准的位移测量解决方案2024-04-23 1993

-

磁致伸缩位移传感器原理及特征2023-02-14 3314

-

磁致伸缩位移传感器运用了什么技术?2019-11-06 2080

-

磁致伸缩位移传感器原理及应用2019-10-01 10779

-

磁致伸缩液位计传感器的原理2018-12-27 2794

-

采用磁致伸缩技术的位移传感器2018-12-04 1811

-

磁致伸缩位移传感器的发展情况2016-06-24 4232

-

基于单片机的磁致伸缩位移传感器的应用2010-09-09 1137

-

磁致伸缩位移传感器综合知识2009-11-25 2365

-

磁致伸缩线性位移传感器的工作原理2009-05-14 2847

全部0条评论

快来发表一下你的评论吧 !