Texas Instruments DRA821x Jacinto™ 64位处理器技术解析

描述

Texas Instruments DRA821x Jacinto™ 64位处理器基于ARM®v8架构,并为带有云连接性的网关系统进行了优化。片上系统 (SoC) 设计通过集成降低了系统级成本和复杂性—尤其是系统MCU、功能安全和安保功能以及用于高速通信的以太网交换机。集成的诊断和功能安全特性是针对ASIL-D和SIL 3认证要求而设计的。PCIe控制器和支持TSN的千兆位以太网交换机可实现实时控制和低延迟通信。

数据手册:*附件:Texas Instruments DRA821x Jacinto™ 64位处理器数据手册.pdf

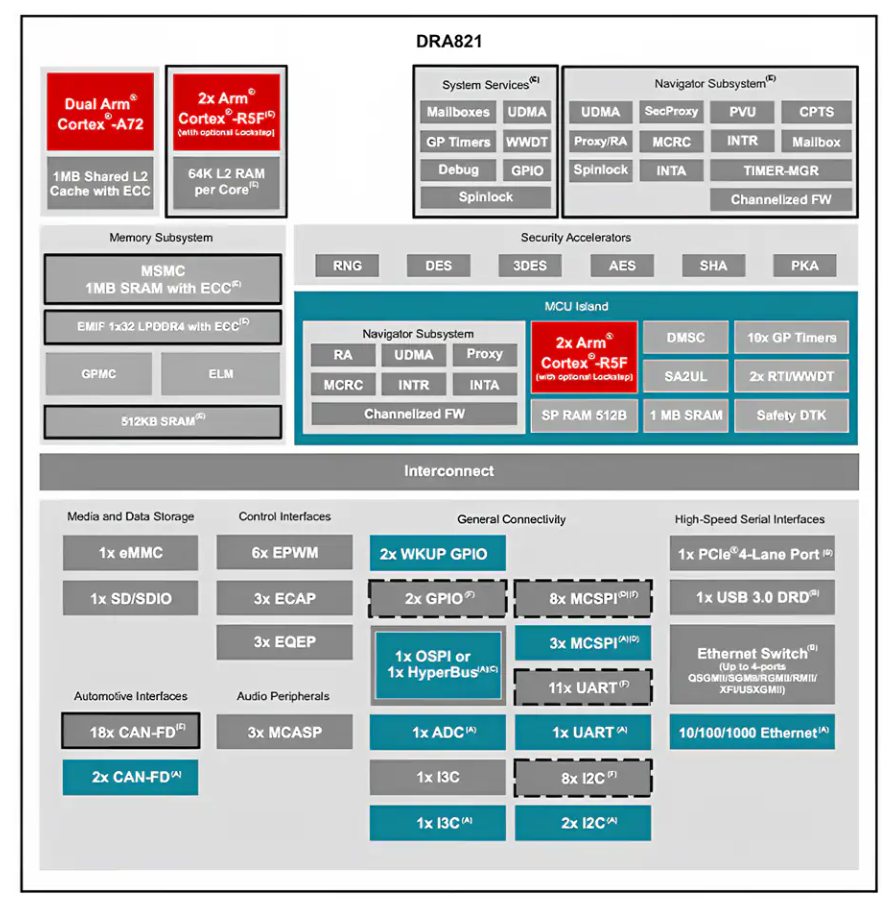

多达四个通用ARM^®^ Cortex®-R5F子系统,可以处理低级、时序关键型处理任务,从而使 ARM Cortex-A72内核不受高级和基于云的应用程序的阻碍。Jacinto DRA821x 处理器包括扩展MCU (eMCU) 域概念。该域是主域上处理器和外设的子集,旨在实现更高的功能安全性,例如ASIL-D/SIL-3。功能框图突出显示了eMCU中包含哪些IP。

特性

- 处理器内核:

- 双64 位ARM Cortex-A72微处理器子系统,最高可达2.0GHz、 24K DMIPS

- 每个双核Cortex-A72集群1MB L2共享缓存

- 每个A72内核具有32KB L1数据缓存和48KB L1指令缓存

- 4个ARM Cortex-R5F MCU,运行频率高达1.0GHz,可选择锁步操作,整数运算能力为8K DMIPS

- 32K指令缓存、32K数据缓存、64K L2 TCM

- 两个Arm Cortex-R5F MCU,隔离式MCU子系统中

- 通用计算分区中的2个ARM Cortex-R5F MCU

- 双64 位ARM Cortex-A72微处理器子系统,最高可达2.0GHz、 24K DMIPS

- 内存子系统:

- 具备ECC和一致性的1MB片上L3 RAM

- ECC错误保护

- 共享一致缓存

- 支持内部DMA引擎

- 外部存储器接口 (EMIF) 模块带ECC

- 支持符合JESD209-4B规范的LPDDR4内存类型。(不支持字节模式LPDDR4内存或超过17排地址位的存储器)

- 支持数据速率高达3200MT/s

- 32位和16位数据总线,内嵌ECC总线高达12.8GB/s

- 通用存储器控制器 (GPMC)

- 主域中的512KB片上SRAM,受ECC保护

- 具备ECC和一致性的1MB片上L3 RAM

- 虚拟化

- ARM Cortex-A72中的Hypervisor支持

- 采用Arm Cortex-A72、Arm Cortex-R5F(具有隔离式安全MCU岛)的独立处理子系统

- IO虚拟化支持

- 外设虚拟化单元 (PVU),用于低延迟高带宽外设流量

- 支持多区域防火墙,用于内存和外设隔离

- 以太网、PCIe和DMA虚拟化支持

- 设备安全(在部分零件编号上)

- 安全运行时间支持的安全启动

- 客户可编程根密钥,高达RSA-4K或ECC-512

- 嵌入式硬件安全模块

- Crypto硬件加速器 – 带ECC、AES、SHA、RNG、DES和3DES的PKA

- 功能安全:

- 针对符合功能安全标准(针对部分零件编号):

- 开发用于功能安全应用

- 可提供文档,协助ISO 26262和IEC 61508功能安全系统设计(高达ASIL-D/SIL-3)

- 针对系统能力高达ASIL-D/SIL-3

- 为MCU域针对的硬件完整性高达ASIL-D/SIL-3

- 硬件完整性高达ASIL-D/SIL-3,用于主域的扩展MCU (EMCU) 部分

- 为主域的剩余部分针对的硬件完整性高达ASIL-B/SIL-2

- EMCU和主域其余部分之间提供FFI隔离

- 安全相关认证

- 符合ISO 26262和IEC 61508标准(已计划)

- 以Q1结尾的零件系列已符合AEC-Q100认证

- 针对符合功能安全标准(针对部分零件编号):

- 高速接口:

- 集成以太网TSN/AVB交换机支持最多4个 (DRA821U4) 或2个 (DRA821U2) 外部端口:

- 一个端口支持5Gb、10Gb USBGMII/XFI

- 所有端口均支持2.5Gb SGMII

- 所有端口均支持1Gb SGMII/RGMII

- DRA821U4:任何单端口均可支持QSGMII(使用所有四个内部端口)

- 非阻塞线速存储和转发交换机

- InterVLAN (Layer3) 路由支持

- 支持与IEEE 1588时间同步(附件D、E、E、F)

- TSN/AVB支持流量调度、整形

- 端口镜像功能,用于调试和诊断

- 警务和费率限制支持

- 安全MCU岛中有一个RGMII/RMII端口

- 集成以太网TSN/AVB交换机支持最多4个 (DRA821U4) 或2个 (DRA821U2) 外部端口:

- 一个PCI-Express Gen3控制器:

- 支持Gen1、 Gen2和 Gen3的操作,并具有自动协商功能

- 4个通道

- 一个USB 3.1 Gen1双重角色设备子系统:

- 支持Type-C切换

- 可独立配置为USB主机、USB外设或USB双角色器件

- 汽车接口

- 20个CAN-FD端口

- 12个通用异步接收器/发射器 (UART)

- 11个串行外设接口 (SPI)

- 1个8通道ADC

- 10个内部集成电路 (I2C™)

- 2个改进的内部集成电路 (I3C)

- 音频接口:

- 3个多通道音频串行端口 (MCASP) 模块

- 闪存接口:

- 嵌入式多媒体卡 (eMMC™ 5.1) 接口

- 支持高达HS400速度

- 嵌入式多媒体卡 (eMMC™ 5.1) 接口

- 一个安全数字3.0/安全数字输入输出3.0 (SD3.0/SDIO3.0) 接口

- 1个八通道SPI/Xccela™/HyperBus 内存控制器 (HBMC) 接口

- 16nm FinFET技术

- 17.2mm x 17.2mm、0.8mm脚距、IPC 3类PCB

功能框图

Texas Instruments DRA821x Jacinto™ 64位处理器技术解析

一、处理器概述

Texas Instruments的DRA821x Jacinto™处理器是基于Armv8 64位架构的汽车级处理器,专为需要云连接的网关系统优化设计。该SoC通过高度集成降低了系统级成本和复杂度,特别适合汽车网关、车身控制模块、V2X/V2V等应用场景。

二、关键特性

1. 处理器核心配置

- 双核Cortex-A72:主频最高2.0GHz,提供24K DMIPS性能

- 四核Cortex-R5F:主频最高1.0GHz,支持锁步模式

- 内存子系统:

- 1MB L3 RAM带ECC和一致性支持

- LPDDR4内存接口,支持3200 MT/s速率

- 512KB片上SRAM(MAIN域)

2. 安全与功能安全

- 支持硬件虚拟化(Hypervisor)

- 独立安全MCU岛设计

- 功能安全目标达ASIL-D/SIL-3认证要求

- 安全启动与运行时支持,支持客户可编程根密钥

3. 高速接口

- 集成以太网TSN/AVB交换机(支持4/2个外部端口)

- PCIe Gen3控制器(4通道)

- USB 3.1 Gen1双角色设备子系统

- 20个CAN-FD接口

三、应用领域

DRA821x系列处理器特别适合以下应用场景:

- 汽车电子:网关系统、车身控制模块、远程信息处理控制单元

- 工业自动化:工厂自动化网关、工业运输设备

- 通信设备:建筑自动化网关、V2X/V2V通信系统

四、封装与功耗

- 采用16nm FinFET工艺

- 17.2mm x 17.2mm FCBGA封装,0.8mm间距

- 支持多级电压域管理,包括:

- 核心电压:0.76-0.84V

- DDR接口电压:1.05-1.15V

- I/O电压:1.71-3.46V(根据接口类型)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

德州仪器AM68x Jacinto 8处理器技术解析2025-08-27 1359

-

DRA821 Jacinto™处理器数据表2024-08-01 495

-

到底64位处理器和32位处理器有什么区别呢?资料下载2021-04-25 2404

-

32位处理器的开发与8位处理器的开发有哪些明显的不同?2021-04-19 2646

-

32位处理器可以装64位系统吗 32位处理器能否装64位系统分析2020-06-28 4177

-

详细解析32位嵌入式处理器与8位处理器应用开发的不同之处2018-02-07 9288

-

32位嵌入式处理器与8位处理器应用开发的区别2015-09-22 2889

-

64位时代来临 Marvell 64位处理器强势应对2014-12-24 2405

-

新战局,解析64位处理器以及未来发展趋势2014-10-03 2079

-

从2014 MWC 看各大厂商比拼64位处理器2014-02-25 1456

-

Intel 32位处理器 ,Intel 32位处理器结构原理2010-03-26 2298

-

Mobile Athlon 64位处理器详解2009-12-18 1090

全部0条评论

快来发表一下你的评论吧 !