倾佳电子SiC MOSFET串扰Crosstalk效应深度解析与综合抑制策略研究报告

电子说

描述

倾佳电子SiC MOSFET串扰Crosstalk效应深度解析与综合抑制策略研究报告

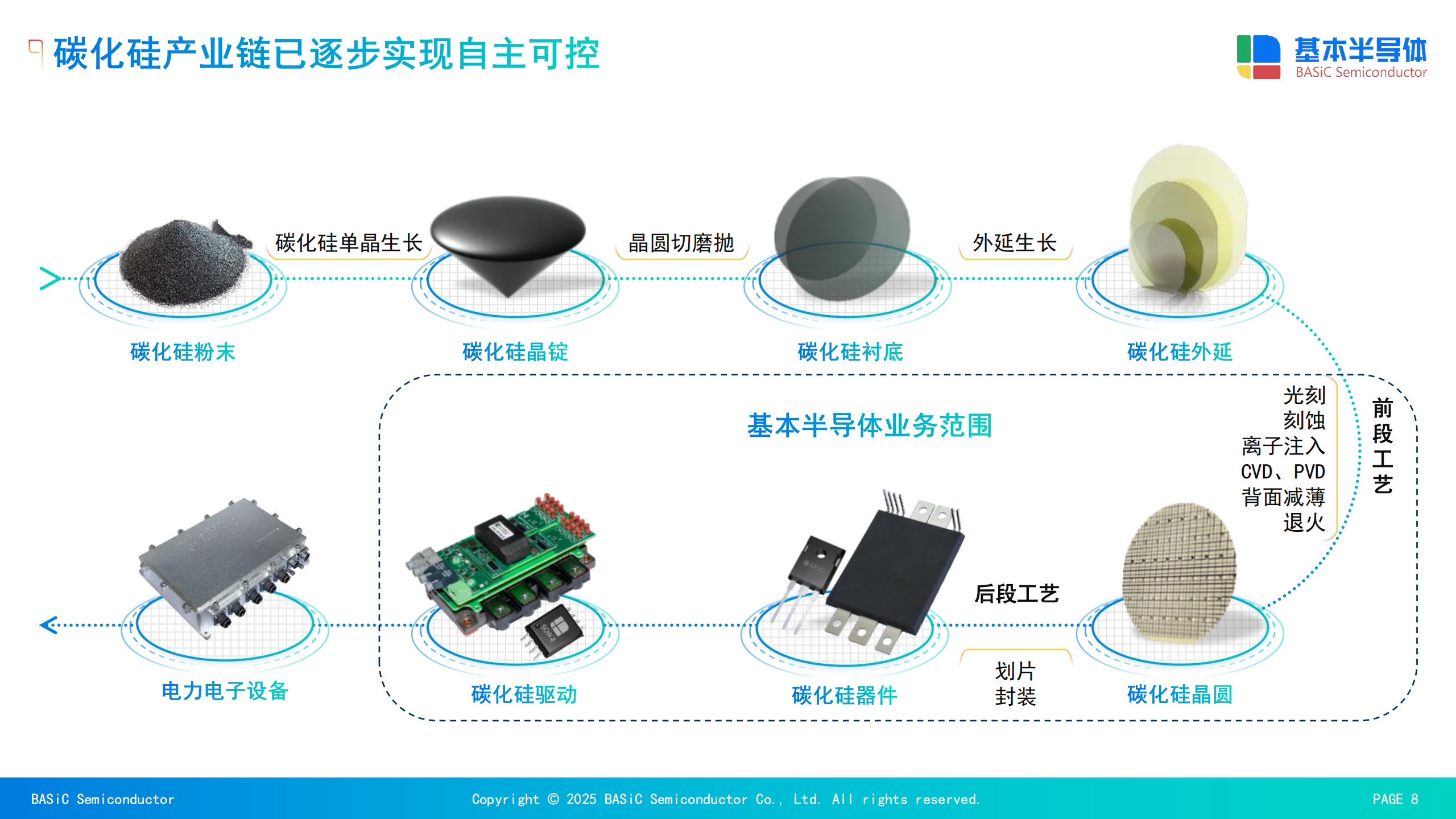

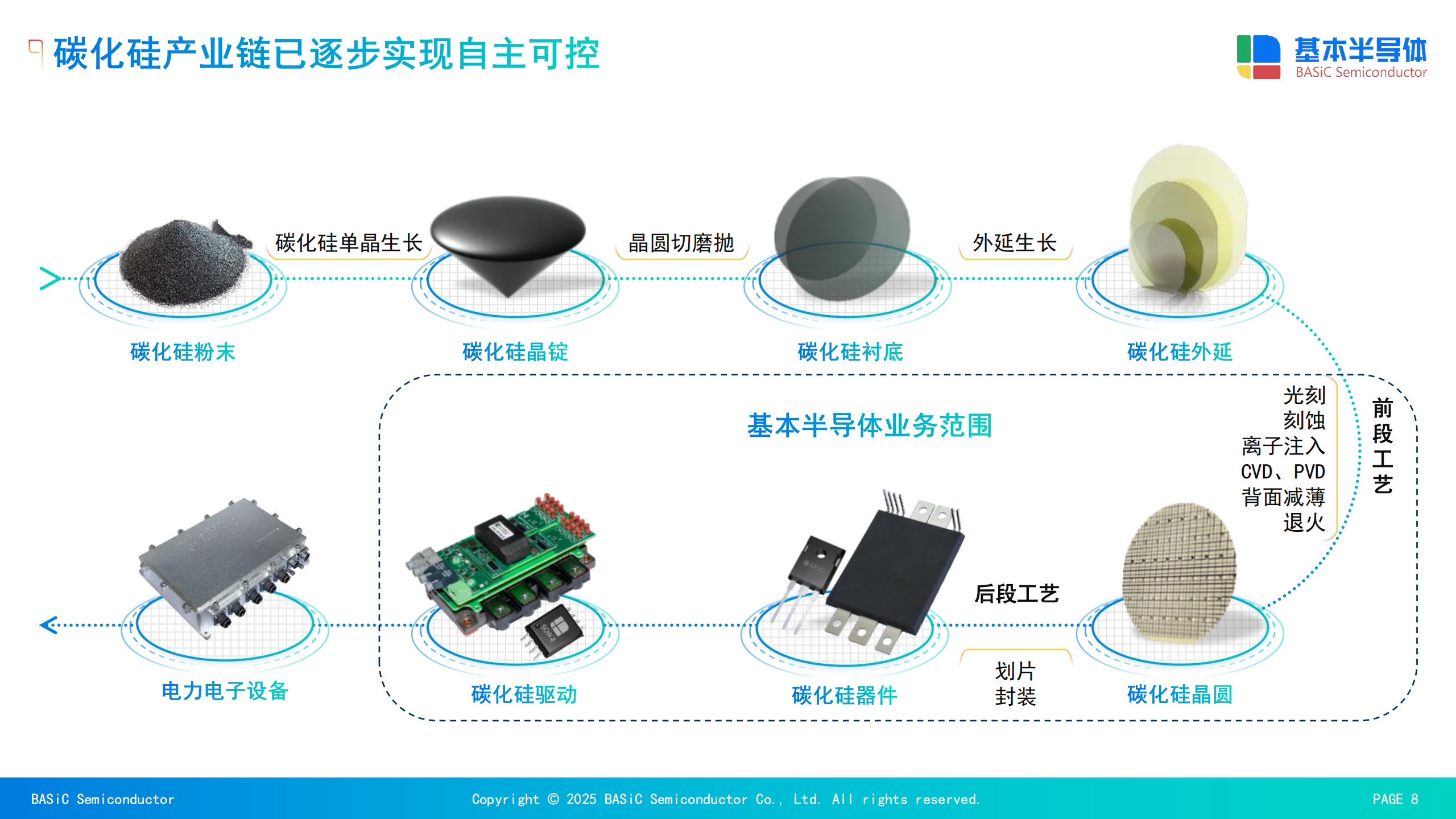

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 引言:碳化硅MOSFET在功率转换中的机遇与挑战

1.1 SiC MOSFET相较于Si IGBT及超结MOSFET的性能优势

碳化硅(SiC)作为第三代宽禁带(Wide-Bandgap, WBG)半导体材料,其卓越的物理特性使其在功率转换领域脱颖而出。相较于传统的硅(Si)基器件,如绝缘栅双极晶体管(IGBT)和超结(Super-junction)MOSFET,SiC MOSFET表现出显著的性能优势。SiC的禁带宽度约为3.26 eV,远大于Si的1.12 eV,这一特性使其具备高临界电场强度,约为Si的10倍 。这种高耐压能力允许器件在保持低导通电阻的同时,实现更高的电压等级,并能承受更高的工作温度(可达175°C至200°C),从而简化散热设计并提高功率密度 。

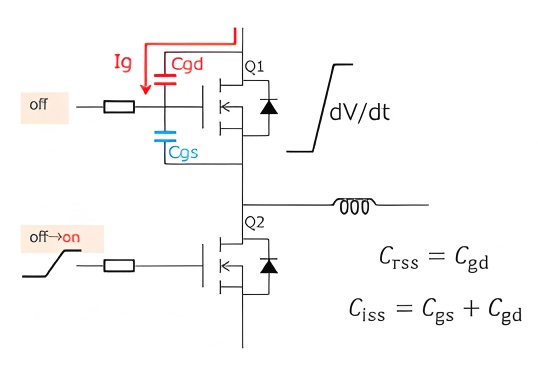

SiC MOSFET是单极型器件,其导电机制依赖于多数载流子,因此在关断时不会出现Si IGBT所固有的拖尾电流现象 。这一特性显著缩短了开关时间,将切换瞬态从数百纳秒甚至微秒级缩短至数十纳秒 。快速开关带来了极低的开关损耗(E_on和E_off),在相同测试条件下,SiC MOSFET的能耗损失可比Si IGBT低41%至78% 。此外,SiC器件的栅极电荷( Qg)和反向传输电容(Crss/Cgd)远低于Si器件,进一步降低了开关能耗,并允许更高的开关频率,进而缩小无源元件如电感和电容的体积,最终实现系统的小型化和轻量化 。这些综合优势使SiC MOSFET成为电动汽车、可再生能源、数据中心和工业应用中高功率、高效率系统的关键使能技术 。

1.2 功率转换器中的半桥拓扑与串扰现象概述

半桥电路是构建各种功率转换拓扑的基础模块,广泛应用于同步整流、逆变器和全桥电路中 。然而,在硬开关半桥应用中,两个MOSFET(高侧和低侧)的快速开关会引发一个固有的挑战:串扰(Crosstalk)。串扰是一种寄生耦合现象,指当一个器件(称为“主动开关”)在进行开关动作时,其另一桥臂处于关断状态的器件(“被动开关”)的栅源电压( Vgs)会受到干扰,产生不期望的电压尖峰 。这种尖峰可能导致被动开关发生部分或完全的误导通(False Turn-on),即所谓的直通(Shoot-through),对系统性能和可靠性造成严重威胁 。

1.3 串扰问题为何在SiC MOSFET应用中变得尤为突出?

尽管串扰在任何半桥电路中都存在,但SiC MOSFET的固有特性使其问题尤为严重 。其根本原因在于器件的高速开关能力和较低的门槛电压( Vth)。

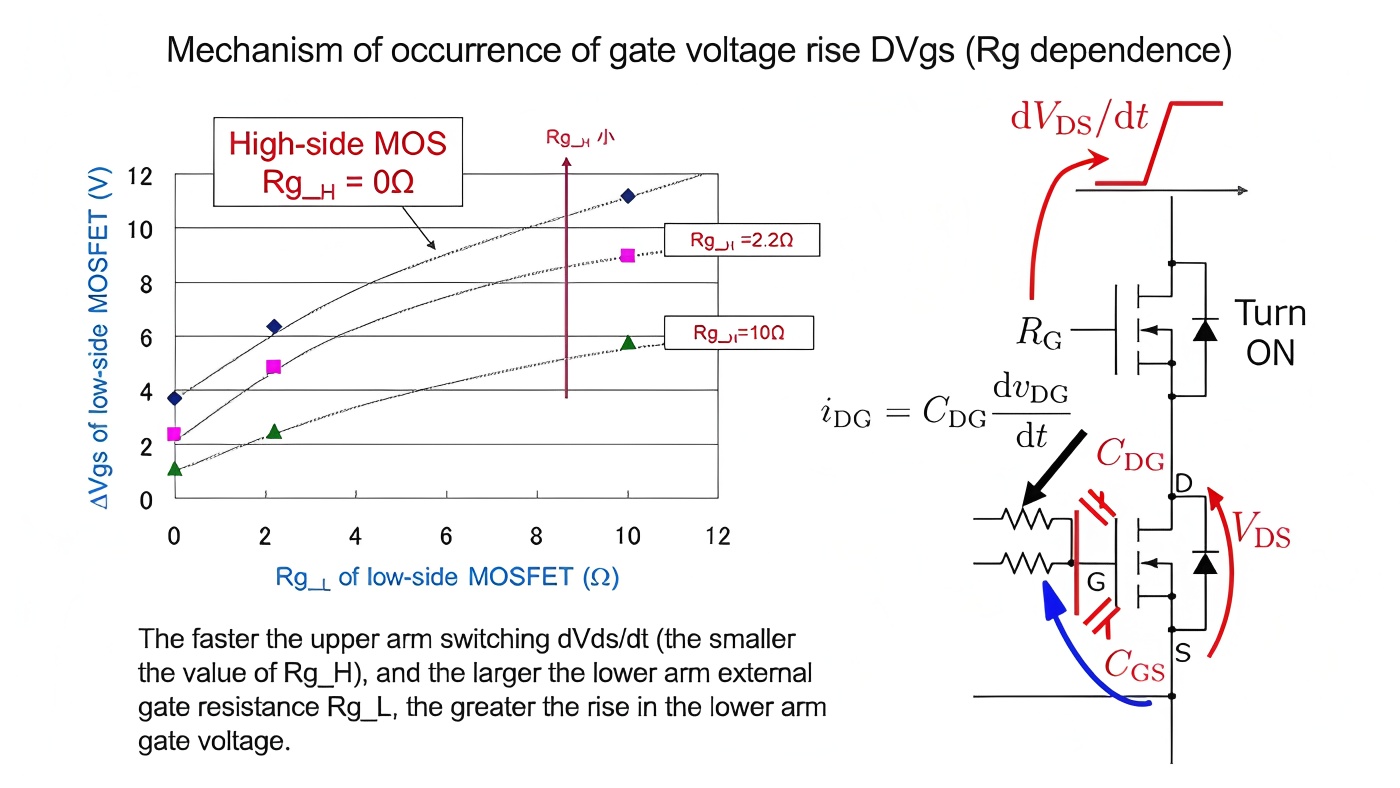

高dV/dt和dI/dt: SiC MOSFET极快的开关速度使得其漏源电压(Vds)和漏极电流(Id)在极短的时间内发生剧烈变化,产生极高的dV/dt和dI/dt 。这些高变化率是引发串扰的直接物理根源,因为它们会通过寄生电容和电感将高功率回路的能量耦合到门极回路 。

低Vth: 相比于硅基器件,SiC MOSFET的门槛电压相对较低,某些型号甚至低于1 V 。这使得栅极上任何微小的正向电压尖峰都可能轻松超过 Vth,引发被动开关的意外导通 。

串扰问题是SiC MOSFET核心优势——高速开关能力的直接“副作用”。它揭示了器件固有材料特性与应用环境(特别是寄生参数)之间的深层矛盾。快速开关带来的高dV/dt和dI/dt波形,通过主功率回路和栅极驱动回路中固有的寄生电容(Cgd)和共源电感(Lcs)耦合到被动开关的门极。由于SiC器件较低的门槛电压,这种耦合产生的电压尖峰极易引发误导通。因此,串扰问题并非一个孤立的现象,而是SiC材料优势在电路层面引发的连锁反应。任何有效的解决方案都必须从器件、驱动和PCB布局这三个层面进行系统性权衡和优化。

2. SiC MOSFET串扰机制的物理与电路分析

2.1 米勒效应:栅-漏电容的耦合作用

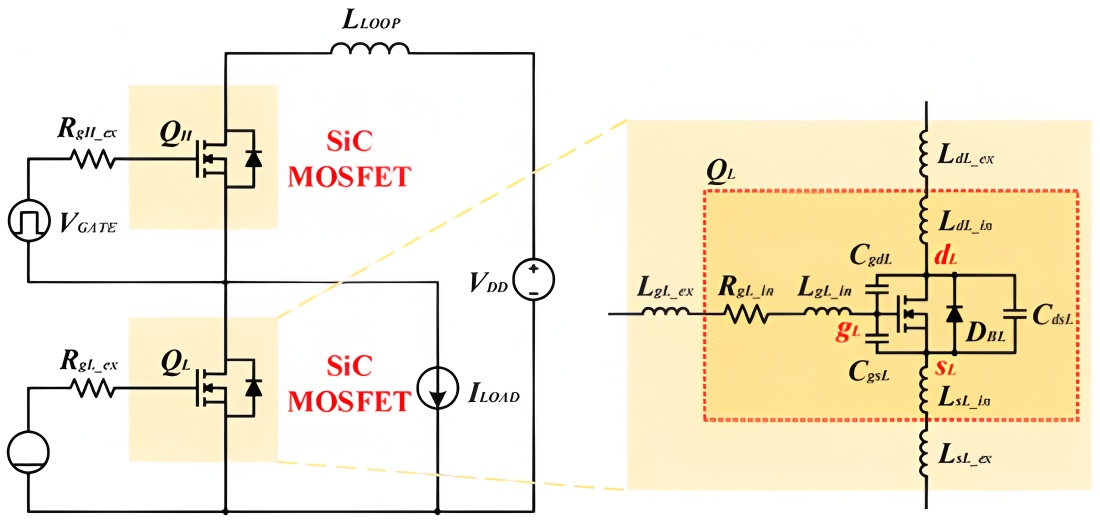

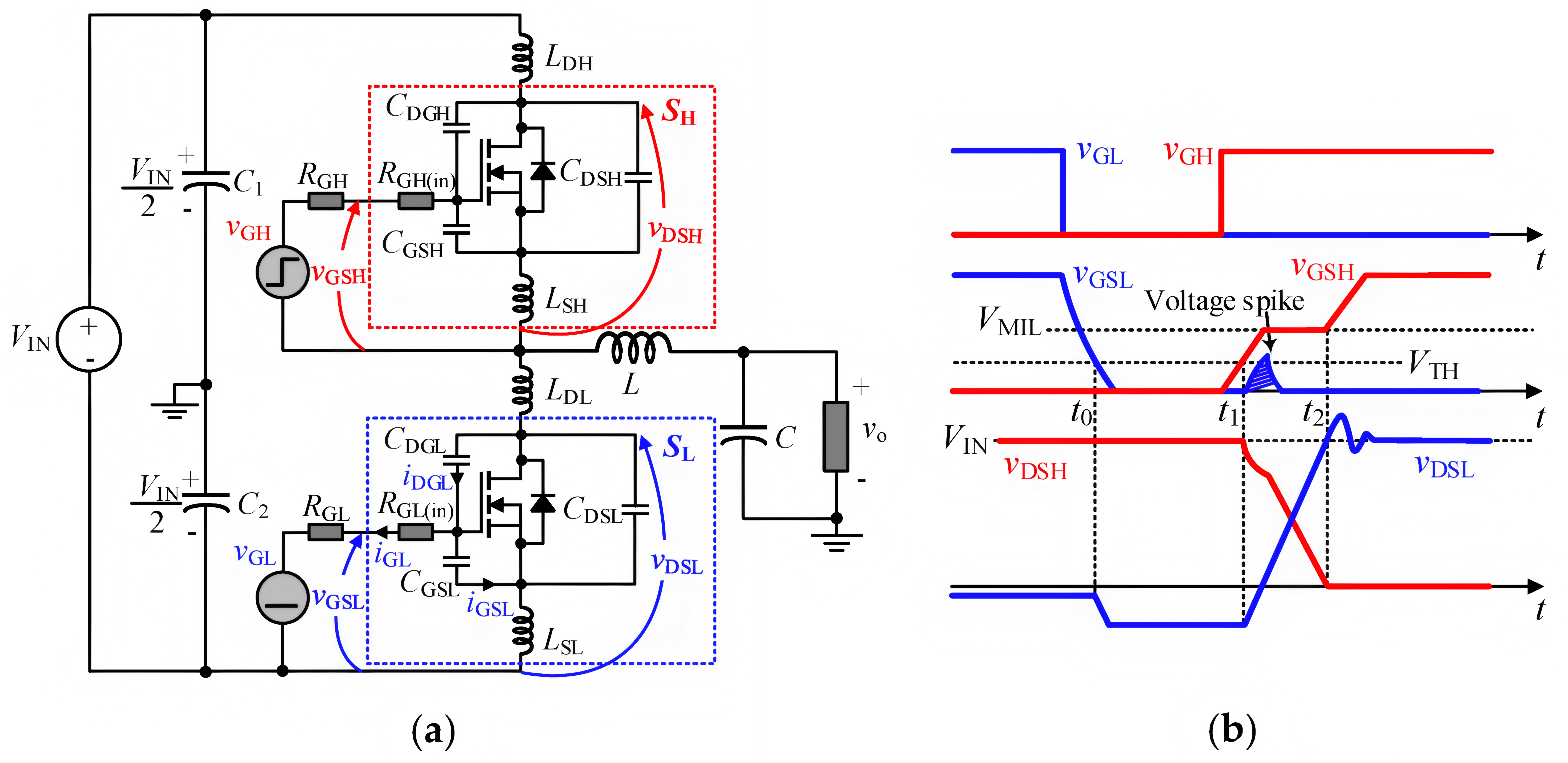

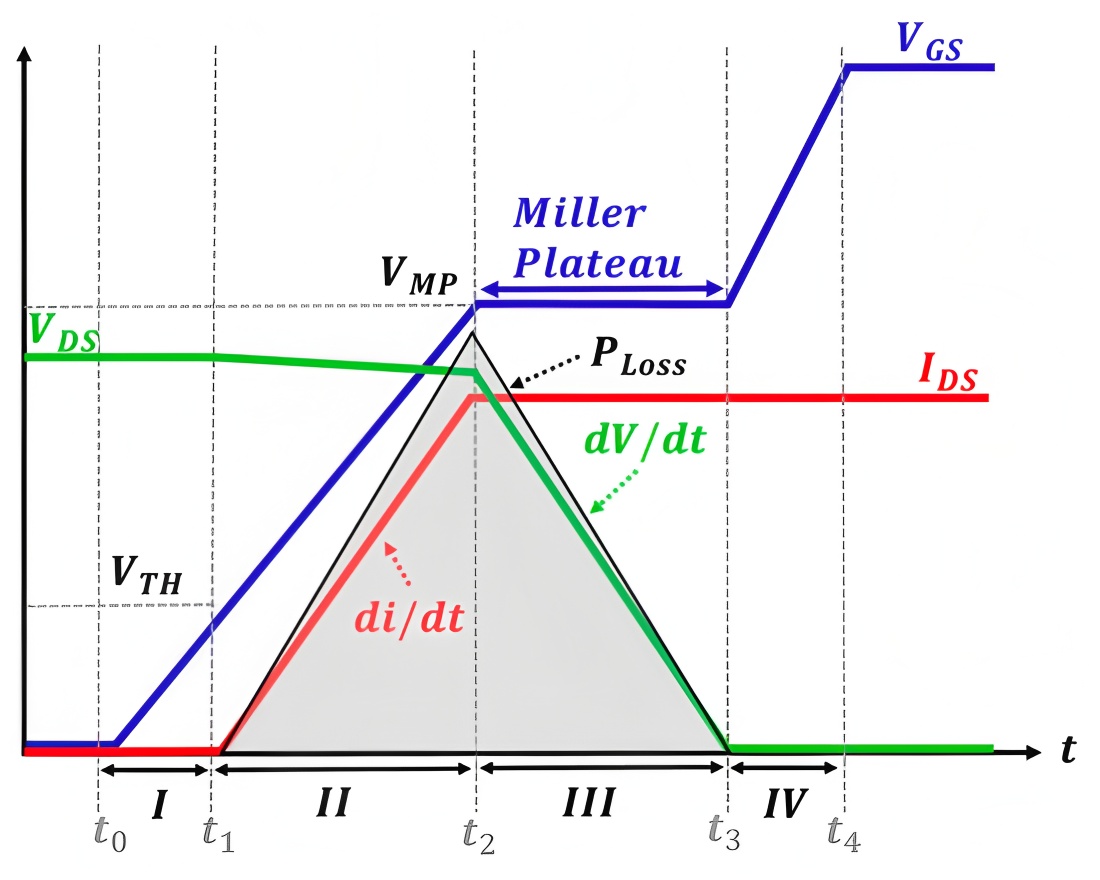

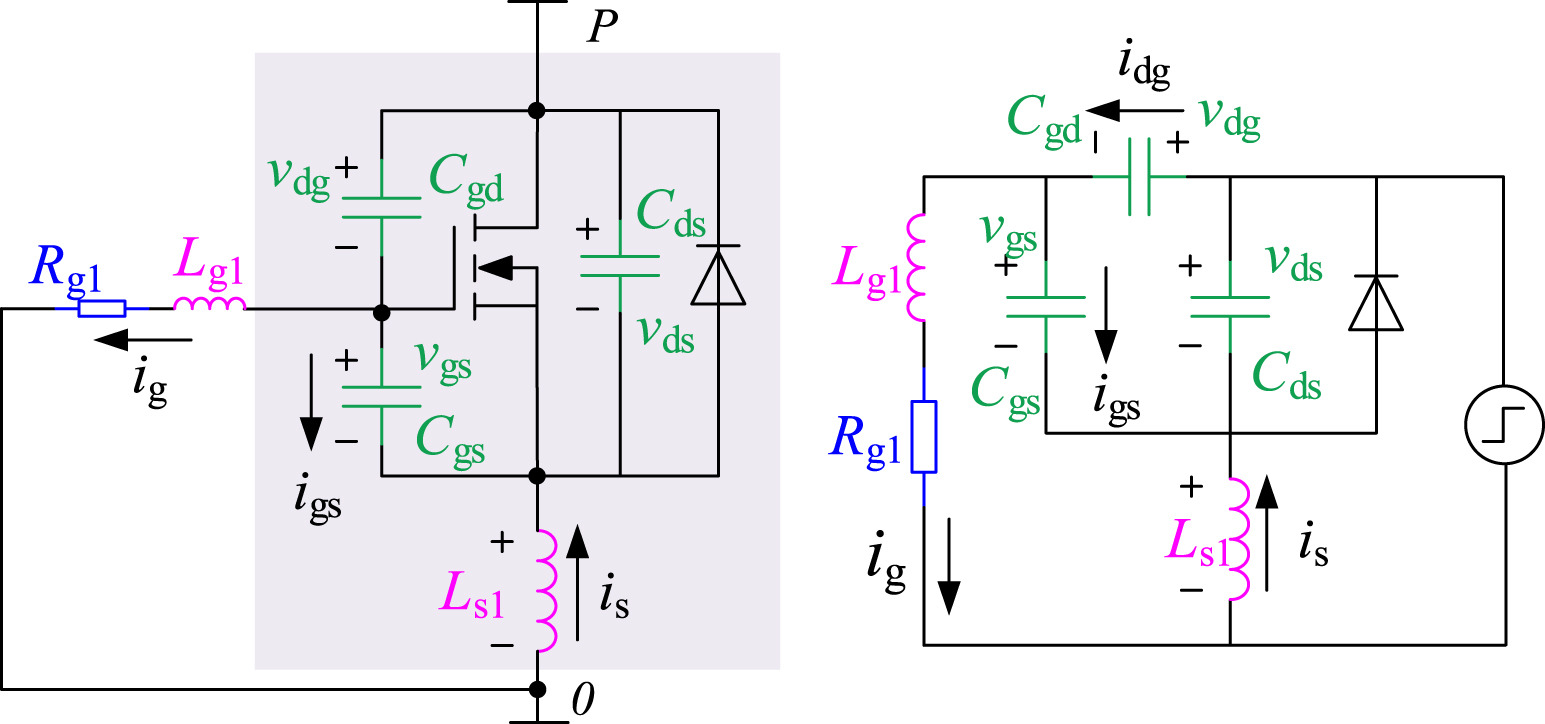

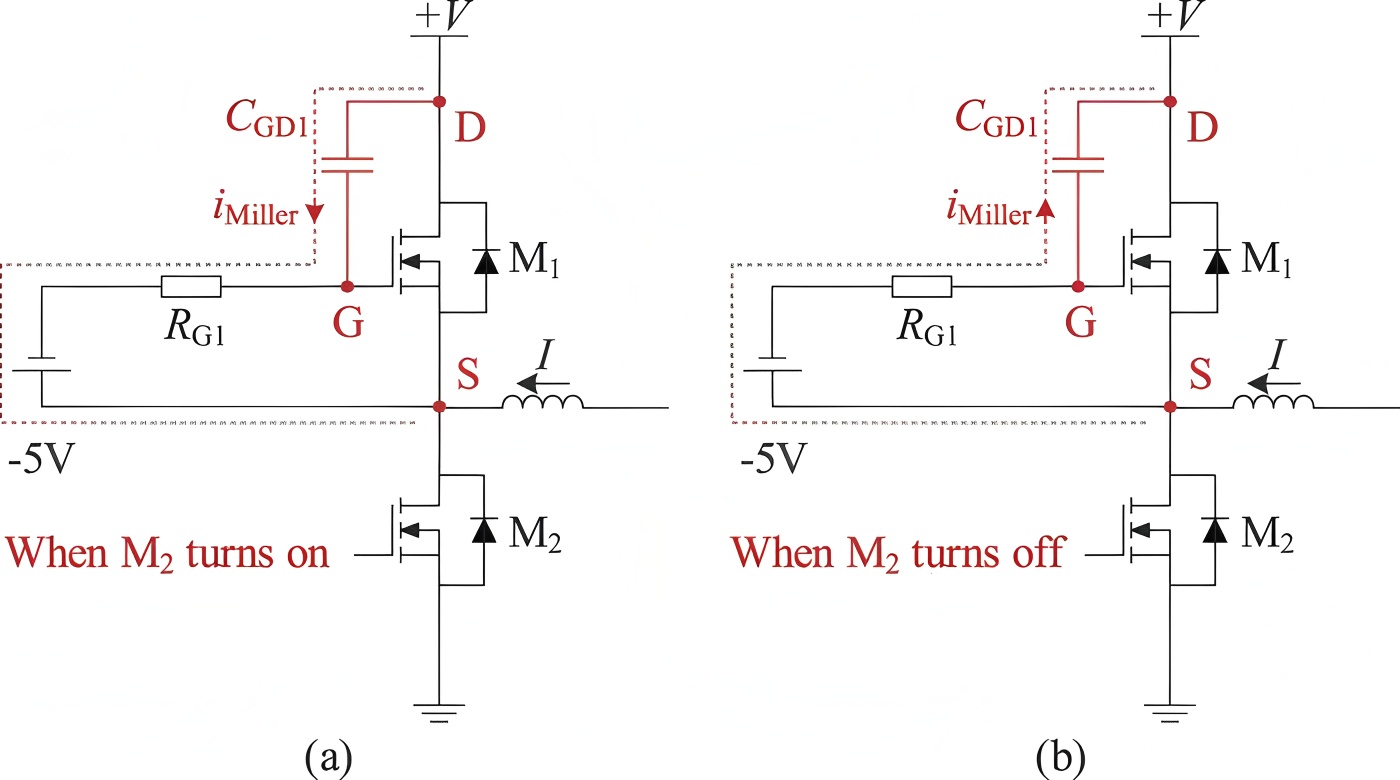

米勒效应是串扰最主要的物理机制之一。其核心在于MOSFET内部固有的栅漏寄生电容(Cgd)。在半桥拓扑中,当主动开关(例如,高侧MOSFET QH)导通时,被动开关(低侧MOSFET QL)的漏源电压(Vds)会从直流母线电压迅速下降到接近零伏 。反之,当Q_{H}关断时, Q_{L}的V_{ds}会从零迅速上升 。这种急剧的电压变化产生了高dV/dt。

高dV/dt通过C_{gd}在Q_{L}的栅极回路中产生一个位移电流(Displacement Current),其大小由I_{C_{gd}} = C_{gd} cdot (dV_{ds}/dt)决定。这个位移电流流经Q_{L}的栅极驱动回路中的栅极电阻(包括内部电阻R_{g,int}和外部电阻R_{g,ext})和寄生电感(Lg),在栅极上产生一个正向电压尖峰 。如果这个尖峰电压超过 Q_{L}的门槛电压V_{th},即使其门极驱动信号处于关断状态,Q_{L}也会被部分或完全误导通。这种误导通会造成上下桥臂短路,产生巨大的瞬时电流,这不仅会增加额外的开关损耗,还可能导致器件永久性损坏。与传统SiMOSFET不同,SiCMOSFET的米勒平台通常不是平坦的,这表明在开关过程中V_{gs}并非恒定,这与其较低的跨导(gm)特性相关 。这种非线性特性使得其动态行为的精确建模和控制更具挑战性 。

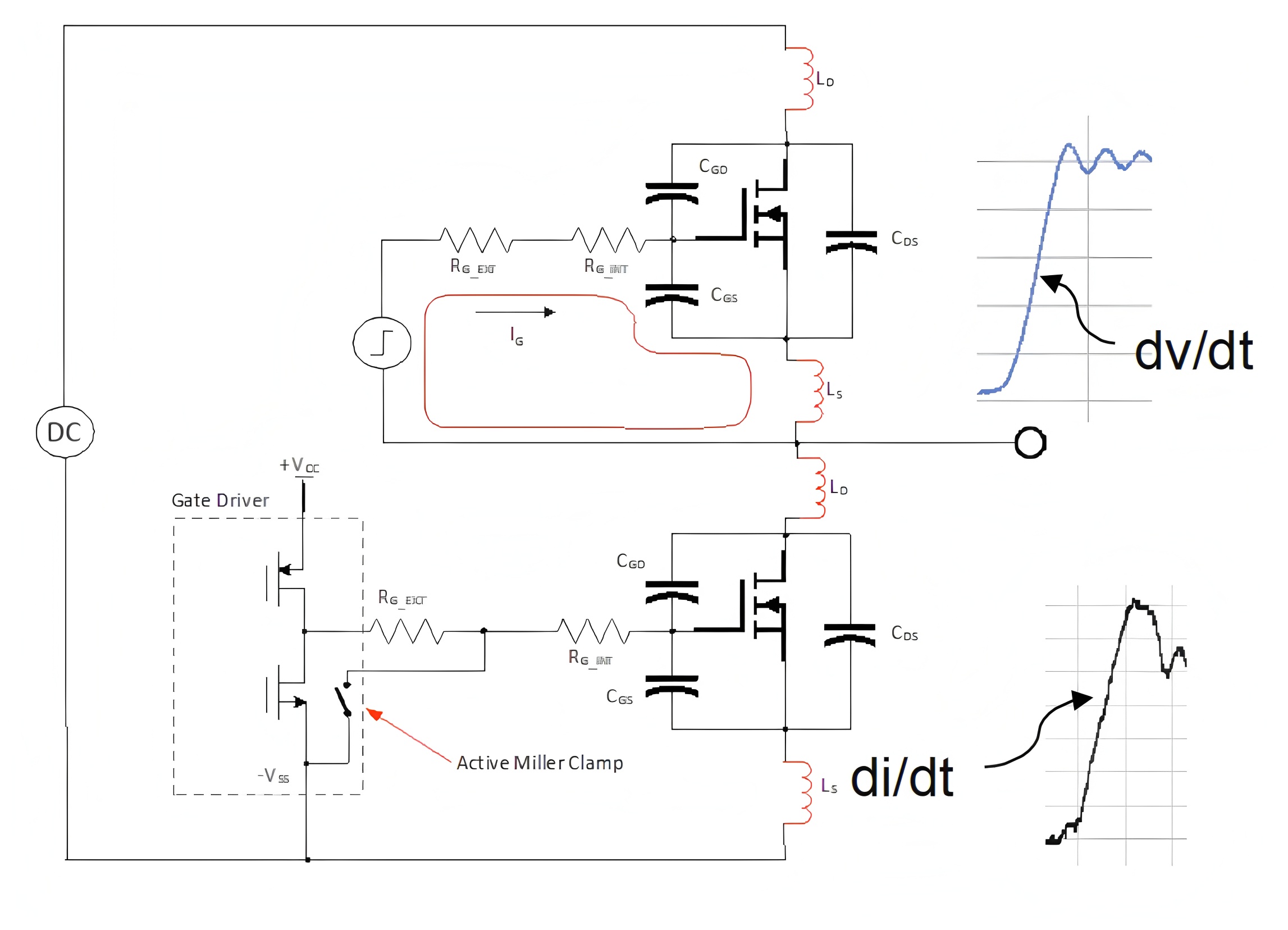

2.2 寄生共源电感(Lcs)的作用

除了米勒效应,寄生共源电感(Lcs)是另一个引发串扰的关键因素 。L_{cs}是MOSFET封装内部的源极引线键合电感和外部PCB布线中源极路径寄生电感的总和 。在半桥拓扑中,L_{cs}是门极驱动回路和主功率回路共用的寄生参数 。

L_{cs}的影响主要体现在两个方面:

导通瞬态: 当高侧MOSFET导通时,流经低侧MOSFET体二极管的电流急剧下降(dId/dt为负)。该电流流过低侧MOSFET的Lcs,在其上产生一个感应电压VLcs=−Lcs⋅(dId/dt) 。这个正向感应电压会叠加到被动开关(低侧MOSFET)的栅源电压上,与米勒效应共同作用,加剧正向串扰尖峰 。

关断瞬态: 在被动开关的关断瞬态,如果其漏极电流迅速减小(dId/dt为负),$L_{cs}$会产生一个正向感应电压,可能导致栅极电压被拉至负值 。这种负向串扰尖峰如果超过器件的负向安全电压等级( VGS,min),可能导致栅氧化层应力过大甚至永久性损伤 。

串扰的物理根源在于寄生参数将主功率回路的高速动态变化耦合至高阻抗的门极回路。PCB设计优化不仅需要减小回路面积,更应通过改变电流路径来物理性地对抗这些寄生耦合。例如,采用四引脚封装的开尔文源(Kelvin Source)连接,本质上就是为了物理性地将L_{cs}从门极驱动回路中移除,从根本上切断了电流耦合路径 。

表1. 串扰机制与主要影响因素对照表

| 机制 | 物理根源 | 触发时机 | 导致的主要现象 | 对系统影响 | 解决方案 | 参考文献 |

|---|---|---|---|---|---|---|

| 米勒效应 | 栅-漏电容(Cgd) | 主动开关导通/关断瞬态(dV/dt) | 正向电压尖峰,栅极电压振荡 | 误导通、直通、开关损耗增加、栅氧应力 | 负偏压、米勒钳位、有源驱动、PCB布局优化 | |

| 共源电感效应 | 共源电感(Lcs) | 主动开关导通/关断瞬态(dI/dt) | 正向和负向电压尖峰 | 误导通、直通、栅氧损伤、开关损耗增加 | Kelvin源连接、有源驱动、PCB布局优化 |

3. 串扰对系统性能的深度影响与评估

3.1 开关损耗与系统效率

串扰对系统效率的负面影响是多方面的,其中最直接的是引发额外开关损耗。当被动开关因串扰尖峰而误导通时,会形成上下桥臂的短路直通(Shoot-through)。即使是极短的直通时间,也会在器件上产生巨大的瞬时电流,导致额外的开关导通损耗( Eon)。这种损耗是隐性的,难以用常规方法量化,但它显著降低了系统的整体效率。

另一个重要的损耗来源是体二极管的反向恢复过程。在半桥电路的死区时间(Dead-time)内,电流通常会流经体二极管或外置的反并联二极管 。当另一桥臂的主动开关导通时,这个二极管必须从导通状态迅速恢复到关断状态,这会引发反向恢复电流( Irr)和反向恢复电荷(Qrr)。尽管SiC MOSFET的体二极管Q_{rr}比Si器件低得多(可低92%),但在高速、高电流密度以及高温条件下,其反向恢复行为仍然显著 。反向恢复电流不仅会导致额外的开关损耗,还可能与主回路的寄生电感相互作用,引发电压振铃和EMI问题 。

串扰问题与死区时间的设计紧密相关。死区时间设置过短,可能导致主动开关在体二极管反向恢复完成前就导通,加剧直通和E_{on}损耗 。死区时间设置过长,则会增加体二极管在高正向压降( Vf)下的导通时间,从而增加传导损耗 。因此,设计者必须在“高速”和“可靠性”之间进行权衡,而串扰效应正是这一权衡中的关键限制因素。

3.2 电磁兼容性(EMC/EMI)与电压振铃

高dV/dt和dI/dt的快速开关瞬态会激励主功率回路中的寄生电感(Lloop)和寄生电容(Coss)形成高频谐振回路,导致剧烈的电压和电流振铃 。这种振铃是产生电磁干扰(EMI)的主要来源 。

串扰效应则进一步放大了EMI问题。通过米勒耦合,V_{ds}上的高频振铃会被传输到被动开关的栅极,导致栅极电压振荡 。这种栅极振荡又会反向影响MOSFET的导通状态,引发电流振荡,从而形成一个恶性循环,进一步加剧主功率回路的振铃和EMI 。研究表明,在某些特定的高dV/dt和高结温条件下,串扰甚至会导致电磁不稳定性,产生严重的EMI,特别是在平面型(Planar)SiC MOSFET中 。

3.3 器件可靠性与故障模式

串扰对器件可靠性的影响是毁灭性的。误导通和随之而来的直通短路会使器件在极短时间内承受远超额定值的电流和功率,导致过热、熔融,最终永久性失效 。

此外,串扰引起的门极电压尖峰可能对器件造成长期的累积性损伤。如果正向尖峰超过栅极-源极最大额定电压(VGS,max),或负向尖峰超过最小额定电压(VGS,min),都可能导致栅氧化层(gate oxide)应力过大 。长期或反复出现的这种过应力会加速栅氧层的退化,降低器件的长期可靠性 。尽管有研究表明,短时间的串扰尖峰(数十纳秒)并不会导致立即失效,但其对器件寿命的影响仍不容忽视 。

表2. 串扰对系统性能的深度影响评估

| 影响类别 | 具体表现 | 物理/电路机制 | 量化指标(Eon, Qrr, Irr) | 参考文献 |

|---|---|---|---|---|

| 开关损耗 | 误导通引起的直通电流 | 米勒耦合(Cgd)导致栅极电压尖峰超过Vth | E_{on}增加 | |

| 体二极管反向恢复损耗 | 高dI/dt加速体二极管反向恢复过程 | Qrr、 Irr | ||

| 电磁兼容性(EMC) | 高频电压/电流振铃 | 寄生电感与电容谐振,门极回路二次谐振 | 振铃峰值电压、EMI频谱 | |

| 器件可靠性 | 短路直通导致器件失效 | 误导通引发上下桥臂短路 | 器件温升、热失控 | |

| 栅氧损伤与退化 | 栅极电压尖峰超过VGS,max/VGS,min | 泄漏电流、栅氧击穿 |

4. 综合解决策略:从器件到系统层面的多维度方案

有效抑制SiC MOSFET串扰问题需要采取多层次的综合策略,从器件选型、门极驱动到PCB布局进行协同优化。

4.1 门极驱动电路设计优化

门极驱动电路是控制开关行为的“大脑”,其设计对串扰抑制至关重要。

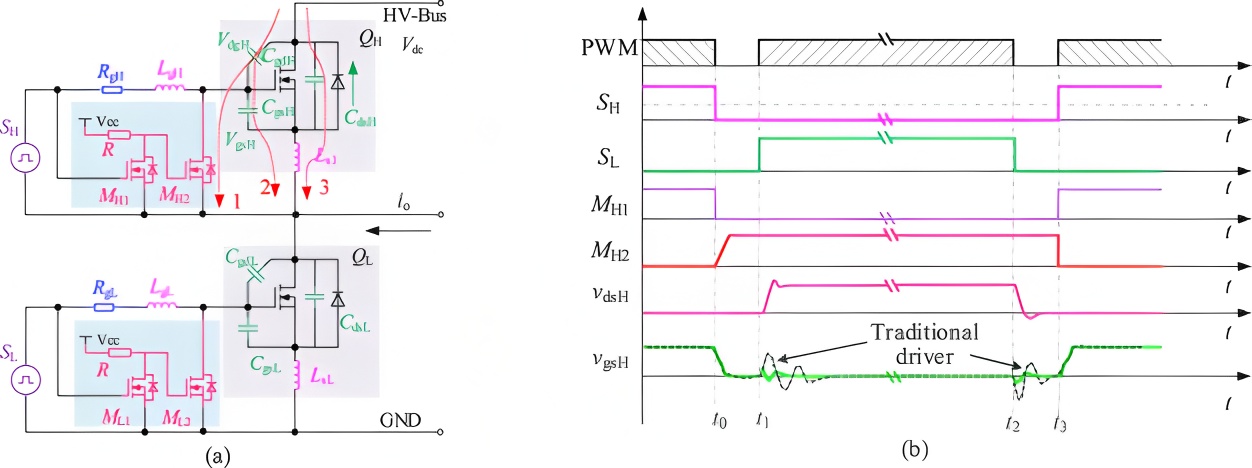

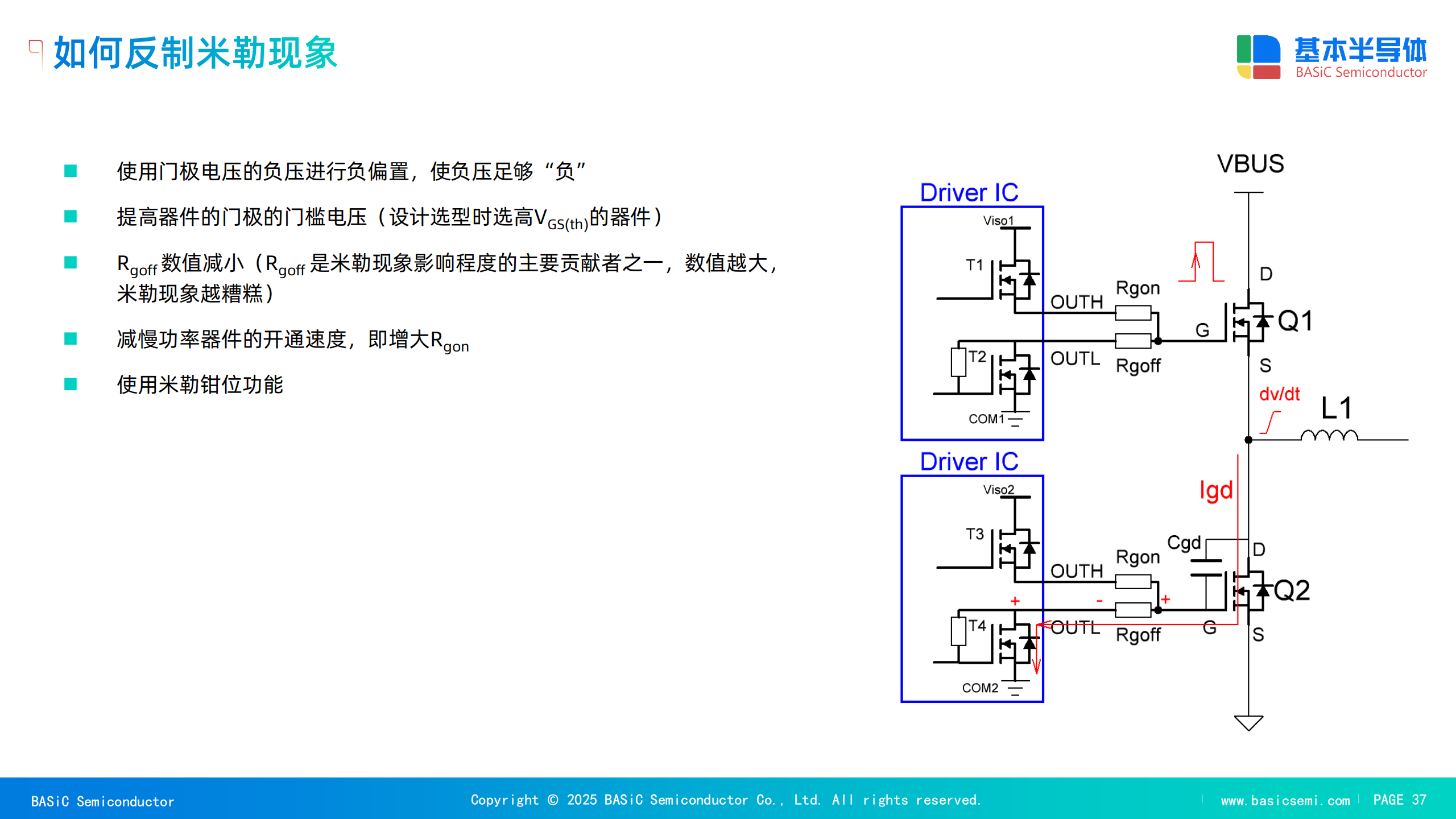

4.1.1 负偏压关断 SiC MOSFET较低的门槛电压(Vth)使得其在关断电压为0 V时对串扰尖峰高度敏感 。一种简单有效的防御策略是在关断期间对栅极施加负偏压(通常为-2 V至-5 V)。这为米勒耦合产生的正向电压尖峰提供了更大的裕度,确保被动开关的 V_{gs}始终低于V_{th},从而有效防止误导通 。此外,负偏压还能加速栅极电荷的泄放,缩短关断时间,进一步降低损耗 。

4.1.2 米勒钳位电路 米勒钳位电路是一种专门针对米勒效应的抑制方案 。其工作原理是在器件关断期间,通过一个低阻抗通路(通常是一个小MOSFET)将栅极与源极短接 。当米勒耦合电流试图抬高栅极电压时,该电流会被直接旁路到源极,从而有效抑制栅极电压的上升,防止误导通 。米勒钳位电路可以作为独立电路设计,也可以集成在门极驱动芯片内部 。

4.1.3 有源门极驱动(AGD) 有源门极驱动(AGD)是应对串扰问题的更高级、更智能的解决方案 。与依赖被动元件(电阻、电容)的传统驱动方式不同,AGD通过实时感应器件的电压或电流波形,动态调整门极驱动电流和电压 。这种闭环控制能够兼顾高速开关与串扰抑制,根据不同的负载、温度和直流母线电压,自适应地优化开关轨迹 。AGD能有效减少开关损耗,抑制电压和电流振铃,并提高系统的电磁兼容性 。

4.2 PCB布局实践:最小化寄生参数

PCB布局是抑制串扰最根本的手段,其核心目标是最小化门极回路和主功率回路的寄生电感。

4.2.1 门极驱动回路的优化 门极驱动回路的寄生电感(Lg)会与栅极电容(Ciss)谐振,产生门极电压振荡 。为最小化

Lg,应将门极驱动芯片尽可能靠近SiC MOSFET放置 。此外,通过将驱动信号走线与其回流路径紧密叠加或平行布线,可以形成最小的环路面积,从而有效减少 Lg 。

4.2.2 主功率回路的优化 主功率回路的寄生电感(Lpower)是高频振铃和电压尖峰的主要来源 。优化布局的关键是减小“高

dI/dt”环路的面积 。这包括将高频去耦电容紧密放置在MOSFET附近,并采用多层板设计,将正负电流路径紧密叠加,形成“平行板”结构 。这种设计利用了磁场抵消原理,能显著降低 Lpower,从而减轻串扰尖峰和EMI问题 。

4.2.3 开尔文源(Kelvin Source)连接的优势 开尔文源连接是物理性解决共源电感串扰问题的理想方案 。在四引脚封装中,Kelvin源引脚为栅极驱动回路提供了一个独立的、与大电流功率回路隔离的源极参考点 。这使得主功率回路中流过源极引线键合的剧烈 dI/dt电流(IL)不会在门极驱动电压中产生感应电压,从而从根本上消除了$L_{cs}$效应的影响 。Kelvin源连接能充分发挥SiC器件的快速开关性能,并显著抑制串扰,从而实现更低的开关损耗 。

4.3 器件选型与封装技术

内置SBD(Schottky Barrier Diode): 一些新一代SiC MOSFET集成了反并联肖特基二极管(SBD),通常与PN结体二极管并联 。由于SBD是单极型器件,不含少数载流子,因此没有反向恢复电荷( Qrr)和相关损耗 。同时,SBD的正向压降通常低于SiC MOSFET体二极管,有助于在死区时间降低导通损耗并抑制反向恢复问题 。

低寄生封装: 封装技术对寄生参数影响巨大 。新型封装,如TOLL和4-lead TO-247,通过缩短引线键合和优化引脚布局,显著降低了封装内部的寄生电感,从而从物理根源上减轻了串扰问题,并充分利用SiC的高速开关优势 。

表3. 串扰抑制策略与设计权衡分析

| 策略类别 | 工作原理 | 优点 | 缺点/权衡 | 应用场景 | 参考文献 |

|---|---|---|---|---|---|

| 负偏压 | 在关断期间提供负Vgs,为串扰尖峰提供裕度 | 简单、有效、成本低 | 可能加剧负向尖峰,需要双极性电源 | 基础应用、传统拓扑 | |

| 米勒钳位 | 关断时将栅极短接至源极,旁路C_{gd}电流 | 高效抑制米勒效应,防止误导通 | 增加电路复杂性,可能略增开关时间 | 高功率、高频应用 | |

| 有源门极驱动 | 实时监测并动态调整门极驱动波形 | 性能最优、可兼顾低损耗与低EMI | 复杂、成本高,需要反馈控制 | 先进的高性能、高可靠性系统 | |

| PCB布局优化 | 最小化门极与功率回路面积,抵消磁场 | 从物理根源减轻寄生效应 | 需要精细设计、多次迭代、对经验要求高 | 所有SiC MOSFET应用 | |

| Kelvin源连接 | 提供独立源极参考,消除L_{cs}影响 | 物理性解决L_{cs}问题,最大化开关速度 | 需要四引脚封装,成本相对较高 | 高速、大功率应用,如EV逆变器 | |

| 内置SBD | 提供低Vf、无Q_{rr}的电流旁路路径 | 减少传导与恢复损耗,提升可靠性 | 可能略微增加开关损耗(Coss) | 高频硬开关、同步整流应用 |

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

需求SiC碳化硅MOSFET单管及功率模块,配套驱动板及驱动IC,请搜索倾佳电子杨茜

5. 结论与展望

倾佳电子深入分析了SiC MOSFET在半桥应用中串扰效应的内在机制、对系统性能的深远影响以及多维度的综合解决策略。研究表明,串扰并非孤立的现象,而是由SiC器件高dV/dt和dI/dt特性与电路中不可避免的寄生参数($C_{gd}$和$L_{cs}$)相互作用的结果。这种耦合会导致误导通、短路直通和栅氧损伤,不仅增加开关损耗、降低效率,还严重恶化电磁兼容性并威胁器件的长期可靠性。

有效应对串扰挑战,需要从以下几个层面协同优化:

门极驱动设计: 负偏压关断为栅极提供了安全裕度;米勒钳位电路从源头旁路了耦合电流;而有源门极驱动则代表了未来的方向,通过动态、自适应控制,实现了高速与可靠性的完美平衡。

PCB布局: 严格遵循最小化环路面积的原则,特别是利用多层板的平行板结构和紧凑的元件布局,从物理层面减少了寄生电感和电容,是所有解决方案的基础。

器件与封装: 新一代器件和封装技术,如集成SBD和开尔文源连接,从根本上改变了器件的电学行为,消除了串扰的主要耦合路径,为系统设计提供了更优异的起点。

展望未来,串扰问题的研究和解决将继续向更深层次发展。有源门极驱动将进一步智能化,结合实时传感器和高级控制算法,实现对开关轨迹的实时、精确控制。封装技术将继续演进,通过更先进的内部结构和异质集成技术,从根本上消除寄生参数,实现“零串扰”的理想目标。随着SiC和GaN等宽禁带半导体技术的不断成熟和成本下降,它们在更广泛的应用中将面临更高的集成度和更复杂的电磁环境,串扰问题的研究也将随之进入新的阶段。

审核编辑 黄宇

- 相关推荐

- 热点推荐

- 串扰

- 碳化硅

- SiC MOSFET

-

碳化硅 (SiC) MOSFET dv/dt 极限物理本质深度研究报告2026-02-15 262

-

深度解析SiC碳化硅功率MOSFET米勒效应:物理机制、动态影响与桥式电路中的串扰抑制2026-01-26 467

-

碳化硅(SiC)MOSFET模块硬并联中环流产生的根本机理及综合抑制策略2026-01-25 406

-

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势2026-01-20 3208

-

倾佳电子光伏与储能产业功率半导体分立器件从IGBT向碳化硅MOSFET转型的深度研究报告2025-12-01 2601

-

倾佳电子SVG技术发展趋势与SiC模块应用价值深度研究报告2025-11-30 1635

-

倾佳电子户储与工商业混合逆变器功率器件从IGBT向SiC MOSFET全面转型的驱动因素深度研究报告2025-11-28 2245

-

倾佳电子全碳化硅 (SiC) MOSFET 设计户储逆变器如何助力安全性提升的深度研究报告2025-11-23 2907

-

倾佳电子SiC碳化硅MOSFET串扰抑制技术:机理深度解析与基本半导体系级解决方案2025-10-02 1354

-

倾佳电力电子系统中共模电压和共模电流的深度研究及SiC功率器件的抑制贡献2025-09-29 7589

-

倾佳电子碳化硅MOSFET短路特性与退饱和保护(DESAT)深度研究报告2025-09-01 1519

全部0条评论

快来发表一下你的评论吧 !