DS560MB410 4通道线性转接驱动器技术解析与应用指南

描述

Texas Instruments DS560MB410 4通道线性转接驱动器是一款低功耗、高性能线性均衡器,支持多速率、多协议接口。使用四级脉冲振幅调制 (PAM4) 时最高可达28GBD,使用非归零码 (NRZ) 调制时最高可达32GBD。它可扩展用于源铜缆 (ACC)、背板和中板应用中高速串行链路的覆盖范围并提升稳定性。DS560MB410可将两个ASIC之间的覆盖范围增加至比正常的ASIC到ASIC范围高18dB以上。

数据手册:*附件:Texas Instruments DS560MB410 4通道线性转接驱动器数据手册.pdf

每个通道独立运行,用户可选择的CTLE升压曲线经过优化,可均衡PCB或铜缆损耗曲线。DS560MB410均衡的线性特性保留了流经转接驱动器的输入信号特性。这种透明性使链路伙伴ASIC能够在链路训练期间自由协商Tx均衡器系数, 并支持任务模式下的单个通道正向纠错 (FEC) 直通,同时更大限度地降低对延迟的影响。

DS560MB410的小型封装尺寸和经优化的高速信号退出使其成为小尺寸封装的理想选择。简化的均衡控制、低功耗和超低附加抖动使其适用于中板和背板和上的芯片至芯片范围扩展和信号分配。6.00Mm × 6.00mm的小尺寸可轻松适应有源铜缆 (ACC) 装配应用,无需散热器。DS560MB410采用单个电源,可尽可能减少对外部组件的需求。这些特性降低了PCB布局布线复杂度以及物料清单 (BOM) 成本。Texas Instruments DS560MB410可通过SMBus或外部EEPROM进行配置。单个EEPROM最多可由16个器件共享。

特性

- 四通道多协议线性均衡器,支持高达28GBd (PAM4) 和32GBd (NRZ) 的接口

- 适用于高达CEI-56G、以太网 (400 GbE)、光纤通道 (64GFC)、InfiniBand™ (HDR) 和CPRI/eCPRI PCB和铜缆应用

- 可选择的CTLE升压曲线,用于补偿PCB或电缆损耗

- 具有引脚或寄存器控制的集成2x2交叉点,适用于多路复用器、扇出和信号交叉

- 低功耗:160mW/通道(典型值)

- 无需散热片

- 无缝支持CR/KR链路训练、自动协商和前向纠错(FEC)直通功能的CTLE线性均衡

- 在13.28GHz下,将远距离链路扩展至比正常的ASIC至ASIC性能高18dB+

- 用于PAM-4眼图对称性增强的眼图扩展器

- 低输入至输出延迟:80ps(典型值)

- 低附加随机抖动

- 小型6.00mm × 6.00mm BGA封装,可轻松实现直通布线

- 无需基准时钟

- 单个2.5V ±5%电源

- –40°C至+85°C环境温度范围

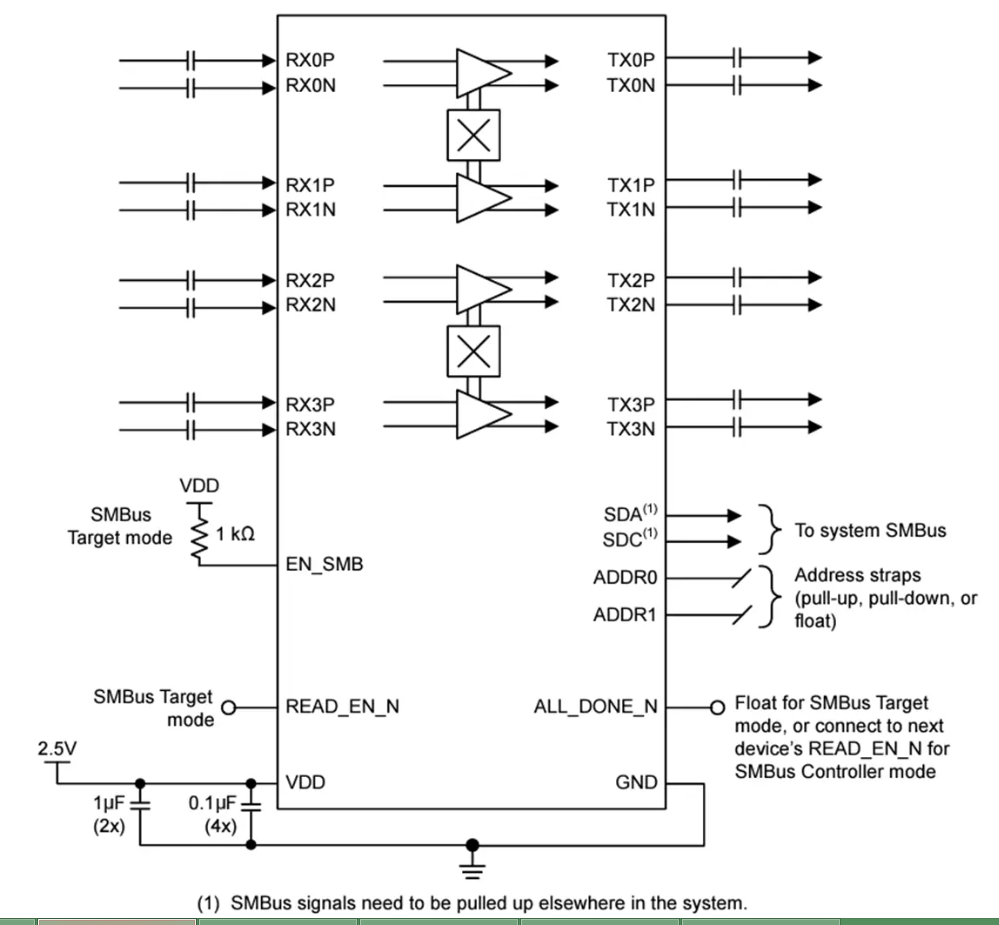

简化示意图

DS560MB410 4通道线性转接驱动器技术解析与应用指南

一、核心特性与协议支持

关键性能参数:

- 四通道多协议线性均衡器

- 支持28-GBd PAM4调制

- 兼容32-GBd NRZ调制

- 超低功耗设计:160mW/通道(典型值)

- 卓越的信号增强能力:

- 在13.28GHz频率下可补偿18dB+信道损耗

- 集成眼图扩展器改善PAM4信号对称性

- 极低延迟特性:80ps端到端延迟(典型值)

协议兼容性:

- 以太网(400GbE)

- 光纤通道(64GFC)

- InfiniBand HDR

- CPRI/eCPRI标准

二、架构设计与功能模块

1. 信号处理链

- 连续时间线性均衡器(CTLE) :

- 提供可选的PCB/电缆损耗补偿曲线

- 支持动态调整均衡参数

- 2×2交叉点矩阵:

- 支持NRZ模式下的信号交叉路由(最高32GBd)

- 提供引脚和寄存器双重控制接口

2. 控制接口

- SMBus/I2C接口:

- 支持外接EEPROM配置

- 最多16个设备共享单个EEPROM

- 硬件控制模式:

- 通过ADDR0/ADDR1引脚设置设备地址

- READ_EN_N实现控制器级联

三、典型应用场景

1. 背板信号增强

设计要点:

- 补偿FR4板材在28GHz的插入损耗

- 典型布线长度扩展能力:≥20英寸(56G PAM4)

- 推荐CTLE设置:Profile 3(最大均衡量)

2. 有源铜缆设计

实施方案:

- QSFP-DD/OSFP模块内集成

- 无需散热片的小型化设计

- 配合Retimer实现端到端链路优化

3. 冗余系统配置

故障切换架构:

// 典型2:1多路复用配置

assign TX0 = (FAILOVER) ? RX2 : RX0;

assign TX1 = (FAILOVER) ? RX3 : RX1;

四、硬件设计指南

1. 电源设计

- 单电源供电:2.5V±5%

- 去耦要求:

- 1×1μF陶瓷电容(VDD主滤波)

- 4×0.1μF陶瓷电容(每通道旁路)

2. PCB布局规范

- 封装特性:6mm×6mm BGA(101球)

- 高速信号布线:

- 差分对内长度偏差<5mil

- 阻抗控制100Ω±10%

- 热设计考虑:

- θJA=178.6°C/W(自然对流)

- 建议使用4层以上PCB堆叠

五、配置与调优

1. CTLE优化流程

- 测量信道S21参数

- 选择匹配的预设均衡曲线

- 通过眼图扫描验证优化效果

2. 交叉点配置

寄存器映射示例:

| 地址 | 位域 | 功能描述 |

|---|---|---|

| 0x12 | [1:0] | 通道0路由选择 |

| 0x12 | [3:2] | 通道1路由选择 |

六、性能测试数据

1. 抖动特性

| 参数 | 条件 | 典型值 |

|---|---|---|

| 随机抖动 | 56G PAM4 | 150fs |

| 确定性抖动 | 经过20dB损耗 | 1.2ps |

2. 功耗分析

| 工作模式 | 单通道功耗 | 四通道总功耗 |

|---|---|---|

| 全功能模式 | 165mW | 660mW |

| 节能模式 | 85mW | 340mW |

该器件特别适用于需要长距离信号传输的56G/112G SerDes系统,其线性架构可完美支持KR模式链路训练和FEC透传,是下一代数据中心互连设备的理想选择。

-

探索DS160PR410:四通道PCI - Express第4代线性转接驱动器的卓越性能与应用2025-12-17 459

-

DS320PR410:支持PCIe™ 5.0、CXL 2.0的四通道线性转接驱动器2025-12-16 627

-

DS320PR810八通道线性转接驱动器技术解析与应用指南2025-09-09 1029

-

DS560MB410EVM重定时器评估模块技术解析2025-09-01 1034

-

DS320PR1601RSC-EVM线性转接驱动器评估模块技术解析2025-08-28 872

-

DS320PR1601 PCIe 5.0 32Gbps线性转接驱动器技术解析与应用指南2025-08-21 1149

-

DS320PR410四通道PCIe 5.0线性转接驱动器技术解析与应用指南2025-08-08 1260

-

DS560MB410EVM用户指南2024-11-15 399

-

DS160PR410四通道PCI-Express第4代线性转接驱动器数据表2024-07-02 613

-

DS560MB410低功耗56Gbps PAM4 4通道线性转接驱动数据表2024-06-28 487

-

DS160PR412 PCIe 4.0 16Gbps 4通道线性转接驱动器数据表2024-06-24 606

-

DS320PR410支持PCIe5.0、CXL 2.0的四通道线性转接驱动器数据表2024-06-21 474

全部0条评论

快来发表一下你的评论吧 !