fpga开发板 璞致ZYNQ UltraScale+ MPSOCPZ-ZU19EG 核心板与开发板用户手册

电子说

描述

第一章:UltraScale+MPSoC介绍

Xilinx Zynq UltraScale MPSoC 架构基于 TSMC 16FinFET+ 处理技术,实现下 一代 Zynq® UltraScale+ MPSoC。在 Zynq-7000 SoC 系列成功的基础上,全新的 UltraScale MPSoC 架构进一步扩大了 Xilinx SoC,支持真正的异构多处理功能, 可为更智能系统的适当任务提供适当引擎,包括:

-Smarter Control

互联控制/机器间:灵活/可自适应 制造、工厂吞吐量、质量和安全

- Smarter Vision

高级 2D/3D:不断发展的视频处理算法、目标检测与分析

- Smarter Network

无线通信: 支持多个频带和智能天线

有线通信:多种有线通信标准和上下文感知网络服务

数据中心: 软件定义网络 (SDN) 、数据预处理,以及分析功能

ZYNQ UltraScale MPSoC 架构提供多个高级处理器,能从 32 位扩大到 64 位, 提供虚拟支持。Xilinx 一直在与 ARM® 合作,提供支持 Cortex®-A53 的最高效 64 位 ARMv8 应用处理器、具有 ARM® Cortex®-R5 的实时低功耗协处理器以及符合 OpenGL ES 1.1/2.0 标准的 ARM® Mali™-400MP 多内核 GPU,充分发挥 ARM 在嵌 入式处理器及其生态系统中的领先地位优势。此外,ZYNQ UltraScale MPSoC 还包 含 H.265/H.264 视频编解码器单元,可提供原生 UltraHD 压缩及专用引擎,满足动 态电源管理与安全配置需求。

Xilinx 具有支持 SoC 优势的各种工具,提供 Vivado® Design Suite、 Xilinx SDK 以及 PetaLinux,可进一步加速使用 SDx™ 系列设计抽象环境的开发,从而可 高效利用 ZYNQ UltraScale+ MPSoC 的强大功能。该架构的基本元素包括:

- 64 位四核 ARM Cortex-A53 处理器

- 双核 ARM Cortex-R5

- 实时处理器 ARM Mali™-400MP

- 图形处理器 H.265/264

- 视频编码解码器单元

- 高级动态功耗管理单元

- 配置安全单元

- DDR4/LPDDR4 内存接口支持

- 16FinFET+ 单位功耗性能

- SDSoC 开发环境 (设计抽象)

- 下一代 AXI 互联

- 兼容 Zynq-7000SoC、软件和生态系统

[]() []()第二章:开发板概述

[]()2.1.开发板概述

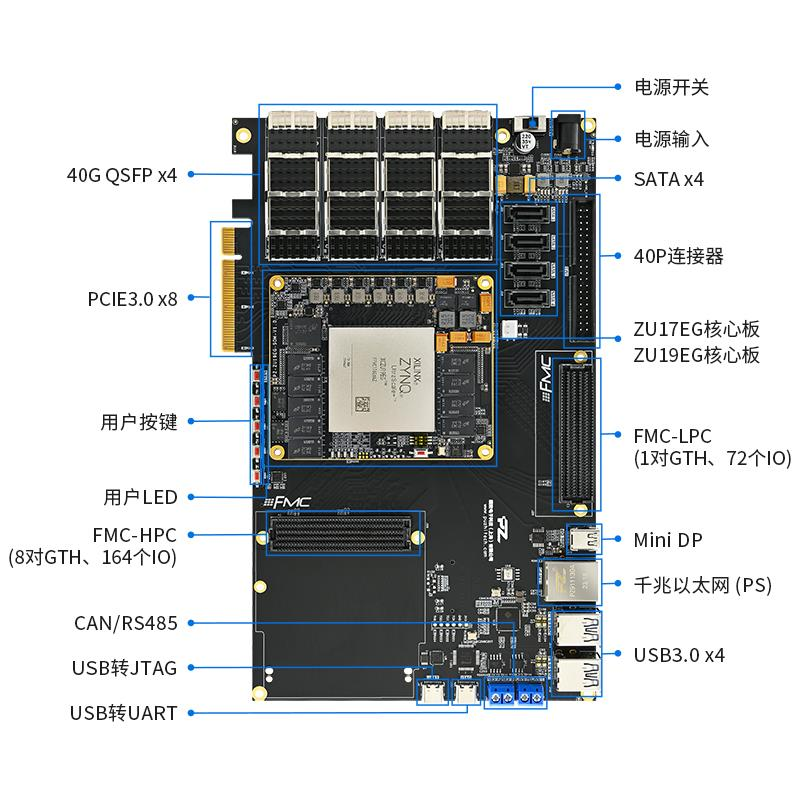

璞致电子科技 ZYNQ UltraScale+ MPSOC 系列开发板做了 ZU17EG 和

ZU19EG 两个兼容版本,分别使用了 XILINX 公司的 XCZU17EG-2FFVC1760I 和 XCZU19EG-2FFVC1760I 作为主控制器,默认生产型号为 ZU19EG,如用户需要 ZU17EG,可以联系璞致生产。

璞致电子科技 ZYNQ UltraScale+系列开发板以核心板加底板方式提供。

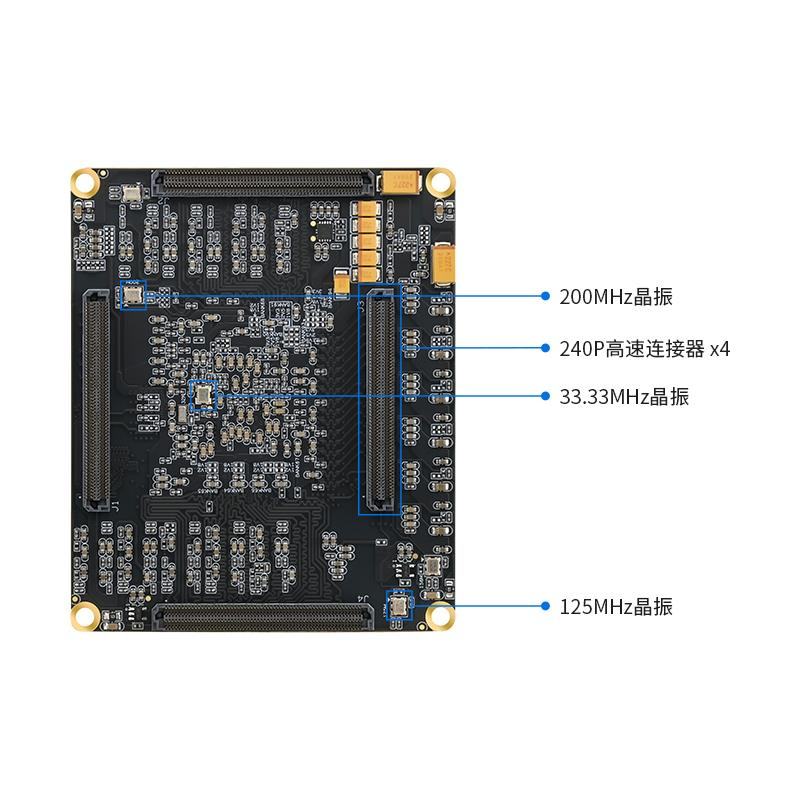

核心板通过四个0.635mm 间距 240P 高速连接器扣接在底板上,使用上更加灵 活。既可以做学习使用,也可以使用核心板用于项目开发。

另外,开发板集成了丰富的外设资源,提供了详尽的开发例程,加速了用 户学习或者项目推进。除此之外,开发板还集成了 JTAG 调试器,做到了一根 USB 线和一根 12V 电源线就可以让开发板工作起来,使用更加便捷。

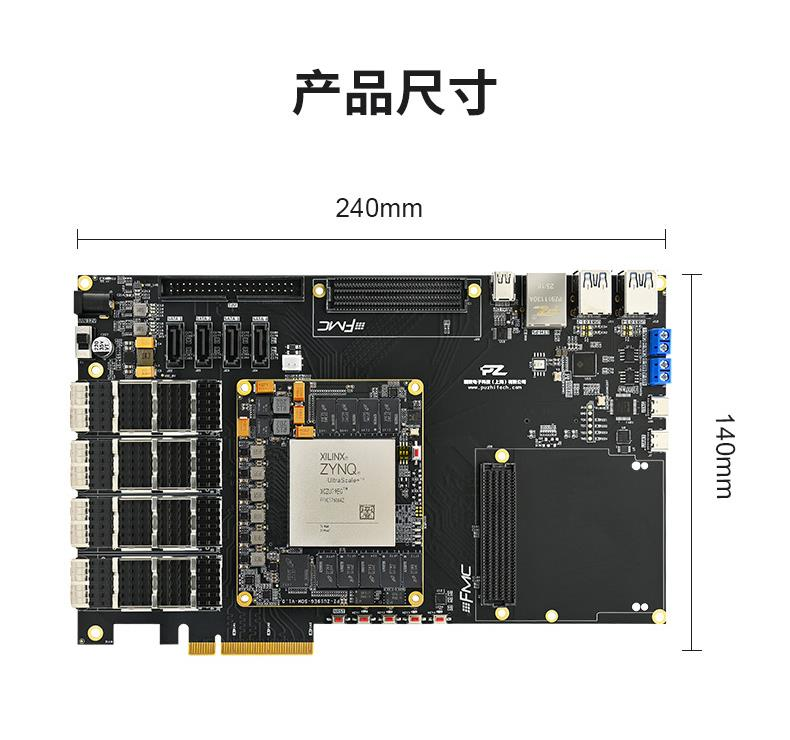

开发板尺寸为 240x140mm,单板的四个角各放置一个固定孔,用于安装支撑 柱或固定单板,孔径为 3.5mm。如下图分别是开发板和核心板的功能模块位置标 注以及尺寸图,用户可以根据标注查看外设所在位置。

编辑

编辑

编辑

编辑

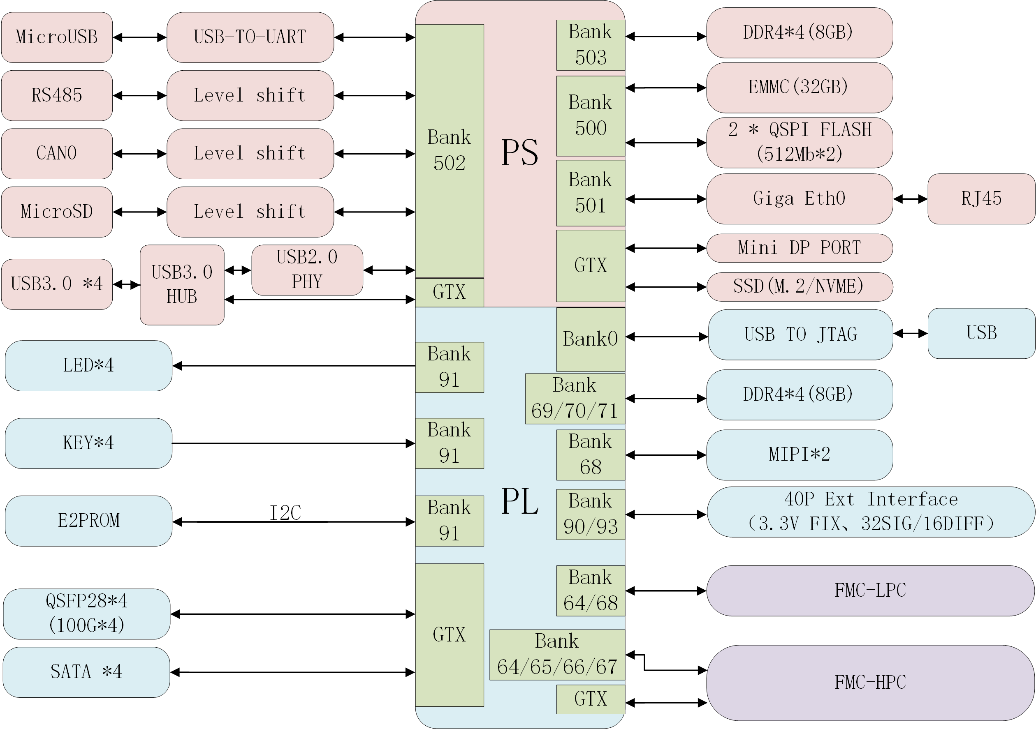

[]()2.2.开发板资源与框图

如下表与框图已列出开发板板载资源,通过下表可以看到开发板所包含的 所有功能。

编辑

编辑

[]()2.3.开发板尺寸

如下图标出开发板尺寸为 240x140mm,开发板的四个角各放置一个固定孔, 用于安装支撑柱或固定单板,孔径为 3.5mm。开发板配置了风扇、散热片以及亚 克力防护板,为方便展示,并没有安装到开发板上,下图列出了散热片和风扇 以及对应尺寸。

编辑

[]() []()第三章:PZ-ZU19EG********核心板

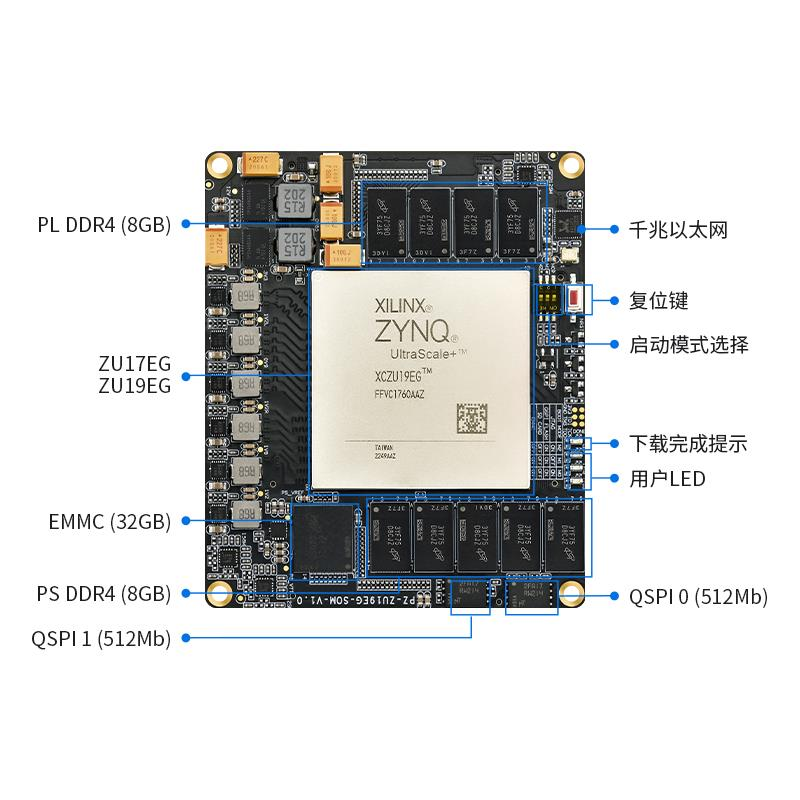

[]()3.1.核心板简介

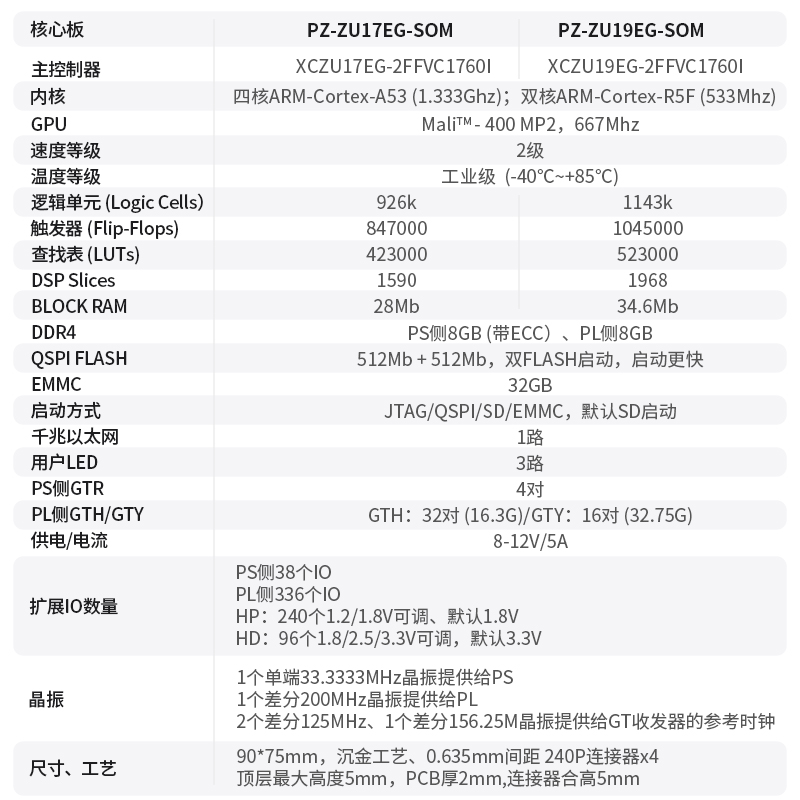

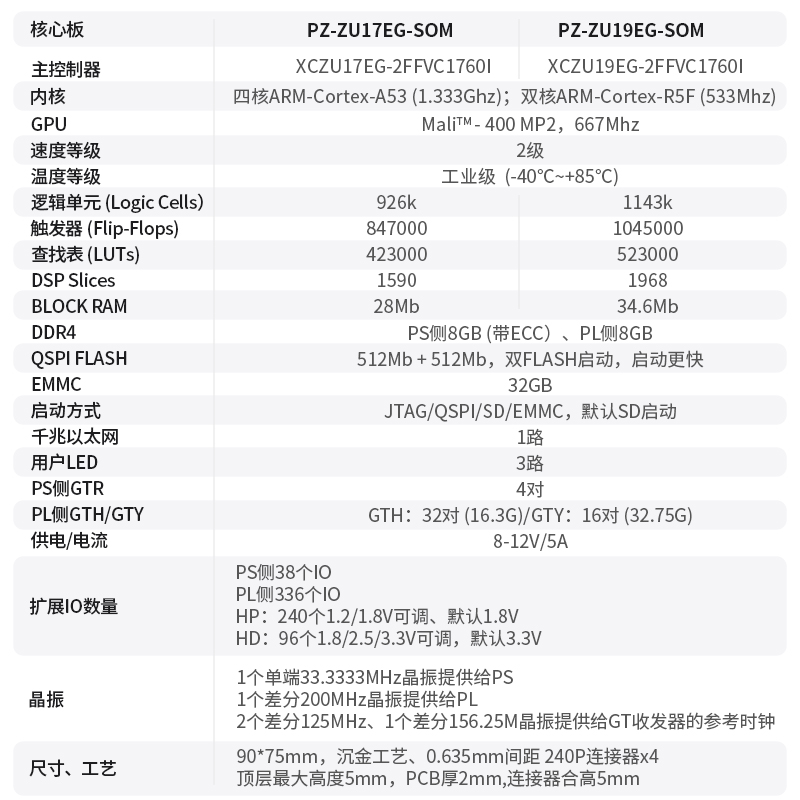

开发板采用了核心板扣接底板的方式,对于开发板的型号取决于使用的核 心板型号。核心板提供 ZU17EG 和ZU19EG 两款,两款接口完全兼容,通过更换 核心板方式就可以实现开发板的型号更换,璞致默认生产 ZU19EG,如用户需 要 ZU17EG 可以联系璞致生产。如下表列出了两款核心板的参数以及之间的差 异。

[]()3.2.核心板规格

编辑

[]()3.3.核心板供电

核心板供电电压范围是 8-12V,推荐供电电压为 8V,在核心板的两个角都 留有电源输入管脚,电源管脚在模块内部已做了连通,此设计是为了方便底板 的电源接入,设计时只需要连接一个角上的电源管脚,核心板即可工作。电源 连接需用铜皮连接且打足够的过孔以保证电源通流能力。核心板上的所有 GND 信号都需要连接到底板上,每个 GND 通过两个过孔与底板连接。核心板供电极 限电流在 5A,所以外部供电需要考虑极限电流情况以保证核心板工作稳定。

给模组供电的电源输出电压需要稳定,在模组电源输入加一级 DCDC 电源 转换,从高电压转到 8-12V(推荐 8V),DCDC 电流输出能力可以选 8A 左右,如 电源芯片 TPS54A24RTWR 可以参考。在模组电源输入处需放置 2 颗 220uF/25V 电容保证电源质量。

编辑

[]()3.4.核心板时钟

核心板为 PS 侧提供了 33.333333Mhz 的时钟输入,输入的管脚位置为

PS_REF_CLK;为 PL 侧提供了 200Mhz 的差分时钟输入,PL 侧的时钟输入管脚 是 IO_13P_GC_69/IO_13N_GC_69,管脚位置是 E32/D32;为 PL 侧 GTX 提供了三 路差分时钟输入,分别为 125M/125M/156.25M 三个晶振输入到时钟芯片。另外 时钟做了板卡上晶振和连接器外部时钟输入选择,当时钟选择信号不接地时钟 来源为差分晶振,当时钟选择信号接地时时钟来源为连接器外部输入,更详细 说明可参考璞致提供的核心板原理图。

[]()3.5.核心板全局复位

核心板提供了 nGST 复位按键,为系统复位按键,低电平有效。此引脚也引出到 了连接器,信号名称为 SYS_nRST_I,方便外部加入复位按键或者设计看门狗复位电 路用。同时为了系统稳定, 我们在核心板上加了复位芯片,此信号可以用于单板其他 外设的复位用,信号电平是 3.3V。复位脚为 PS/PL 共用复位,连接到 PS 侧的 PS_POR_B(W27)引脚上和 PL 侧 BANK68 的 IO_T1U_68(J17)管脚,电平约束可以参考璞 致提供的例程。

如果底板上需要设计复位电路有以下几种情况需考虑。

1)复位电路底板内部使用,只需要对地添加复位按键和一个 10uF 电容并口即可。

2) 复位电路需要预留在结构上供外部使用,需要添加对地按键,同时对地并联 10uF 电容和 TVS 防静电器件。

编辑

nRST Key nRST IC

PS_POR_B(W27)

PL

IO_T1U_68(J17)

[]()3.6.核心板启动方式

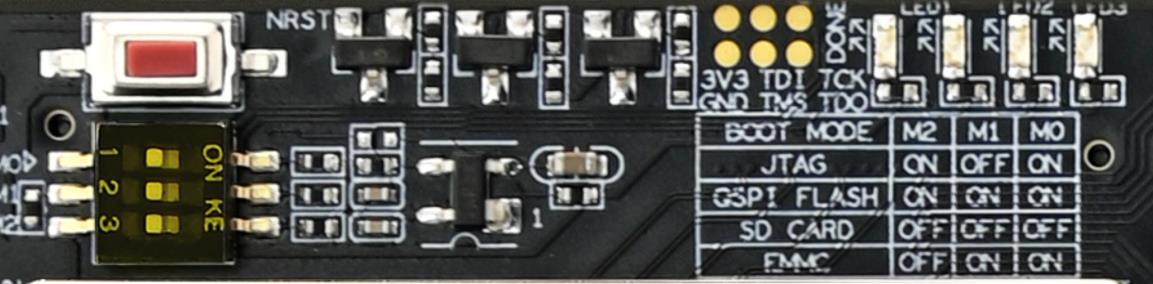

核心板支持四种启动模式,分别是 JTAG、QSPI Flash、EMMC 、SD 卡。板载了 前三种启动方式,SD 卡方式用户可以通过在底板上连接实现。四种启动方式可以通 过板载的拨码开关来选择。如下图已列出各个模式拨码开关所在的位置。因主芯片 发热量较大,所以在核心板上需要加散热片,会遮挡 BOOT MODE 选择表格。

编辑

[]() 3.7.网口连接

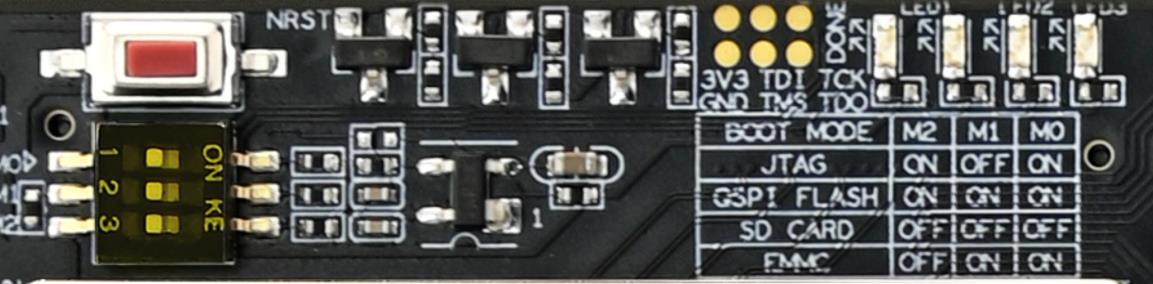

核心板上放置了一颗工业级千兆以太网芯片 RTL8211FI-CG,以太网芯片与 ZYNQ 芯片之间通过 RGMII 接口互联,连接对应管脚见下表,以太网对外连接只需要一个 带变压器的 RJ45 即可使用,芯片地址 PHY_AD[2:0]=001,连接原理图可参考下图(产 品电路需加 ESD 保护电路)。另外, 在实际产品应用中,C80 需要使用高耐压电容, 如 0.1uF/2KV。

| RMGII********信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| GTX_CLK | MIO26_501 | L27 |

| TXD0 | MIO27_501 | L29 |

| TXD1 | MIO28_501 | L28 |

| TXD2 | MIO29_501 | M27 |

| TXD3 | MIO30_501 | L30 |

| TX_EN | MIO31_501 | M28 |

| RX_CLK | MIO32_501 | M30 |

| RXD0 | MIO33_501 | N28 |

| RXD1 | MIO34_501 | P27 |

| RXD2 | MIO35_501 | N29 |

| RXD3 | MIO36_501 | T27 |

| RX_DV | MIO37_501 | N30 |

| MDC | MIO76_502 | AH31 |

| MDIO | MIO77_502 | AG31 |

编辑

[]() 3.8.EMMC********管脚定义

板载 EMMC 容量 32GB,工作温度为-40℃--+85℃,管脚定义如下表。

| EMMC********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| EMMC_D0 | MIO13 | AD34 |

| EMMC_D1 | MIO14 | AJ32 |

| EMMC_D2 | MIO15 | AD35 |

| EMMC_D3 | MIO16 | AJ31 |

| EMMC_D4 | MIO17 | AJ30 |

| EMMC_D5 | MIO18 | AE34 |

| EMMC_D6 | MIO19 | AE35 |

| EMMC_D7 | MIO20 | AH34 |

|---|---|---|

| EMMC_CLK | MIO22 | AH32 |

| EMMC_CMD | MIO21 | AF35 |

| EMMC_nRST | MIO23 | AG35 |

[]()3.9.QSPI********FLASH

核心板设计了两路 QSPI FLASH,单片容量为 512Mb,两片共计 1024Mb,用户可 以定义为 QSPI X8 来加速启动,减少启动用时。QSPI FLASH 可用于存储启动文件和 用户文件。

| QSPI0FLASH********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DATA0 | MIO4 | AL33 |

| DATA1 | MIO1 | AM29 |

| DATA2 | MIO2 | AM31 |

| DATA3 | MIO3 | AM30 |

| QSPI_CS | MIO5 | AL32 |

| QSPI_CLK | MIO0 | AM33 |

| QSPI1FLASH********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DATA0 | MIO8 | AK33 |

| DATA1 | MIO9 | AK34 |

| DATA2 | MIO10 | AK30 |

| DATA3 | MIO11 | AK32 |

| QSPI_CS | MIO7 | AL30 |

| QSPI_CLK | MIO12 | AJ34 |

[]()3.10.板载********LED

为方便调试,核心板上放置了三颗 LED,LED 连接到 PL 侧,LED 的管脚位置如下 表,当管脚输出高电平时 LED 点亮,低电平 LED 灭。

| 序号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1 | IO-T2U-68 | C14 |

| LED2 | IO-T3U-68 | A15 |

| LED3 | IO-T2U-67 | AP11 |

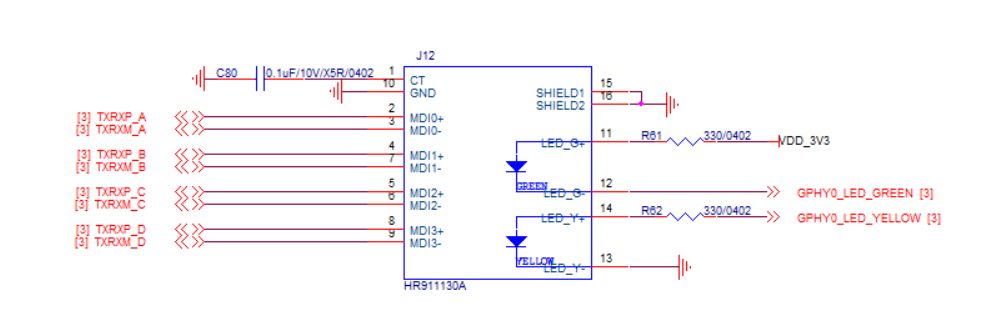

[]() 3.11.BANK********接口电平选择

单板上 BANK64/65/66/67/68 为 HP BANK,接口电平配置为 1.2/1.8V, 可以通过 单板上提供 的指示进 行 0 欧姆 电 阻选焊来调节 电压 ,默认 电平为 1.8V。

编辑

BANK90/91/93/94 为 HD BANK,BANK 电平可以实现 1.8V/2.5V/3.3V 三种电平转换, 更换电阻位置即可,默认电平为 3.3V。

[]()3.12.PS侧DDR

PS 侧配置了五颗工业级 DDR4 芯片,单颗容量 2GB,四颗共计容量为 8GB,另 一颗做 ECC 用, DDR4 管脚分配直接调用系统分配即可。也可以参考我司提供的例程。

[]()3.13.PL侧DDR

PL 侧配置了四颗工业级 DDR4 芯片,单颗容量 2GB,四颗共计容量为 8GB,DDR4 管脚分配参见下表。

| DDR4********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DDR4_DQ0 | IO_L3N_70 | N25 |

| DDR4_DQ1 | IO_L2N_70 | L25 |

| DDR4_DQ2 | IO_L2P_70 | M25 |

| DDR4_DQ3 | IO_L5N_70 | N23 |

| DDR4_DQ4 | IO_L5P_70 | P23 |

| DDR4_DQ5 | IO_L6N_70 | L23 |

| DDR4_DQ6 | IO_L3P_70 | N24 |

| DDR4_DQ7 | IO_L6P_70 | M23 |

| DDR4_DM0 | IO_L1P_70 | P26 |

| DDR4_DQS_P0 | IO_L4P_70 | L24 |

| DDR4_DQS_N0 | IO_L4N_70 | K24 |

| DDR4_DQ8 | IO_L8P_70 | K26 |

| DDR4_DQ9 | IO_L11N_GC_70 | H26 |

| DDR4_DQ10 | IO_L9N_70 | J24 |

| DDR4_DQ11 | IO_L12P_GC_70 | H24 |

| DDR4_DQ12 | IO_L9P_70 | J23 |

|---|---|---|

| DDR4_DQ13 | IO_L11P_GC_70 | H25 |

| DDR4_DQ14 | IO_L8N_70 | J26 |

| DDR4_DQ15 | IO_L12N_GC_70 | G25 |

| DDR4_DM1 | IO_L7P_70 | K27 |

| DDR4_DQS_P1 | IO_L10P_70 | H23 |

| DDR4_DQS_N1 | IO_L10N_70 | G23 |

| DDR4_DQ16 | IO_L15P_70 | F27 |

| DDR4_DQ17 | IO_L14P_GC_70 | F25 |

| DDR4_DQ18 | IO_L17P_70 | D27 |

| DDR4_DQ19 | IO_L14N_GC_70 | E25 |

| DDR4_DQ20 | IO_L15N_70 | F28 |

| DDR4_DQ21 | IO_L18P_70 | F24 |

| DDR4_DQ22 | IO_L17N_70 | D28 |

| DDR4_DQ23 | IO_L18N_70 | E24 |

| DDR4_DM2 | IO_L13P_70 | G26 |

| DDR4_DQS_P2 | IO_L16P_70 | E26 |

| DDR4_DQS_N2 | IO_L16N_70 | E27 |

| DDR4_DQ24 | IO_L21N_70 | B27 |

| DDR4_DQ25 | IO_L24N_70 | A25 |

| DDR4_DQ26 | IO_L20P_70 | A27 |

| DDR4_DQ27 | IO_L23N_70 | C25 |

| DDR4_DQ28 | IO_L21P_70 | C26 |

| DDR4_DQ29 | IO_L24P_70 | A24 |

| DDR4_DQ30 | IO_L20N_70 | A28 |

| DDR4_DQ31 | IO_L23P_70 | C24 |

| DDR4_DM3 | IO_L19P_70 | C28 |

| DDR4_DQS_P3 | IO_L22P_70 | B25 |

| DDR4_DQS_N3 | IO_L22N_70 | B26 |

| DDR4_DQ32 | IO_L6N _71 | M21 |

| DDR4_DQ33 | IO_L5P_71 | P21 |

| DDR4_DQ34 | IO_L3N_71 | L19 |

| DDR4_DQ35 | IO_L2N_71 | L18 |

| DDR4_DQ36 | IO_L5N_71 | N21 |

| DDR4_DQ37 | IO_L2P_71 | M18 |

| DDR4_DQ38 | IO_L6P_71 | M22 |

| DDR4_DQ39 | IO_L3P_71 | M20 |

| DDR4_DM4 | IO_L1P_71 | P18 |

| DDR4_DQS_P4 | IO_L4P_71 | N20 |

| DDR4_DQS_N4 | IO_L4N_71 | N19 |

| DDR4_DQ40 | IO_L11N_GC_71 | H19 |

| DDR4_DQ41 | IO_L8N_71 | K20 |

| DDR4_DQ42 | IO_L11P_GC_71 | H20 |

| DDR4_DQ43 | IO_L9N_71 | J21 |

|---|---|---|

| DDR4_DQ44 | IO_L12N_GC_71 | G20 |

| DDR4_DQ45 | IO_L8P_71 | L20 |

| DDR4_DQ46 | IO_L12P_GC_71 | H21 |

| DDR4_DQ47 | IO_L9P_71 | K21 |

| DDR4_DM5 | IO_L7P_71 | K19 |

| DDR4_DQS_P5 | IO_L10P_71 | K22 |

| DDR4_DQS_N5 | IO_L10N_71 | J22 |

| DDR4_DQ48 | IO_L14N_GC_71 | F22 |

| DDR4_DQ49 | IO_L15P_71 | F19 |

| DDR4_DQ50 | IO_L18P_71 | E22 |

| DDR4_DQ51 | IO_L17N_71 | D21 |

| DDR4_DQ52 | IO_L14P_GC_71 | F23 |

| DDR4_DQ53 | IO_L15N_71 | E19 |

| DDR4_DQ54 | IO_L18N_71 | D22 |

| DDR4_DQ55 | IO_L17P_71 | E21 |

| DDR4_DM6 | IO_L13P_71 | G22 |

| DDR4_DQS_P6 | IO_L16P_71 | F20 |

| DDR4_DQS_N6 | IO_L16N_71 | E20 |

| DDR4_DQ56 | IO_L24N_71 | A23 |

| DDR4_DQ57 | IO_L20N_71 | B20 |

| DDR4_DQ58 | IO_L23P_71 | B22 |

| DDR4_DQ59 | IO_L21P_71 | A20 |

| DDR4_DQ60 | IO_L24P_71 | B23 |

| DDR4_DQ61 | IO_L20P_71 | C20 |

| DDR4_DQ62 | IO_L23N_71 | A22 |

| DDR4_DQ63 | IO_L21N_71 | A19 |

| DDR4_DM7 | IO_L19P_71 | D19 |

| DDR4_DQS_P7 | IO_L22P_71 | C21 |

| DDR4_DQS_N7 | IO_L22N_71 | B21 |

| DDR4_A0 | IO_L17P_69 | B35 |

| DDR4_A1 | IO_L21N_69 | A38 |

| DDR4_A2 | IO_L11P_GC_69 | E31 |

| DDR4_A3 | IO_L20N_69 | B37 |

| DDR4_A4 | IO_L18N_69 | A34 |

| DDR4_A5 | IO_L21P_69 | A37 |

| DDR4_A6 | IO_L18P_69 | A33 |

| DDR4_A7 | IO_L15P_69 | D33 |

| DDR4_A8 | IO_L10N_69 | A32 |

| DDR4_A9 | IO_L15N_69 | C33 |

| DDR4_A10 | IO_L17N_69 | A35 |

| DDR4_A11 | IO_L10P_69 | B31 |

| DDR4_A12 | IO_L16N_69 | C34 |

| DDR4_A13 | IO_L11N_GC_69 | D31 |

|---|---|---|

| DDR4_A14 | IO_L22N_69 | A40 |

| DDR4_A15 | IO_L16P_69 | D34 |

| DDR4_A16 | IO_L12P_GC_69 | C30 |

| DDR4_A17 | IO_L12N_GC_69 | C31 |

| DDR4_BA0 | IO_L23N_69 | B41 |

| DDR4_BA1 | IO_L9N_69 | A30 |

| DDR4_BG0 | IO_L23P_69 | B40 |

| DDR4_nCS | IO_L8N_69 | B30 |

| DDR4_ODT | IO_L20P_69 | B36 |

| DDR4_nRESET | IO_L19N_69 | C37 |

| DDR4_CLK_P | IO_L14N_GC_69 | B32 |

| DDR4_CLK_N | IO_L14P_GC_69 | B33 |

| DDR4_CKE | IO_L8P_69 | C29 |

| DDR4_nACT | IO_L22P_69 | A39 |

| DDR4_nALERT | IO_L7N_69 | D29 |

| DDR4_PARITY | IO_L19P_69 | C36 |

[]()3.14.核心板信号与等长

核心板引出到连接器的信号都做了严格等长,可以参考璞致提供的信号等长表 格,里面详细列出了信号名称和信号走线长度。

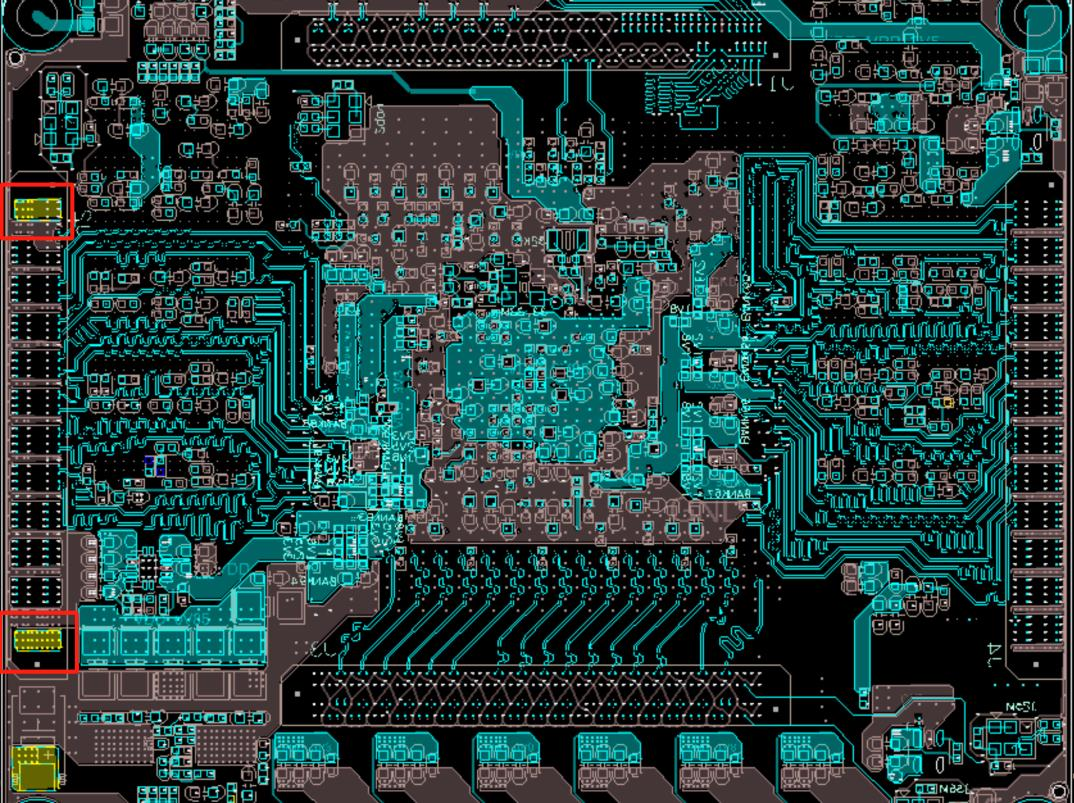

3.15.核心板封装库

为方便用户快速使用核心板,我们提供了对应的封装库,连接器相对位置和核 心板外框丝印都已摆放好,直接调用即可。原理图封装提供 AD/ORCAD 两个版本,PCB 封装提供 AD/Allegro 两个版本,均已存放在对应的文件夹下。另外,文件夹下提供 了核心板的 DXF 文件,方便用户对应结构。

3.16.核心板对应连接器

核心板采用了两个高密连接器与底板连接,底板上使用的连接器对应型号是 ADM6-60-01.5-L-4-2-A-TR,用户可以自行购买,也可以联系璞致客服购买。

[]()[]()第四章PZ-ZU19EG **** 底板****

[]() 4.1.电源供电

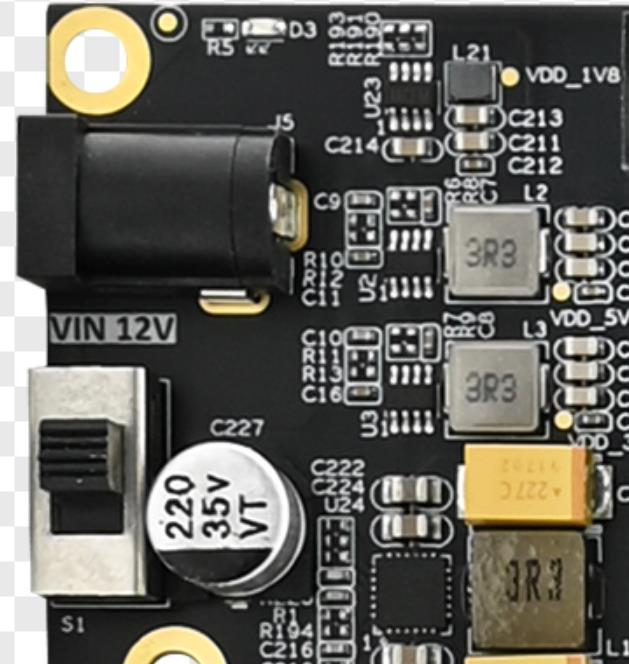

开发板采用 12V/3A 的适配器供电,电源接入后通过 DCDC 转换成 8V、5V、3.3V 等多路电压供板内器件使用。接入 12V 电源可以通过开关 S1开关来控制通断, 电源 部分详细电路可参考开发板对应的原理图。

编辑

[]()4.2.时钟电路

开发板时钟分为两部分,核心板上的时钟和底板上给外设提供的时钟。

核心板为 PS 侧提供了 33.33Mhz 的时钟输入,输入的管脚位置为 PS_REF_CLK; 为 PL 侧提供了 200Mhz/125Mhz/156.25Mhz 时钟,详细电路可参考核心板时钟电路部 分说明或核心板原理图。

底板上使用时钟芯片 5P49V6965A000NLGI 配置成 26/27/100Mhz,提供给 PS 侧 的 USB3.0/Mini DP/SSD 提供时钟源;对于详细的时钟连接可以参考提供的开发板原 理图。

[]()4.3.复位电路

在开发板上和核心板上各预留了一个复位按键,两个按键是连到一起,用户可 以根据方便来选择按键。经过按键后,核心板上放置了一颗复位芯片, 型号为 MAX811TEUS。

复位管脚分别连接到 MPSOC 芯片的 PS 和 PL 端,PS 端连到 BANK0,对应管脚为 PS_POR_B,管脚位置为 W27,PL 侧 BANK68 的 IO_T1U_68(J17)管脚,J17 管脚电平为

3.3V。复位部分详细电路可参考开发板原理图。

编辑

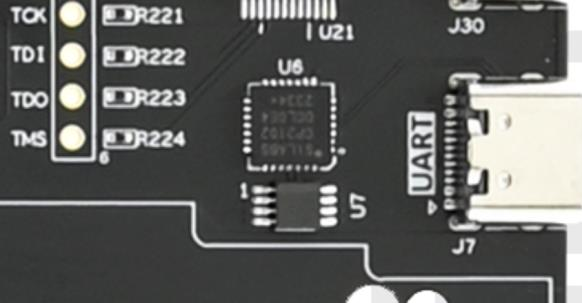

[]() 4.4.USB********转串口

开发板使用 Silicon Labs CP2102GM 芯片实现 USB 转 UART, USB 接口采用 Micro USB,用户只要用一根 Micro USB 线连接到 PC 上即可进行串口通信。

UART 的 TX/RX 信号与 MPSOC 的 BANK501 相连,接口电平为 1.8V,所以串口接口 采用电平转换成 3.3V 与串口芯片相连。

如下是信号对应关系表和原理图,TX/RX 方向为 MPSOC 端定义。

| UART0引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| UART0_TX | MIO_43 | R30 |

| UART0_RX | MIO_42 | T30 |

编辑

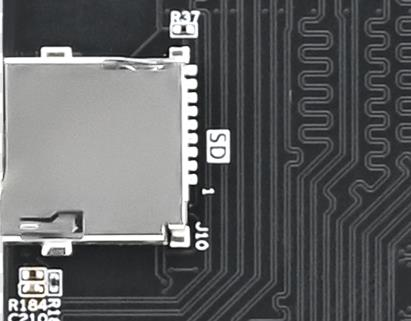

[]()4.5.SD********卡

开发板上放置了一个 SD 卡座(开发板背面),可以做 SD 卡启动,也方便用户调 试或者用户做文件存储,电路接口电平为 1.8V ,SD 卡信号连接到 MPSOC 的 BANK501 上,TF 卡电平为 3.3V,通过专用的电平转换芯片实现 SD 卡信号 1.8V 转 3.3V。

如下是信号对应关系,详细电路可以参考开发板原理图。

| SD********卡引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| SD-CLK | MIO51 | W30 |

| SD-CMD | MIO50 | V29 |

| SD-CD | MIO45 | T29 |

| SD-DATA0 | MIO46 | U28 |

| SD-DATA1 | MIO47 | T28 |

| SD-DATA2 | MIO48 | V30 |

| SD-DATA3 | MIO49 | U29 |

编辑

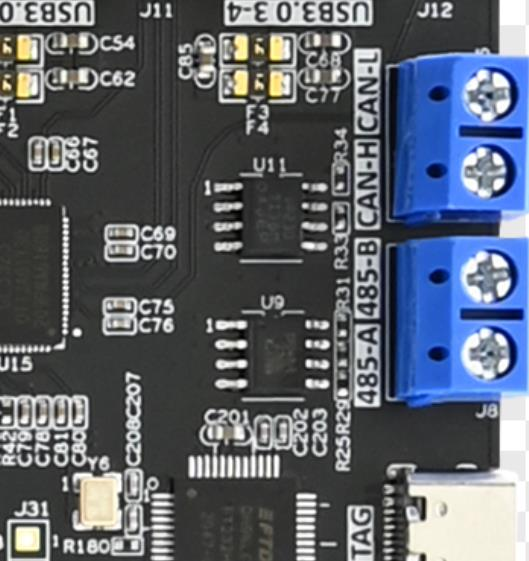

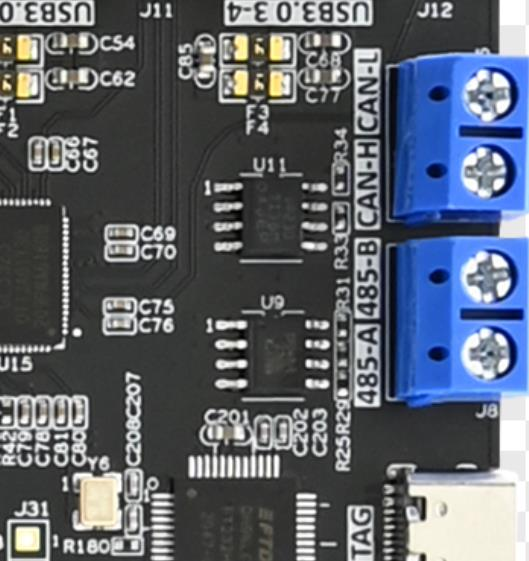

[]() 4.6.RS485接口

开发板使用 SP3485EN 芯片实现 RS485 通信,RS485 的 TX/RX 信号与 MPSOC 的 BANK501 相连,接口电平为 1.8V,所以接口采用电平转换成 3.3V 与 RS485 芯片相 连。

如下是信号对应关系表和原理图,TX/RX 方向为 MPSOC 端定义。

| RS485引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| RS485_TX | MIO40 | AE32 |

| RS485_RX | MIO41 | P30 |

编辑

[]() 4.7.CAN********接口

开发板使用 SN65HVD230D 芯片实现 CAN 通信,CAN 的 TX/RX 信号与 MPSOC 的 BANK501 相连,接口电平为 1.8V,所以信号接口采用电平转换成 3.3V 与CAN 芯片相 连。

如下是信号对应关系表,TX/RX 方向为 MPSOC 端定义,详细电路参考开发板原理 图。

| CAN********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| CAN_TX | MIO39 | P29 |

| CAN_RX | MIO38 | R27 |

编辑

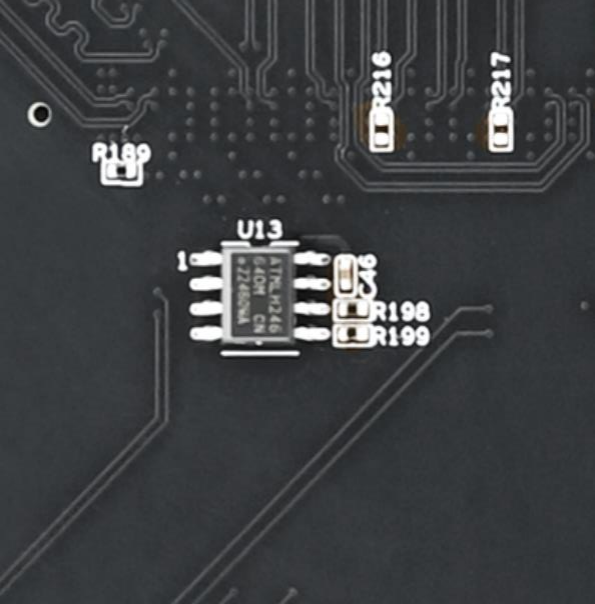

[]()4.8.E2********PROM

开发板上放置了一颗 64Kbit 的 EEPROM 芯片,型号为 AT24C64D-SSHM-T,与 FPGA 的 BANK91 通过 IIC 总线相连。EEPROM 读地址是 0xA1,写地址是 0xA0。

如下是 EEPROM 的管脚分配,详细电路可以参考开发板原理图。

| EEPROM********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| IIC-CLK | IO-1P-91 | J11 |

| IIC-DATA | IO-1N-91 | H10 |

编辑

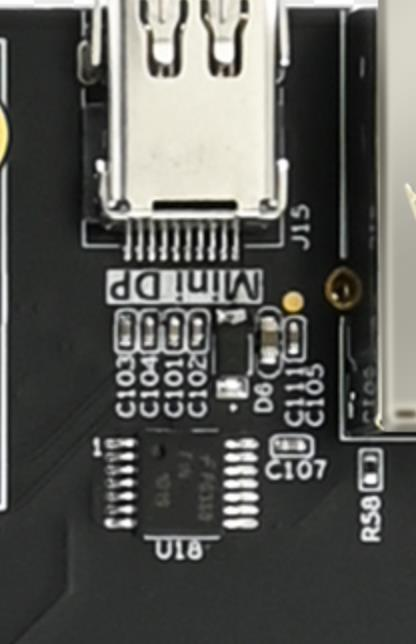

[]()4.9.MiniDP接口

开发板上放置了一个 Mini DP 输出接口,接口信号与 FPGA 的 BANK91/BANK505 相连,详细可参考原理图。

如下是 Mini DP 的引脚分配, 详细电路可以参考开发板原理图。

| MiniDP引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DP_LINE_P0 | MGT_505_TX_P3 | AB39 |

| DP_LINE_N0 | MGT_505_TX_N3 | AB40 |

| DP_LINE_P1 | MGT_505_TX_P2 | AD39 |

| DP_LINE_N1 | MGT_505_TX_N2 | AD40 |

|---|---|---|

| DP_HPD | IO_L7N_HDGC_91 | E10 |

| DP_AUX_OUT | IO_L2N_91 | G11 |

| DP_OE | IO_L2P_91 | H11 |

| DP_AUX_IN | IO_L7P_HDGC_91 | E11 |

| DP_CLK_P_27M | MGT_505_CLK_P2 | AC37 |

| DP_CLK_N_27M | MGT_505_CLK_N2 | AC38 |

编辑

[]() 4.10.USB3.0接口

开发板上放置了四个 USB3.0 主接口,主接口兼容 USB2.0/3.0。接口信号与 FPGA 的 BANK501/BANK505 相连,详细可参考原理图。USB2.0 使用 PHY 芯片 USB3320C-EZK 与 MIO 相连实现。USB3.0 使用 HUB 芯片 GL3523-OTY30 扩展。

如下是 USB2.0/USB3.0 的引脚分配, 详细电路可以参考开发板原理图。

| USB********引脚 | MPSOC********管脚名称 | 管脚位置 |

|---|---|---|

| USBPHY_DATA0 | MIO56 | AA30 |

| USBPHY_DATA1 | MIO57 | AB30 |

| USBPHY_DATA2 | MIO54 | Y29 |

| USBPHY_DATA3 | MIO59 | AC31 |

| USBPHY_DATA4 | MIO60 | AD29 |

| USBPHY_DATA5 | MIO61 | AC32 |

| USBPHY_DATA6 | MIO62 | AD31 |

| USBPHY_DATA7 | MIO63 | AD30 |

| USBPHY_STP | MIO58 | AC29 |

| USBPHY_NXT | MIO55 | AB29 |

| USBPHY_DIR | MIO53 | Y30 |

| USBPHY_CLKOUT | MIO52 | W29 |

| USBPHY_RESET | MIO44 | R29 |

| GT1_USB3_SSTXP | MGT_505_TX_P1 | AF39 |

| GT1_USB3_SSTXN | MGT_505_TX_N1 | AF40 |

| GT1_USB3_SSRXP | MGT_505_RX_P1 | AE41 |

|---|---|---|

| GT1_USB3_SSRXN | MGT_505_RX_N1 | AE42 |

| USB3_CLK_P_26M | MGT_505_CLK_P1 | AE37 |

| USB3_CLK_N_26M | MGT_505_CLK_N1 | AE38 |

编辑

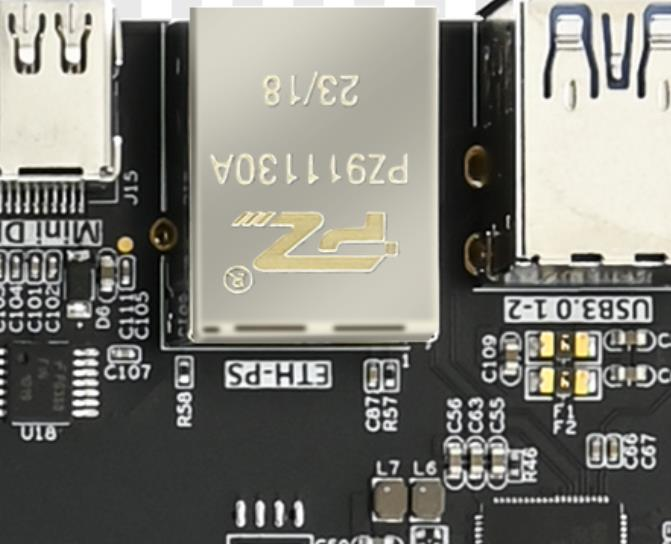

[]()4.11.千兆以太网

开发板上设计了一路千兆以太网,PHY 芯片已集成在核心板上,信号连 接到 PS 端。以太网芯片与 MPSOC 之间通过 RGMII 接口互联,连接对应管脚 见下表,PS 端网口地址是 PHY_AD[2:0]=001,详细电路可以参考开发板原理 图。

| RMGII********信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| GTX_CLK | MIO26_501 | L27 |

| TXD0 | MIO27_501 | L29 |

| TXD1 | MIO28_501 | L28 |

| TXD2 | MIO29_501 | M27 |

| TXD3 | MIO30_501 | L30 |

| TX_EN | MIO31_501 | M28 |

| RX_CLK | MIO32_501 | M30 |

| RXD0 | MIO33_501 | N28 |

| RXD1 | MIO34_501 | P27 |

| RXD2 | MIO35_501 | N29 |

| RXD3 | MIO36_501 | T27 |

| RX_DV | MIO37_501 | N30 |

| MDC | MIO76_502 | AH31 |

| MDIO | MIO77_502 | AG31 |

编辑

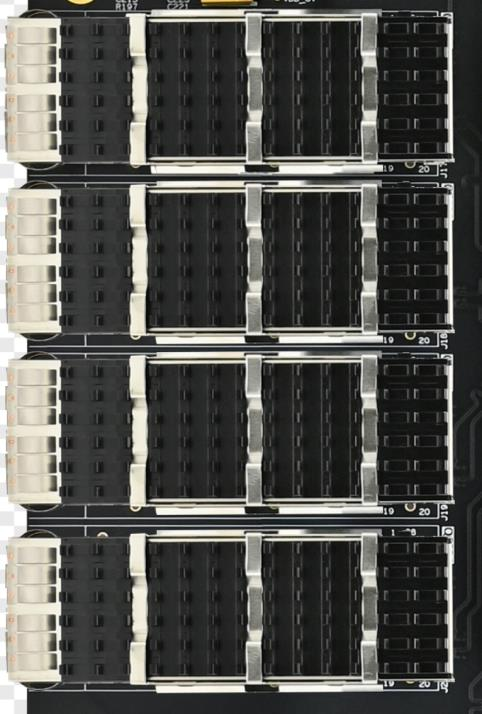

[]() 4.12.QSFP********接口

开发板上设计了四路 40G QSFP 接口,接口信号与 MPSOC 的 BANK94/BANK128 相 连,详细可参考原理图。

如下是 QSFP 的引脚分配, 详细电路可以参考开发板原理图。

| QSFP1********引脚 | 管脚名称 | 管脚位置 | QSFP2********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|---|---|---|

| QSFP1-TX-P0 | MGT_TX_P0_230 | R6 | QSFP2-TX-P0 | MGT_TX_P0_229 | W6 |

| QSFP1-TX-N0 | MGT_TX_N0_230 | R5 | QSFP2-TX-N0 | MGT_TX_N0_229 | W5 |

| QSFP1-TX-P1 | MGT_TX_P1_230 | P8 | QSFP2-TX-P1 | MGT_TX_P1_229 | V8 |

| QSFP1-TX-N1 | MGT_TX_N1_230 | P7 | QSFP2-TX-N1 | MGT_TX_N1_229 | V7 |

| QSFP1-TX-P2 | MGT_TX_P2_230 | N6 | QSFP2-TX-P2 | MGT_TX_P2_229 | U6 |

| QSFP1-TX-N2 | MGT_TX_N2_230 | N5 | QSFP2-TX-N2 | MGT_TX_N2_229 | U5 |

| QSFP1-TX-P3 | MGT_TX_P3_230 | M8 | QSFP2-TX-P3 | MGT_TX_P3_229 | T8 |

| QSFP1-TX-N3 | MGT_TX_N3_230 | M7 | QSFP2-TX-N3 | MGT_TX_N3_229 | T7 |

| QSFP1-RX-P0 | MGT_RX_P0_230 | T4 | QSFP2-RX-P0 | MGT_RX_P0_229 | Y4 |

| QSFP1-RX-N0 | MGT_RX_N0_230 | T3 | QSFP2-RX-N0 | MGT_RX_N0_229 | Y3 |

| QSFP1-RX-P1 | MGT_RX_P1_230 | R2 | QSFP2-RX-P1 | MGT_RX_P1_229 | W2 |

| QSFP1-RX-N1 | MGT_RX_N1_230 | R1 | QSFP2-RX-N1 | MGT_RX_N1_229 | W1 |

| QSFP1-RX-P2 | MGT_RX_P2_230 | P4 | QSFP2-RX-P2 | MGT_RX_P2_229 | V4 |

| QSFP1-RX-N2 | MGT_RX_N2_230 | P3 | QSFP2-RX-N2 | MGT_RX_N2_229 | V3 |

| QSFP1-RX-P3 | MGT_RX_P3_230 | N2 | QSFP2-RX-P3 | MGT_RX_P3_229 | U2 |

| QSFP1-RX-N3 | MGT_RX_N3_230 | N1 | QSFP2-RX-N3 | MGT_RX_N3_229 | U1 |

| QSFP1_LPMODE | IO_1P_94 | F5 | QSFP2_LPMODE | IO_1P_94 | F4 |

| QSFP1_I2C_SCL | IO_2P_94 | E5 | QSFP2_I2C_SCL | IO_2P_94 | C4 |

| QSFP1_I2C_SDA | IO_2N_94 | E4 | QSFP2_I2C_SDA | IO_2N_94 | C3 |

27 / 40

| QSFP3-TX-P0 | MGT_TX_P0_228 | AC6 | QSFP4-TX-P0 | MGT_TX_P0_227 | AG6 |

|---|---|---|---|---|---|

| QSFP3-TX-N0 | MGT_TX_N0_228 | AC5 | QSFP4-TX-N0 | MGT_TX_N0_227 | AG5 |

| QSFP3-TX-P1 | MGT_TX_P1_228 | AB8 | QSFP4-TX-P1 | MGT_TX_P1_227 | AF8 |

| QSFP3-TX-N1 | MGT_TX_N1_228 | AB7 | QSFP4-TX-N1 | MGT_TX_N1_227 | AF7 |

| QSFP3-TX-P2 | MGT_TX_P2_228 | AA6 | QSFP4-TX-P2 | MGT_TX_P2_227 | AE6 |

| QSFP3-TX-N2 | MGT_TX_N2_228 | AA5 | QSFP4-TX-N2 | MGT_TX_N2_227 | AE5 |

| QSFP3-TX-P3 | MGT_TX_P3_228 | Y8 | QSFP4-TX-P3 | MGT_TX_P3_227 | AD8 |

| QSFP3-TX-N3 | MGT_TX_N3_228 | Y7 | QSFP4-TX-N3 | MGT_TX_N3_227 | AD7 |

| QSFP3-RX-P0 | MGT_RX_P0_228 | AD4 | QSFP4-RX-P0 | MGT_RX_P0_227 | AH4 |

| QSFP3-RX-N0 | MGT_RX_N0_228 | AD3 | QSFP4-RX-N0 | MGT_RX_N0_227 | AH3 |

| QSFP3-RX-P1 | MGT_RX_P1_228 | AC2 | QSFP4-RX-P1 | MGT_RX_P1_227 | AG2 |

| QSFP3-RX-N1 | MGT_RX_N1_228 | AC1 | QSFP4-RX-N1 | MGT_RX_N1_227 | AG1 |

| QSFP3-RX-P2 | MGT_RX_P2_228 | AB4 | QSFP4-RX-P2 | MGT_RX_P2_227 | AF4 |

| QSFP3-RX-N2 | MGT_RX_N2_228 | AB3 | QSFP4-RX-N2 | MGT_RX_N2_227 | AF3 |

| QSFP3-RX-P3 | MGT_RX_P3_228 | AA2 | QSFP4-RX-P3 | MGT_RX_P3_227 | AE2 |

| QSFP3-RX-N3 | MGT_RX_N3_228 | AA1 | QSFP4-RX-N3 | MGT_RX_N3_227 | AE1 |

| QSFP3_LPMODE | IO_1P_94 | C6 | QSFP4_LPMODE | IO_1P_94 | C5 |

| QSFP3_I2C_SCL | IO_2P_94 | D4 | QSFP4_I2C_SCL | IO_2P_94 | E3 |

| QSFP3_I2C_SDA | IO_2N_94 | D3 | QSFP4_I2C_SDA | IO_2N_94 | E2 |

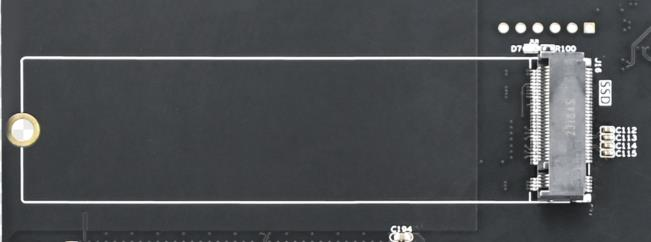

[]() 4.13.SSD********接口

开发板 PS 侧设计了一路 SSD(x1模式),接口类型为 M.2,走 NVME 协议。 SSD 接口的管脚位置如下表,详细电路可以参考开发板原理图。

| SSD********接口 | 管脚名称 | 管脚位置 |

|---|---|---|

| SSD_nRST | MIO64 | AD32 |

| REFCLK_P_100M | MGT_505_CLK_P0 | AG37 |

| REFCLK_N_100M | MGT_505_CLK_N0 | AG38 |

| GT0_SSD_TX_P0 | MGT_505_TX_P0 | AH39 |

| GT0_SSD_TX_N0 | MGT_505_TX_N0 | AH40 |

| GT0_SSD_RX_P0 | MGT_505_RX_P0 | AG41 |

| GT0_SSD_RX_N0 | MGT_505_RX_N0 | AG42 |

编辑

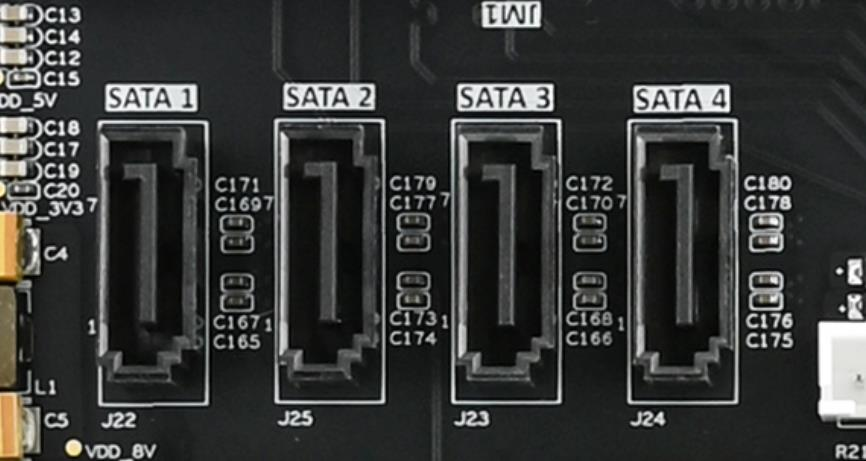

[]() 4.14.SATA********接口

开发板上设计了 4 路 SATA 接口,如下表列出了管脚对应关系,详细电路可以参 考开发板原理图。

| SATA1接口 | 管脚名称 | 管脚位置 |

|---|---|---|

| SATA1_TX_P | MGT_TX_P0_231 | L6 |

| SATA1_TX_N | MGT_TX_N0_231 | L5 |

| SATA1_RX_P | MGT_RX_P0_231 | M4 |

| SATA1_RX_N | MGT_RX_N0_231 | M3 |

| SATA2接口 | 管脚名称 | 管脚位置 |

| SATA2_TX_P | MGT_TX_P1_231 | K4 |

| SATA2_TX_N | MGT_TX_N1_231 | K3 |

| SATA2_RX_P | MGT_RX_P1_231 | L2 |

| SATA2_RX_N | MGT_RX_N1_231 | L1 |

| SATA3接口 | 管脚名称 | 管脚位置 |

| SATA3_TX_P | MGT_TX_P2_231 | J6 |

| SATA3_TX_N | MGT_TX_N2_231 | J5 |

| SATA3_RX_P | MGT_RX_P2_231 | J2 |

| SATA3_RX_N | MGT_RX_N2_231 | J1 |

| SATA4接口 | 管脚名称 | 管脚位置 |

| SATA4_TX_P | MGT_TX_P3_231 | H4 |

| SATA4_TX_N | MGT_TX_N3_231 | H3 |

| SATA4_RX_P | MGT_RX_P3_231 | G2 |

| SATA4_RX_N | MGT_RX_N3_231 | G1 |

编辑

[]()4.15.LED

核心板设计了三路 LED,开发板设计了四路 LED,共计七路 LED。LED 高电平亮, 低电平灭。详细电路可参考开发板原理图。

| LED********位号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1(核心板) | IO-T2U-68 | C14 |

| LED2(核心板) | IO-T3U-68 | A15 |

| LED3(核心板) | IO-T2U-67 | AP11 |

| LED1(开发板) | IO-6P-91 | F13 |

| LED2(开发板) | IO-6N-91 | F12 |

| LED3(开发板) | IO-8P-91 | E12 |

| LED4(开发板) | IO-8N-91 | D12 |

编辑

编辑

[]()4.16.按键

开发板设计了四路按键。按键默认高电平, 按下为低电平,按键连到 PL 侧,管 脚位置如下表。

| KEY 1 | IO-L9P-91 | D11 |

|---|---|---|

| KEY 2 | IO-L9N-91 | C11 |

| KEY 3 | IO-L11P-91 | B12 |

| KEY 4 | IO-L11N-91 | B11 |

编辑

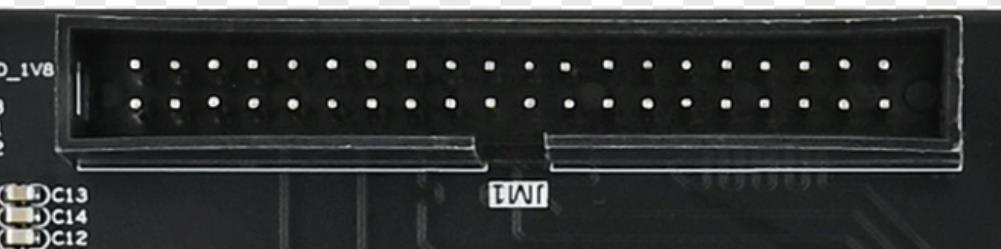

[]()4.17.40P********扩展接口

开发板板载了两个 40P 2.54mm 间距的简易牛角座,用于扩展信号的连接,

信号与 FPGA 的 BANK90/93 连接,电平为 3.3V。如下表标出了信号所在的芯片 位置,详细连接关系参考原理图部分。

| JM1信号顺序 | 管脚名称 | 管脚位置 | JM1信号顺序 | 管脚名称 | 管脚位置 |

|---|---|---|---|---|---|

| 5 | IO_L1P_90 | N11 | 6 | IO_L9P_90 | M10 |

| 7 | IO_L1N_90 | N10 | 8 | IO_L9N_90 | L10 |

| 9 | IO_L2P_90 | P12 | 10 | IO_L6P_90 | M12 |

| 11 | IO_L2N_90 | N12 | 12 | IO_L6N_90 | M11 |

| 13 | IO_L5P_90 | N13 | 14 | IO_L10P_90 | K11 |

| 15 | IO_L5N_90 | M13 | 16 | IO_L10N_90 | K10 |

| 17 | IO_L4P_90 | P14 | 18 | IO_L7P_90 | L12 |

| 19 | IO_L4N_90 | N14 | 20 | IO_L7N_90 | K12 |

| 21 | IO_L8P_90 | L14 | 22 | IO_L12P_90 | J13 |

| 23 | IO_L8N_90 | L13 | 24 | IO_L12N_90 | J12 |

| 25 | IO_3P_90 | R14 | 26 | IO_L11P_90 | K14 |

| 27 | IO_L3N_90 | P13 | 28 | IO_L11N_90 | J14 |

| 29 | IO_L4P_93 | F9 | 30 | IO_L3P_93 | J9 |

| 31 | IO_L4N_93 | E9 | 32 | IO_L3N_93 | H9 |

| 37 | IO_L12P_93 | D9 | 38 | IO_L6P_93 | G8 |

| 39 | IO_L12N_93 | C9 | 40 | IO_L6N_93 | F8 |

编辑

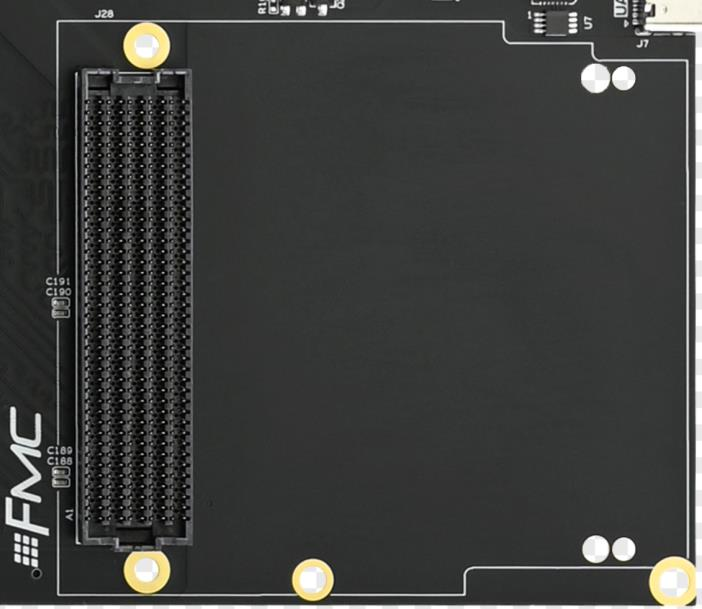

[]() 4.18.FMC********扩展接口

开发板上设计了两路 FMC 连接器,一路 HPC 接口、一路 LPC 接口,如下表列出 了信号对应关系。详细连接关系参考原理图部分。

31 / 40

| 序号 | FMC-HPC 管脚 | MPSOC 管脚名称 | 管脚位置 |

|---|---|---|---|

| A2 | DP1_M2C_P | MGT_RX_P1_128 | V39 |

| A3 | DP1_M2C_N | MGT_RX_N1_128 | V40 |

| A6 | DP2_M2C_P | MGT_RX_P2_128 | U41 |

| A7 | DP2_M2C_N | MGT_RX_N2_128 | U42 |

| A10 | DP3_M2C_P | MGT_RX_P3_128 | T39 |

| A11 | DP3_M2C_N | MGT_RX_N3_128 | T40 |

| A14 | DP4_M2C_P | MGT_RX_P0_129 | R41 |

| A15 | DP4_M2C_N | MGT_RX_N0_129 | R42 |

| A18 | DP5_M2C_P | MGT_RX_P1_129 | P39 |

| A19 | DP5_M2C_N | MGT_RX_N1_129 | P40 |

| A22 | DP1_C2M_P | MGT_TX_P1_128 | W36 |

| A23 | DP1_C2M_N | MGT_TX_N1_128 | W37 |

| A26 | DP2_C2M_P | MGT_TX_P2_128 | V34 |

| A27 | DP2_C2M_N | MGT_TX_N2_128 | V35 |

| A30 | DP3_C2M_P | MGT_TX_P3_128 | U36 |

| A31 | DP3_C2M_N | MGT_TX_N3_128 | U37 |

| A34 | DP4_C2M_P | MGT_TX_P0_129 | T34 |

| A35 | DP4_C2M_N | MGT_TX_N0_129 | T35 |

| A38 | DP5_C2M_P | MGT_TX_P1_129 | R36 |

| A39 | DP5_C2M_N | MGT_TX_N1_129 | R37 |

| B12 | DP7_M2C_P | MGT_RX_P3_129 | M39 |

| B13 | DP7_M2C_N | MGT_RX_N3_129 | M40 |

| B16 | DP6_M2C_P | MGT_RX_P2_129 | N41 |

| B17 | DP6_M2C_N | MGT_RX_N2_129 | N42 |

| B20 | GBTCLK1_M2C_P | MGT_CLK0_P_129 | W32 |

| B21 | GBTCLK1_M2C_N | MGT_CLK0_N_129 | W33 |

| B32 | DP7_C2M_P | MGT_TX_P3_129 | N36 |

| B33 | DP7_C2M_N | MGT_TX_N3_129 | N37 |

| B36 | DP6_C2M_P | MGT_TX_P2_129 | P34 |

| B37 | DP6_C2M_N | MGT_TX_N2_129 | P35 |

| C2 | DP0_C2M_P | MGT_TX_P0_128 | Y34 |

| C3 | DP0_C2M_N | MGT_TX_N0_128 | Y35 |

| C6 | DP0_M2C_P | MGT_RX_P0_128 | W41 |

| C7 | DP0_M2C_N | MGT_RX_N0_128 | W42 |

| C10 | LA06_P | IO_L18P_65 | AR28 |

| C11 | LA06_N | IO_L18N_65 | AT28 |

| C14 | LA10_P | IO_L16P_65 | AN27 |

| C15 | LA10_N | IO_L16N_65 | AP27 |

| C18 | LA14_P | IO_L5P_65 | AY27 |

| C19 | LA14_N | IO_L5N_65 | AY28 |

| C22 | LA18_P_CC | IO_L11P_SRCC_65 | AU25 |

| C23 | LA18_N_CC | IO_L11N_SRCC_65 | AU26 |

| C26 | LA27_P | IO_L15P_64 | AN22 |

| C27 | LA27_N | IO_L15N_64 | AP22 |

| C30 | SCL | IO_L2P_93 | H14 |

| C31 | SDA | IO_L2N_93 | G13 |

| D4 | GBTCLK0_M2C_P | MGT_CLK0_P_128 | AB34 |

32 / 40

| D5 | GBTCLK0_M2C_N | MGT_CLK0_N_128 | AB35 |

|---|---|---|---|

| D8 | LA01_P_CC | IO_L13P_MRCC_65 | AR27 |

| D9 | LA01_N_CC | IO_L13N_MRCC_65 | AT27 |

| D11 | LA05_P | IO_L17P_65 | AM28 |

| D12 | LA05_N | IO_L17N_65 | AN28 |

| D14 | LA09_P | IO_L15P_65 | AM26 |

| D15 | LA09_N | IO_L15N_65 | AN26 |

| D17 | LA13_P | IO_L6P_65 | BA28 |

| D18 | LA13_N | IO_L6N_65 | BB28 |

| D20 | LA17_P_CC | IO_L12P_MRCC_65 | AT25 |

| D21 | LA17_N_CC | IO_L12N_MRCC_65 | AT26 |

| D23 | LA23_P | IO_L8P_65 | AV26 |

| D24 | LA23_N | IO_L8N_65 | AW26 |

| D26 | LA26_P | IO_L7P_64 | AU23 |

| D27 | LA26_N | IO_L7N_64 | AV23 |

| E2 | HA01_P_CC | IO_L13P_MRCC_66 | AV17 |

| E3 | HA01_N_CC | IO_L13N_MRCC_66 | AV16 |

| E6 | HA05_P | IO_L15P_66 | AU18 |

| E7 | HA05_N | IO_L15N_66 | AV18 |

| E9 | HA09_P | IO_L16P_66 | AR18 |

| E10 | HA09_N | IO_L16N_66 | AT18 |

| E12 | HA13_P | IO_L5P_66 | AY15 |

| E13 | HA13_N | IO_L5N_66 | AY14 |

| E15 | HA16_P | IO_L6P_66 | BA13 |

| E16 | HA16_N | IO_L6N_66 | BB13 |

| E18 | HA20_P | IO_L8P_66 | BA11 |

| E19 | HA20_N | IO_L8N_66 | BB11 |

| E21 | HB03_P | IO_L15P_67 | AR15 |

| E22 | HB03_N | IO_L15N_67 | AR14 |

| E24 | HB05_P | IO_L2P_67 | BB9 |

| E25 | HB05_N | IO_L2N_67 | BB8 |

| E27 | HB09_P | IO_L20P_67 | AJ15 |

| E28 | HB09_N | IO_L20N_67 | AK15 |

| E30 | HB13_P | IO_L24P_67 | AJ14 |

| E31 | HB13_N | IO_L24N_67 | AK14 |

| E33 | HB19_P | IO_L9P_67 | AW11 |

| E34 | HB19_N | IO_L9N_67 | AW10 |

| E36 | HB21_P | IO_L10P_67 | AV9 |

| E37 | HB21_N | IO_L10N_67 | AV8 |

| F4 | HA00_P_CC | IO_L14P_SRCC_66 | AT15 |

| F5 | HA00_N_CC | IO_L14N_SRCC_66 | AU15 |

| F7 | HA04_P | IO_L12P_MRCC_66 | AU14 |

| F8 | HA04_N | IO_L12N_MRCC_66 | AV14 |

| F10 | HA08_P | IO_L4P_66 | BA15 |

| F11 | HA08_N | IO_L4N_66 | BB15 |

| F13 | HA12_P | IO_L10P_66 | AU13 |

| F14 | HA12_N | IO_L10N_66 | AV13 |

| F16 | HA15_P | IO_L7P_66 | AY12 |

33 / 40

| F17 | HA15_N | IO_L7N_66 | BA12 |

|---|---|---|---|

| F19 | HA19_P | IO_L9P_66 | BA10 |

| F20 | HA19_N | IO_L9N_66 | BB10 |

| F22 | HB02_P | IO_L1P_67 | AW9 |

| F23 | HB02_N | IO_L1N_67 | AY9 |

| F25 | HB04_P | IO_L3P_67 | AW8 |

| F26 | HB04_N | IO_L3N_67 | AY8 |

| F28 | HB08_P | IO_L4P_67 | BA8 |

| F29 | HB08_N | IO_L4N_67 | BA7 |

| F31 | HB12_P | IO_L18P_67 | AM10 |

| F32 | HB12_N | IO_L18N_67 | AN10 |

| F34 | HB16_P | IO_L7P_67 | AV12 |

| F35 | HB16_N | IO_L7N_67 | AW12 |

| F37 | HB20_P | IO_L16P_67 | AN12 |

| F38 | HB20_N | IO_L16N_67 | AP12 |

| J2 | CLK3_M2C_P | IO_L13P_MRCC_67 | AR13 |

| J3 | CLK3_M2C_N | IO_L13N_MRCC_67 | AR12 |

| J6 | HA03_P | IO_L3P_66 | AN18 |

| J7 | HA03_N | IO_L3N_66 | AN17 |

| J9 | HA07_P | IO_L18P_66 | AT16 |

| J10 | HA07_N | IO_L18N_66 | AU16 |

| J12 | HA11_P | IO_L2P_66 | BA16 |

| J13 | HA11_N | IO_L2N_66 | BB16 |

| J15 | HA14_P | IO_L24P_66 | AN16 |

| J16 | HA14_N | IO_L24N_66 | AP16 |

| J18 | HA18_P | IO_L23P_66 | AL16 |

| J19 | HA18_N | IO_L23N_66 | AM16 |

| J21 | HA22_P | IO_L20P_66 | AL18 |

| J22 | HA22_N | IO_L20N_66 | AM18 |

| J24 | HB01_P | IO_L23P_67 | AM13 |

| J25 | HB01_N | IO_L23N_67 | AN13 |

| J27 | HB07_P | IO_L22P_67 | AN14 |

| J28 | HB07_N | IO_L22N_67 | AP14 |

| J30 | HB11_P | IO_L19P_67 | AL15 |

| J31 | HB11_N | IO_L19N_67 | AM15 |

| J33 | HB15_P | IO_L21P_67 | AL14 |

| J34 | HB15_N | IO_L21N_67 | AM14 |

| J36 | HB18_P | IO_L6P_67 | BB5 |

| J37 | HB18_N | IO_L6N_67 | BB4 |

| K4 | CLK2_M2C_P | IO_L12P_MRCC_67 | AT11 |

| K5 | CLK2_M2C_N | IO_L12N_MRCC_67 | AT10 |

| K7 | HA02_P | IO_L21P_66 | AW17 |

| K8 | HA02_N | IO_L21N_66 | AW16 |

| K10 | HA06_P | IO_L17P_66 | AR17 |

| K11 | HA06_N | IO_L17N_66 | AT17 |

| K13 | HA10_P | IO_L1P_66 | AY17 |

| K14 | HA10_N | IO_L1N_66 | BA17 |

| K16 | HA17_P_CC | IO_L11P_SRCC_66 | AW15 |

34 / 40

| K17 | HA17_N_CC | IO_L11N_SRCC_66 | AW14 |

|---|---|---|---|

| K19 | HA21_P | IO_L22P_66 | AJ17 |

| K20 | HA21_N | IO_L22N_66 | AK17 |

| K22 | HA23_P | IO_L19P_66 | AJ18 |

| K23 | HA23_N | IO_L19N_66 | AK18 |

| K25 | HB00_P_CC | IO_L11P_SRCC_67 | AT13 |

| K26 | HB00_N_CC | IO_L11N_SRCC_67 | AT12 |

| K28 | HB06_P_CC | IO_L8P_67 | AU11 |

| K29 | HB06_N_CC | IO_L8N_67 | AV11 |

| K31 | HB10_P | IO_L17P_67 | AM11 |

| K32 | HB10_N | IO_L17N_67 | AN11 |

| K34 | HB14_P | IO_L5P_67 | BA6 |

| K35 | HB14_N | IO_L5N_67 | BB6 |

| K37 | HB17_P_CC | IO_L14P_SRCC_67 | AP10 |

| K38 | HB17_N_CC | IO_L14N_SRCC_67 | AR10 |

| G2 | CLK1_M2C_P | IO_L19P_64 | AM19 |

| G3 | CLK1_M2C_N | IO_L19N_64 | AN19 |

| G6 | LA00_P_CC | IO_L14P_SRCC_65 | AR24 |

| G7 | LA00_N_CC | IO_L14N_SRCC_65 | AR25 |

| G9 | LA03_P | IO_L7P_65 | AU24 |

| G10 | LA03_N | IO_L7N_65 | AV24 |

| G12 | LA08_P | IO_L10P_65 | AU28 |

| G13 | LA08_N | IO_L10N_65 | AV28 |

| G15 | LA12_P | IO_L24P_65 | AJ24 |

| G16 | LA12_N | IO_L24N_65 | AK24 |

| G18 | LA16_P | IO_L21P_65 | AM24 |

| G19 | LA16_N | IO_L21N_65 | AN24 |

| G21 | LA20_P | IO_L4P_65 | BA26 |

| G22 | LA20_N | IO_L4N_65 | BB26 |

| G24 | LA22_P | IO_L3P_65 | AY25 |

| G25 | LA22_N | IO_L3N_65 | BA25 |

| G27 | LA25_P | IO_L8P_64 | AV22 |

| G28 | LA25_N | IO_L8N_64 | AW22 |

| G30 | LA29_P | IO_L1P_64 | BA23 |

| G31 | LA29_N | IO_L1N_64 | BB23 |

| G33 | LA31_P | IO_L2P_64 | AY23 |

| G34 | LA31_N | IO_L2N_64 | AY22 |

| G36 | LA33_P | IO_L20P_64 | AM21 |

| G37 | LA33_N | IO_L20N_64 | AM20 |

| H4 | CLK0_M2C_P | IO_L12P_MRCC_64 | AU20 |

| H5 | CLK0_M2C_N | IO_L12N_MRCC_64 | AV19 |

| H7 | LA02_P | IO_L2P_65 | BB24 |

| H8 | LA02_N | IO_L2N_65 | BB25 |

| H10 | LA04_P | IO_L9P_65 | AV27 |

| H11 | LA04_N | IO_L9N_65 | AW27 |

| H13 | LA07_P | IO_L20P_65 | AP24 |

| H14 | LA07_N | IO_L20N_65 | AP25 |

| H16 | LA11_P | IO_L22P_65 | AM23 |

35 / 40

| H17 | LA11_N | IO_L22N_65 | AN23 |

|---|---|---|---|

| H19 | LA15_P | IO_L19P_65 | AR23 |

| H20 | LA15_N | IO_L19N_65 | AT23 |

| H22 | LA19_P | IO_L23P_65 | AK23 |

| H23 | LA19_N | IO_L23N_65 | AL23 |

| H25 | LA21_P | IO_L1P_65 | AW24 |

| H26 | LA21_N | IO_L1N_65 | AY24 |

| H28 | LA24_P | IO_L24P_64 | AJ22 |

| H29 | LA24_N | IO_L24N_64 | AK22 |

| H31 | LA28_P | IO_L21P_64 | AL22 |

| H32 | LA28_N | IO_L21N_64 | AL21 |

| H34 | LA30_P | IO_L22P_64 | AK20 |

| H35 | LA30_N | IO_L22N_64 | AK19 |

| H37 | LA32_P | IO_L3P_64 | BA22 |

| H38 | LA32_N | IO_L3N_64 | BA21 |

编辑

| 序号 | FMC-LPC 管脚 | 管脚名称 | 管脚位置 |

|---|---|---|---|

| C2 | DP0_C2M_P | MGT_TX_P3_131 | E36 |

| C3 | DP0_C2M_N | MGT_TX_N3_131 | E37 |

| C6 | DP0_M2C_P | MGT_RX_P3_131 | D39 |

| C7 | DP0_M2C_N | MGT_RX_N3_131 | D40 |

| C10 | LA06_P | IO_L3P_68 | M17 |

| C11 | LA06_N | IO_L3N_68 | M16 |

| C14 | LA10_P | IO_L4P_68 | M15 |

| C15 | LA10_N | IO_L4N_68 | L15 |

| C18 | LA14_P | IO_L17P_68 | A14 |

| C19 | LA14_N | IO_L17N_68 | A13 |

| C22 | LA18_P_CC | IO_L14P_SRCC_68 | E15 |

| C23 | LA18_N_CC | IO_L14N_SRCC_68 | D14 |

| C26 | LA27_P | IO_L6P_64 | BA18 |

| C27 | LA27_N | IO_L6N_64 | BB18 |

| C30 | SCL | IO_L4P_91 | J8 |

36 / 40

| C31 | SDA | IO_L4N_91 | H8 |

|---|---|---|---|

| D4 | GBTCLK0_M2C_P | MGT_CLK0_P_131 | L32 |

| D5 | GBTCLK0_M2C_N | MGT_CLK0_N_131 | L33 |

| D8 | LA01_P_CC | IO_L11P_SRCC_68 | G17 |

| D9 | LA01_N_CC | IO_L11N_SRCC_68 | F17 |

| D11 | LA05_P | IO_L24P_68 | B18 |

| D12 | LA05_N | IO_L24N_68 | A18 |

| D14 | LA09_P | IO_L10P_68 | G18 |

| D15 | LA09_N | IO_L10N_68 | F18 |

| D17 | LA13_P | IO_L15P_68 | D13 |

| D18 | LA13_N | IO_L15N_68 | C13 |

| D20 | LA17_P_CC | IO_L12P_MRCC_68 | G16 |

| D21 | LA17_N_CC | IO_L12N_MRCC_68 | F15 |

| D23 | LA23_P | IO_L16P_68 | B13 |

| D24 | LA23_N | IO_L16N_68 | A12 |

| D26 | LA26_P | IO_L5P_64 | BB20 |

| D27 | LA26_N | IO_L5N_64 | BB19 |

| G2 | CLK1_M2C_P | IO_L13P_MRCC_64 | AT22 |

| G3 | CLK1_M2C_N | IO_L13N_MRCC_64 | AT21 |

| G6 | LA00_P_CC | IO_L13P_MRCC_68 | F14 |

| G7 | LA00_N_CC | IO_L13N_MRCC_68 | E14 |

| G9 | LA03_P | IO_L22P_68 | B17 |

| G10 | LA03_N | IO_L22N_68 | A17 |

| G12 | LA08_P | IO_L2P_68 | P16 |

| G13 | LA08_N | IO_L2N_68 | N16 |

| G15 | LA12_P | IO_L1P_68 | P15 |

| G16 | LA12_N | IO_L1N_68 | N15 |

| G18 | LA16_P | IO_L5P_68 | K16 |

| G19 | LA16_N | IO_L5N_68 | K15 |

| G21 | LA20_P | IO_L19P_68 | E16 |

| G22 | LA20_N | IO_L19N_68 | D16 |

| G24 | LA22_P | IO_L20P_68 | C16 |

| G25 | LA22_N | IO_L20N_68 | B16 |

| G27 | LA25_P | IO_L4P_64 | AY20 |

| G28 | LA25_N | IO_L4N_64 | BA20 |

| G30 | LA29_P | IO_L14P_SRCC_64 | AT20 |

| G31 | LA29_N | IO_L14N_SRCC_64 | AU19 |

| G33 | LA31_P | IO_L23P_64 | AJ21 |

| G34 | LA31_N | IO_L23N_64 | AJ20 |

| G36 | LA33_P | IO_L18P_64 | AP19 |

| G37 | LA33_N | IO_L18N_64 | AR19 |

| H4 | CLK0_M2C_P | IO_L11P_SRCC_64 | AU21 |

| H5 | CLK0_M2C_N | IO_L11N_SRCC_64 | AV21 |

| H7 | LA02_P | IO_L23P_68 | D18 |

| H8 | LA02_N | IO_L23N_68 | C18 |

| H10 | LA04_P | IO_L21P_68 | E17 |

| H11 | LA04_N | IO_L21N_68 | D17 |

| H13 | LA07_P | IO_L9P_68 | J18 |

37 / 40

| H14 | LA07_N | IO_L9N_68 | H18 |

|---|---|---|---|

| H16 | LA11_P | IO_L6P_68 | L17 |

| H17 | LA11_N | IO_L6N_68 | K17 |

| H19 | LA15_P | IO_L8P_68 | J16 |

| H20 | LA15_N | IO_L8N_68 | H16 |

| H22 | LA19_P | IO_L7P_68 | H15 |

| H23 | LA19_N | IO_L7N_68 | G15 |

| H25 | LA21_P | IO_L18P_68 | C15 |

| H26 | LA21_N | IO_L18N_68 | B15 |

| H28 | LA24_P | IO_L17P_64 | AP20 |

| H29 | LA24_N | IO_L17N_64 | AR20 |

| H31 | LA28_P | IO_L10P_64 | AY19 |

| H32 | LA28_N | IO_L10N_64 | AY18 |

| H34 | LA30_P | IO_L16P_64 | AN21 |

| H35 | LA30_N | IO_L16N_64 | AP21 |

| H37 | LA32_P | IO_L9P_64 | AW20 |

| H38 | LA32_N | IO_L9N_64 | AW19 |

编辑

编辑

编辑

[]()4.19.PCIE3.0********接口

开发板板载了 PCIE3.0 接口,为 X8 接口,如下表列出了PCIE 接口对应关系。

| PCIE********3.0 | 管脚名称 | 管脚位置 |

|---|---|---|

| PERST_N | IO_20N_10 | A9 |

| REF_CLK_P | MGT_110_CLK_P0 | AK12 |

| REF_CLK_N | MGT_110_CLK_N0 | AK11 |

| PER0_P | MGT_TX_P0_224 | AY4 |

| PER0_N | MGT_TX_N0_224 | AY3 |

| PER1_P | MGT_TX_P1_224 | AW6 |

| PER1_N | MGT_TX_N1_224 | AW5 |

| PER2_P | MGT_TX_P2_224 | AU6 |

| PER2_N | MGT_TX_N2_224 | AU5 |

| PER3_P | MGT_TX_P3_224 | AT8 |

| PER3_N | MGT_TX_N3_224 | AT7 |

| PER4_P | MGT_TX_P0_225 | AR6 |

| PER4_N | MGT_TX_N0_225 | AR5 |

| PER5_P | MGT_TX_P1_225 | AP8 |

| PER5_N | MGT_TX_N1_225 | AP7 |

| PER6_P | MGT_TX_P2_225 | AN6 |

38 / 40

| PER6_N | MGT_TX_N2_225 | AN5 |

|---|---|---|

| PER7_P | MGT_TX_P3_225 | AM8 |

| PER7_N | MGT_TX_N3_225 | AM7 |

| PET0_P | MGT_RX_P0_224 | BA2 |

| PET0_N | MGT_RX_N0_224 | BA1 |

| PET1_P | MGT_RX_P1_224 | AW2 |

| PET1_N | MGT_RX_N1_224 | AW1 |

| PET2_P | MGT_RX_P2_224 | AV4 |

| PET2_N | MGT_RX_N2_224 | AV3 |

| PET3_P | MGT_RX_P3_224 | AU2 |

| PET3_N | MGT_RX_N3_224 | AU1 |

| PET4_P | MGT_RX_P0_225 | AT4 |

| PET4_N | MGT_RX_N0_225 | AT3 |

| PET5_P | MGT_RX_P1_225 | AR2 |

| PET5_N | MGT_RX_N1_225 | AR1 |

| PET6_P | MGT_RX_P2_225 | AP4 |

| PET6_N | MGT_RX_N2_225 | AP3 |

| PET7_P | MGT_RX_P3_225 | AN2 |

| PET7_N | MGT_RX_N3_225 | AN1 |

编辑

[]()4.20.双路MIPICSI********接口

开发板设计了双路 mipi csi 接口,如下表列出了 mipi 信号对应关系。

| MIPI1信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| MIPI1_D_P0 | IO_8P_68 | J16 |

| MIPI1_D_N0 | IO_8N_68 | H16 |

| MIPI1_D_P1 | IO_18P_68 | C15 |

| MIPI1_D_N1 | IO_18N_68 | B15 |

| MIPI1_CLK_P | IO_7P_68 | H15 |

| MIPI1_CLK_N | IO_7N_68 | G15 |

| CAM1_GPIO | IO_10N_50 | B6 |

| CAM1_CLK | IO_10P_50 | B5 |

| CAM1_SCL | IO_9P_50 | A5 |

| CAM1_SDA | IO_9N_50 | A4 |

| MIPI2信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| MIPI2_D_P0 | IO_17P_64 | AP20 |

39 / 40

| MIPI2_D_N0 | IO_17N_64 | AR20 |

|---|---|---|

| MIPI2_D_P1 | IO_9P_64 | AW20 |

| MIPI2_D_N1 | IO_9N_64 | AW19 |

| MIPI2_CLK_P | IO_16P_64 | AN21 |

| MIPI2_CLK_N | IO_16N_64 | AP21 |

| CAM2_GPIO | IO_L8N_HDGC_50 | B3 |

| CAM2_CLK | IO_L8P_HDGC_50 | A3 |

| CAM2_SCL | IO_L6P_HDGC_50 | D2 |

| CAM2_SDA | IO_L6N_HDGC_50 | C1 |

编辑

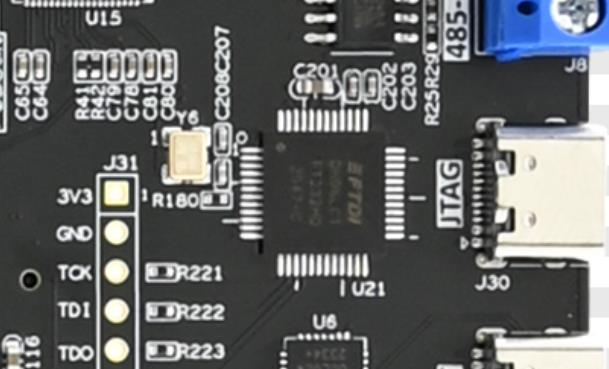

[]() 4.21.USB转JTAG********下载器

开发板板载了一个 USB 转 JTAG 下载器,安装好 Vivado 软件后使用 USB 线连接 好 JTAG 对应的 USB 口,即可实现调试下载,非常方便。如下是接口在开发板上的位 置图。

编辑

审核编辑 黄宇

- 相关推荐

- 热点推荐

- FPGA

- JTAG

- 开发板

- 核心板

- UltraScale

-

Stellaris Microcontroller开发板核心板原理图2016-12-14 984

-

米尔发布新品Zynq UltraScale+ MPSoC核心板2019-05-24 4644

-

MPSOC开发板教程之HELLO WORLD2019-08-02 1054

-

MYD-CZU3EG开发板的Linux开发手册免费下载2019-08-12 1135

-

AX7Z035 ZYNQ开发板的用户手册资料免费下载2020-10-22 3484

-

基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 开发板评测2021-04-28 12978

-

米尔电子zynq ultrascale+ mpsoc底板外设资源清单分享2022-01-07 932

-

Combat开发板用户手册2022-09-16 842

-

Zynq UltraScale ZU19EG MPSOC评估板2022-09-26 1354

-

5702开发板用户手册2022-12-08 1913

-

瑞芯微RK3568核心板/评估板/开发板/工控板用户手册2023-08-01 2013

-

PZ/璞致【PZ-ZU19EG-KFB】—ZYNQ UltraScale + 赋能异构计算与高性能嵌入式系统开发2025-07-24 2308

-

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台2025-08-06 1379

-

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册2025-09-15 7422

-

fpga开发板 璞致 Kintex UltraScale Plus PZ-KU3P 与 PZ-KU5P核心板与开发板用户手册2025-09-26 1721

全部0条评论

快来发表一下你的评论吧 !