CoWoP能否挑战CoWoS的霸主地位

描述

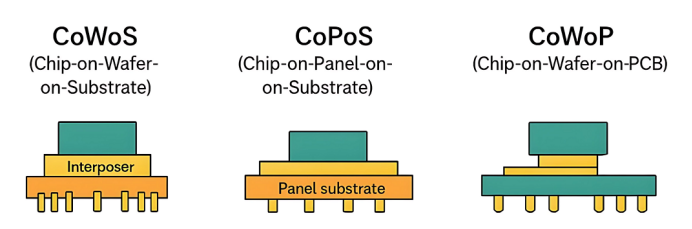

在半导体行业追逐更高算力、更低成本的赛道上,先进封装技术成了关键突破口。过去几年,台积电的CoWoS(Chip-on-Wafer-on-Substrate)技术凭借对AI芯片需求的精准适配,成了先进封装的代名词。但近期,CoWoP(ChiponWaferonPCB)技术横空出世,迅速引发行业关注——它能否挑战CoWoS的霸主地位?今天我们就来拆解这个封装界的“新选手”。

CoWoS:光环与困境

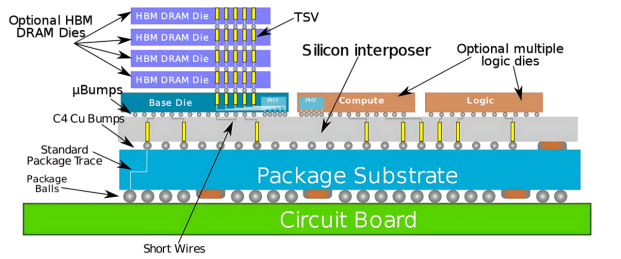

要懂CoWoP的价值,得先看清CoWoS的现状。作为2.5D封装的代表,CoWoS靠硅中介层将GPU与HBM内存集成,再用ABF基板承载芯片、连接主板。这种设计突破了传统封装的带宽和能效瓶颈,靠高密度互连提升了数据吞吐能力,还缓解了“内存墙”问题,完美适配了AI训练的需求。

可随着技术迭代,CoWoS的短板逐渐暴露。最突出的是成本——ABF基板占封装总成本的40%-50%,且价格还在随技术升级上涨。其次是信号损耗,多层基板结构会让NVLink和HBM信号衰减,影响传输完整性。另外,硅中介层的依赖限制了HBM堆叠数量和芯片尺寸,可AI芯片对更高带宽的需求却在不断增加。行业急需新方案破局,CoWoP就在这时登场了。

CoWoP:换道超车的核心优势

CoWoP算是CoWoS的“衍生改进版”,但在技术路径上做了关键革新:

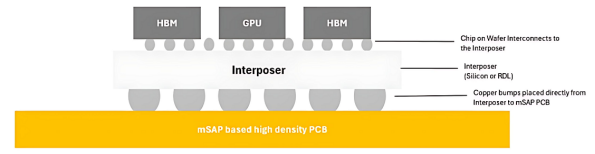

完成芯片-晶圆中介层制造后,直接把中介层装在PCB(又称平台PCB)上,省去了CoWoS中“中介层绑定ABF基板”的步骤,形成“芯片-硅中介层-PCB”的简化结构。

这种设计的优势很直观:

信号传输上,少了一层基板,路径更短更直接,NVLink和HBM的通信损耗大幅降低,高速接口的带宽利用率和延迟表现都能提升;电源方面,电压调节器可更靠近GPU,减少寄生参数,适配高功耗芯片需求。

散热也是CoWoP的亮点——取消芯片上盖(lid)后,芯片能直接接触散热装置,液冷、热管等技术更容易贴合,再加上供电损耗减少,双重优化让散热效果远超传统封装。

成本降低更是关键。CoWoP完全省去了昂贵的ABF基板,还去掉了BGA焊球和封装盖,整体成本能降低30%-50%,既规避了基板成本上涨压力,也为AI芯片大规模应用提供了成本空间。

商业化:看起来美,做起来难

尽管CoWoP潜力不小,但从实验室走向量产,还有不少坎要跨:

· 技术层面,PCB精度是最大瓶颈。目前最先进的mSAP技术能实现25/25微米的线宽/线距,可ABF基板能做到亚10微米级别,差距明显;而且平台PCB得达到封装级的布线密度、平整度和材料控制,对厂商技术要求极高。

· 良率和维修也很棘手。CoWoP中GPU裸晶直接焊在主板上,一旦出问题,整个主板可能报废,容错空间小;同时,芯片、中介层、PCB的协同设计更复杂,会增加开发成本和难度。

· 技术转移成本也不能忽视。从现有封装技术转向CoWoP,产业链上下游(材料/设备/封装厂商)都要调整升级,既需大量资金,也需时间磨合。

产业链影响:有人欢喜有人忧

CoWoP的出现,会给半导体产业链带来明显冲击。对ABF基板厂商来说,这是不小的挑战——若CoWoP大规模应用,基板附加值可能大幅减少,复杂信号路由会转移到中介层的RDL层,高端PCB则会承担封装内路由工作。

但对PCB制造商而言,这是难得的机遇。具备先进mSAP能力、懂基板/封装工艺的企业会更有优势,能提供高质量基板级PCB(SLP)的厂商,有望在CoWoP量产时抢占市场。

未来展望:技术竞赛未完待续

目前,CoWoP的讨论还在升温,但距离大规模量产还有不少时间。业内分析师郭明錤认为,CoWoP要在2028年英伟达RubinUltra时期量产,已是“很乐观的预期”——毕竟高规格芯片所需的SLP生态构建难度大,且CoWoP与CoPoS(另一种CoWoS潜在替代技术)同步推进,也会增加创新风险。

不过,无论CoWoP最终能否颠覆CoWoS,它都为先进封装技术注入了新活力。半导体行业对更高性能、更低成本的追求从未停止,未来或许还会有更多新技术出现,每一次突破都可能带来行业变革。这场技术竞赛的最终赢家是谁,还需要时间给出答案。

-

CoWoP封装的概念、流程与优势2025-08-12 3416

-

最近大火的CoWoP跟CoWoS、CoPoS有什么区别?2025-08-10 6723

-

CoWoS先进封装技术介绍2024-12-17 6070

-

华为鲲鹏挑战英特尔霸主地位 华为的机会在云端2020-02-08 2485

-

移动通信领域的他 亲眼目睹了美国逐步丧失电信霸主地位2019-07-10 4360

-

英特尔前总裁发布Arm服务器芯片,挑战老东家霸主地位!2018-09-20 4828

-

自然光电视亮相,它能挑战激光电视的大屏霸主地位吗?2018-08-24 871

-

国产AMOLED产能迎来大爆发 挑战三星、LG霸主地位2018-07-05 8127

-

华为:将透过AI挑战霸主地位2018-02-05 870

-

挑战英特尔霸主地位 AMD推出Naples欲抢夺服务器芯片市场2017-03-08 1090

-

诺基亚8卷土重来,东山再起的诺基亚8能否重回霸主地位?2017-03-01 1900

-

AMD首款ARM处理器正式登场 挑战英特尔霸主地位2016-01-15 1044

-

Android市占升,苹果霸主地位危矣?2013-01-06 1487

-

华为市场全线开花 挑战爱立信霸主地位2010-01-13 599

全部0条评论

快来发表一下你的评论吧 !