FPGA中的冒险现象和如何处理毛刺

可编程逻辑

1390人已加入

描述

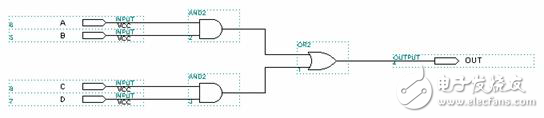

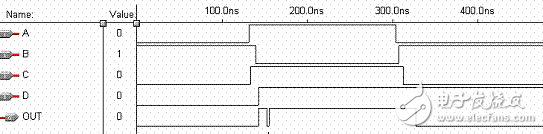

冒险往往会影响到逻辑电路的稳定性。时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。

如何处理毛刺

通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

毛刺并不是对所有的输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,我们可以说D触发器的D输入端对毛刺不敏感。根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。(由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)

去除毛刺的一种常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA中竞争与冒险的前世今生2024-02-21 793

-

FPGA | 竞争冒险和毛刺问题2023-11-02 1108

-

电感的毛刺现象是什么意思?如何解决感应毛刺?2023-08-15 6519

-

简谈FPGA的竞争冒险和毛刺问题2023-05-30 1602

-

FPGA电路中的毛刺现象2022-08-25 2415

-

什么是竞争与冒险现象?怎样判断?如何消除?2019-08-02 4071

-

FPGA视频教程之FPGA设计中如何避免冒险竞争2019-03-22 958

-

FPGA中的竞争和冒险现象2018-08-01 3264

-

FPGA设计中毛刺产生原因及消除2012-09-06 6581

-

FPGA中竞争冒险问题的研究2012-08-04 2574

-

fpga毛刺的产生及处理讨论2012-02-10 3964

-

组合逻辑中的竞争与冒险及毛刺的处理方法2011-01-24 2297

-

如何处理电冰箱压缩机不自停现象2009-05-21 1499

-

FPGA设计中竞争冒险问题的研究2009-04-21 4041

全部0条评论

快来发表一下你的评论吧 !