SN74AC7541八路开漏输出缓冲器技术解析与应用指南

描述

Texas Instruments SN74AC7541/SN74AC7541-Q1八通道缓冲器包括开漏CMOS输出。使用任一输出使能输入可同时将所有通道驱动至高阻抗状态。此系列缓冲器在5V电压和50pF负载时提供11ns的tpd 最大值,在5V电压时提供24mA的连续输出驱动。SN74AC7541-Q1缓冲器符合AEC-Q100 标准,适用于器件温度等级为1(-40°C至125°C)的汽车应用。这些SN74AC7541/SN74AC7541-Q1缓冲器用于驱动 LED指示灯并使用开漏输出进行电平转换。

数据手册:

特性

- 输入电压最高可达6V

- 电压为5V时,24mA连续输出驱动

- 电压为5V时,支持高达75mA的输出驱动(短脉冲)

- 驱动50Ω传输线路

- 电压为5V、负载为50pF时,最大t

pd为11ns - 电源电压范围:1.5V至6V

- 采用可湿性侧翼QFN封装

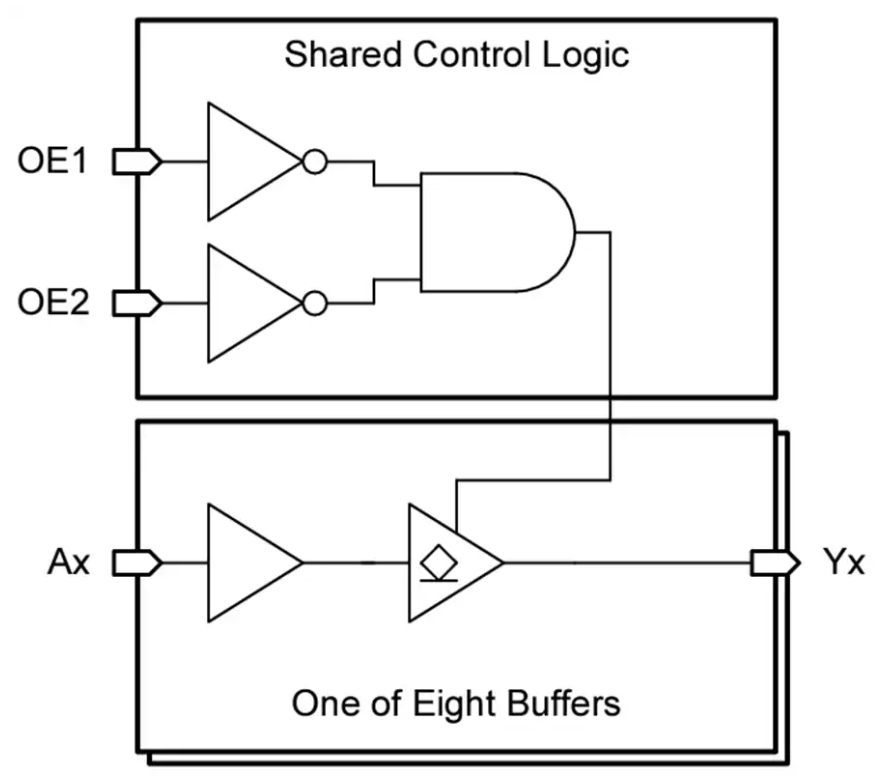

逻辑图(正逻辑)

SN74AC7541八路开漏输出缓冲器技术解析与应用指南

一、产品概述

SN74AC7541是德州仪器(TI)推出的一款高性能八路开漏输出缓冲器,采用先进的CMOS工艺制造,具有1.5V至6V的宽工作电压范围。该器件提供20引脚VSSOP(DGS)、TSSOP(PW)和VQFN(RKS)三种封装选项,工作温度范围为-40°C至125°C,专需电平转换和信号缓冲的应用场景设计。

二、核心特性

1. 电气特性

- 宽电压工作范围:1.5V至6V

- 开漏输出结构:支持线与配置

- 高驱动能力:

- 连续输出电流24mA(5V时)

- 短时脉冲可达75mA(5V时)

- 快速响应:最大传播延迟11ns(5V, 50pF负载)

- 低功耗:静态电流仅20μA(5.5V时)

2. 保护特性

- ESD保护:

- 人体放电模型(HBM):±2000V

- 器件充电模型(CDM):±1000V

- 温度保护:过热关断功能

- 输入/输出钳位二极管:防止过压损坏

三、引脚配置与功能

1. 引脚分布

- 输入引脚:A1-A8(8个独立输入通道)

- 输出引脚:Y1-Y8(8个开漏输出)

- 控制引脚:OE1/OE2(输出使能,低电平有效)

- 电源引脚:VCC(正电源),GND(地)

2. 关键引脚说明

- OE1/OE2:双使能控制设计,需同时为低电平才能激活输出

- 热焊盘(RKS封装) :可连接至GND或保持悬空,不得连接其他信号

四、工作原理

1. 功能模式

| OE1 | OE2 | 输入 | 输出状态 |

|---|---|---|---|

| L | L | L | 低电平 |

| L | L | H | 高阻态 |

| H | X | X | 高阻态 |

| X | H | X | 高阻态 |

2. 开漏输出特性

- 仅能主动拉低输出电平

- 高电平状态时呈现高阻抗

- 支持线与连接多个器件

- 需外接上拉电阻确定高电平电压

五、设计注意事项

1. 布局布线建议

- 电源去耦:每个VCC引脚附近放置0.1μF陶瓷电容

- 热管理:

- VSSOP封装θJA=123.5°C/W

- 高负载应用需考虑散热

- 信号完整性:

- 匹配传输线阻抗(驱动50Ω线路能力)

- 避免90°拐角走线

2. 未使用引脚处理

- 未用输入:必须连接到VCC或GND

- 未用输出:可保持悬空

- 建议:使用10kΩ上拉/下拉电阻处理未用输入

六、性能优化技巧

1. 降低传播延迟

- 使用较高VCC电压(5V时tpd最小)

- 减小负载电容(<50pF)

- 优化PCB走线长度

2. 提高驱动能力

- 短时脉冲可达75mA

- 多个输出并联使用

- 加强电源去耦

3. 降低功耗

- 选择适当上拉电阻值

- 优化信号边沿速率

- 不使用的通道保持禁用

七、封装信息与选型

| 封装类型 | 尺寸(mm) | 热阻θJA(°C/W) | 适用场景 |

|---|---|---|---|

| DGS(VSSOP) | 5.1×3.0 | 123.5 | 空间受限应用 |

| PW(TSSOP) | 6.5×4.4 | 126.2 | 通用设计 |

| RKS(VQFN) | 4.5×2.5 | 67.7 | 高热耗散需求 |

八、常见问题解答

Q1: 两个使能引脚(OE1/OE2)必须同时使用吗?

A: 是的,两个使能引脚都为低电平时输出才被激活,任一为高电平都会使输出进入高阻态。这种设计提供了冗余控制,防止意外使能。

Q2: 开漏输出可以直接驱动继电器吗?

A: 可以,但需注意:

- 继电器线圈需并联续流二极管

- 计算线圈电流是否在器件能力范围内

- 建议增加晶体管驱动大电流继电器

Q3: 不同通道的输出可以并联吗?

A: 可以,这种配置能:

- 增加总驱动电流能力

- 实现线与逻辑功能

- 需确保并联通道同步控制

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74AC541八路缓冲器/驱动器技术解析与应用指南2025-09-05 1007

-

SN74AC8541八路施密特触发缓冲器/驱动器技术解析2025-09-04 1940

-

Texas Instruments SN74ACT7541/SN74ACT7541-Q1八通道缓冲器数据手册2025-08-01 1336

-

Texas Instruments SN74AC07/SN74AC07-Q1六路缓冲器数据手册2025-07-15 919

-

具有三态输出的汽车类八路缓冲器和驱动器SN74LV244A-Q1数据表2024-05-23 488

-

具有三态输出的八路缓冲器/驱动器SN74AC241数据表2024-05-22 462

-

具有三态输出的八路缓冲器或驱动器SN74LVC244A数据表2024-05-13 469

-

具有三态输出的八路缓冲器和线路驱动器SN74HC244-Q1 数据表2024-05-11 513

-

具有施密特触发输入和三态输出的 八路缓冲器和线路驱动器SN74HCS244数据表2024-05-07 545

-

具有三态输出的汽车类八路缓冲器或驱动器SN74AC244-Q1数据表2024-04-30 476

-

八路施密特触发缓冲器/线路驱动器;三态-74HC_HCT7541_Q1002023-02-15 550

全部0条评论

快来发表一下你的评论吧 !