LMK3H0102EVM评估模块深度解析与技术应用指南

描述

Texas Instruments LMK3H0102EVM评估模块 (EVM) 提供一个完整的时钟平台,用于评估LMK3H0102的时钟性能、引脚配置、软件配置和功能。Texas Instruments LMK3H0102是一款集成有基于BAW(体声波)的振荡器的时钟发生器。

数据手册:*附件:Texas Instruments LMK3H0102EVM 评估模块(EVM)数据手册.pdf

特性

- 业内首款基于BAW的无基准时钟发生器

- 只能通过USB供电,可选择外接电源

- 通过TICS Pro GUI提供软件支持,用于生成配置

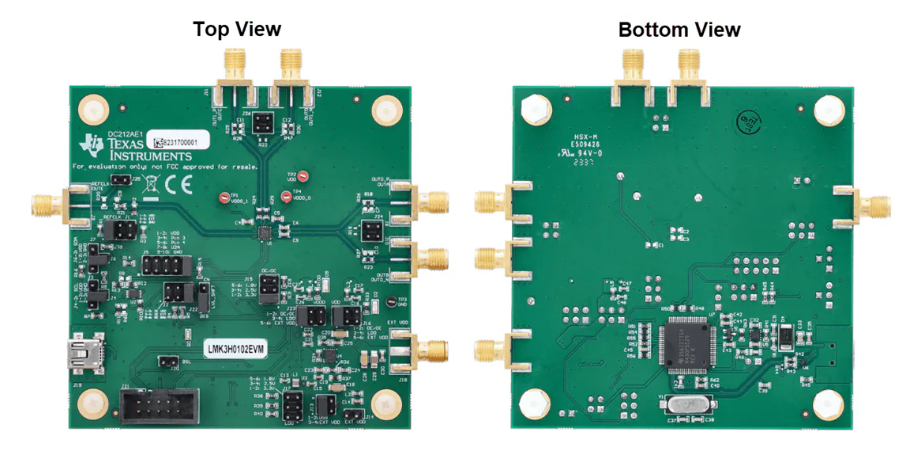

板布局

LMK3H0102EVM评估模块深度解析与技术应用指南

一、评估模块核心特性与系统架构

Texas Instruments LMK3H0102EVM是一款基于BAW(体声波)技术的参考时钟生成器评估平台,专为PCIe Gen1-Gen6时钟应用设计。该模块集成了LMK3H0102双输出时钟发生器,具有以下创新特性:

革命性技术突破:

- 集成BAW谐振器:消除对外部参考时钟的需求,提供2467MHz基础频率

- 双独立输出通道:支持100MHz默认频率(可编程范围12.5-400MHz)

- 多模式配置:支持I2C模式(默认)和OTP模式(4个预编程页面)

- 灵活供电方案:可通过USB(5V)或外部电源(1.8-3.3V)供电

模块接口配置:

- 时钟输出:4个SMA连接器(OUT0_P/N,OUT1_P/N)支持LP-HCSL/LVDS/LVCMOS

- 控制接口:板载USB-to-I2C转换器(MSP430F5529 MCU)

- 扩展接口:支持外部USB2ANY模块连接(J21)

二、硬件设计与配置详解

1. 电源管理系统

LMK3H0102EVM采用三级供电架构,支持多种配置组合:

电源域配置选项:

| 跳线 | 功能 | 配置选项 |

|---|---|---|

| J13 | DC_SRC | 选择USB 5V或EXT_DC作为板载稳压器输入 |

| J15 | DCDC_FB | 设置DC/DC输出(1.8V/2.5V/3.3V) |

| J16 | VDD_SEL | 选择VDD电源(DC/DC、LDO或外部) |

| J23 | VDDO_SEL | 选择VDDO电源(DC/DC、LDO或外部) |

典型供电方案:

- 纯USB供电:J13短接1-2,J16短接1-2,J23短接1-2

- 外部电源供电:通过J18 SMA接口输入1.8-3.3V

- 混合供电:VDD来自LDO,VDDO来自DC/DC

2. 工作模式配置

OTP模式配置(通过J1-J7跳线):

- 页面选择:J3/J7组合选择OTP页面0-3

- 输出格式:J5设置LP-HCSL终止阻抗(85Ω/100Ω)

- 典型应用:批量生产时固化配置,无需软件干预

I2C模式配置(默认):

- 地址设置:J5跳线决定I2C地址(0x68-0x6B)

- 电平转换:J22控制1.8V系统的I2C信号电平适配

- 软件控制:通过TICS Pro实时调整所有寄存器参数

3. 时钟输出配置

输出接口特性:

- OUT0:默认AC耦合LP-HCSL(C6/C9=0.1μF)

- OUT1:默认DC耦合LP-HCSL(R26/R28=49.9Ω)

- REFCLK:可配置为33Ω终端LVCMOS输出

输出格式切换:

- LP-HCSL:适合PCIe应用,摆幅可调(625-950mV)

- LVDS:支持AC/DC耦合,用于高速串行接口

- LVCMOS:最多可配置5路单端输出

三、软件控制与TICS Pro应用

1. 配置向导流程

五步配置法:

- 频率规划:设置OUT0/OUT1/REFCLK频率(12.5-400MHz)

- 格式选择:配置输出格式与终端匹配

- OE引脚:定义输出使能极性(低有效/高有效)

- OTP选项:定制四个OTP页面的差异参数

- 设计审查:生成配置报告并写入设备

关键寄存器组:

- FOD控制:FOD0_INT(0x04)、FOD0_FRAC(0x05)

- 输出配置:OUT0_CTRL(0x0C)、OUT1_CTRL(0x0D)

- SSC设置:SSC_CTRL(0x10)、SSC_STEP(0x11)

2. 实时调试功能

三大调试界面:

- FOD控制:读取BAW实际频率(典型值2467±50MHz)

- 输出管理:动态切换时钟源(FOD0/FOD1/Edge Combiner)

- 系统设置:调整状态机时钟分频(目标45MHz)

四、典型应用场景与性能优化

1. PCIe时钟树设计

Gen1-Gen6配置建议:

- Gen4/5/6:使用100MHz LP-HCSL,摆幅设为755mV

- SSC配置:选择-0.5%下行扩展(OTP Page3)

- 抖动优化:禁用未使用的输出,配置快速压摆率

2. 多板卡同步系统

级联方案:

- 主EVM配置为I2C模式,输出基准时钟

- 从设备配置OTP模式,通过REFCLK同步

- 使用TICS Pro导出寄存器配置批量编程

3. 信号完整性优化

PCB布局要点:

- 电源去耦:每个VDD引脚配置1μF陶瓷电容(C1-C3)

- 时钟走线:50Ω阻抗控制,长度匹配±50mil

- 接地策略:分割模拟/数字地,单点连接于U1下方

五、设计资源与扩展应用

1. 硬件设计文件

关键工程资源:

- 原理图:包含电源树、时钟路由和控制逻辑

- PCB文件:4层板设计(信号-地-电源-信号)

- BOM清单:注明AEC-Q200车规级元件

2. USB2ANY系统编程

量产编程方案:

- 在目标板预留10pin编程接口(SDA/SCL/GND)

- 使用USB2ANY模块连接TICS Pro

- 导入预验证的寄存器配置文件(.txt格式)

3. 定制化服务

OTP烧录流程:

- 在TICS Pro完成配置验证

- 导出Design Report发送至TI支持

- 获取预编程芯片(LMK3H0102V33-OTP)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索LMK3H0102-Q1:PCIe时钟生成的理想之选2026-02-06 262

-

LMK1D1216EVM缓冲器评估模块技术解析与应用指南2025-09-18 907

-

德州仪器LMK1D1212EVM缓冲器评估模块技术解析2025-09-17 963

-

LMK5B33414EVM网络时钟发生器评估模块技术解析2025-09-08 1056

-

LMK04368EPEVM评估模块技术解析与应用指南2025-09-07 1090

-

Texas Instruments LMK6EVM评估模块技术解析与应用指南2025-09-01 806

-

TPS7H3302EVM评估模块技术解析2025-08-27 1184

-

LMK5B33216EVM评估模块技术解析与应用指南2025-08-12 1184

-

TPS7H4001EVM-CVAL评估模块(EVM)用户指南2024-11-29 409

-

TPS7H2211EVM评估模块用户指南2024-11-05 961

-

LMK3H0102评估模块2024-11-01 350

-

LMK3H0102 PCI Express合规性报告2024-08-29 416

全部0条评论

快来发表一下你的评论吧 !