璞致 PZSDR 系列板卡之 P159 软件无线电硬件说明-ZU15EG+ADRV9009 16bit ADC & 14bit DAC

电子说

描述

第一章:产品概述

[]()1.1产品概述

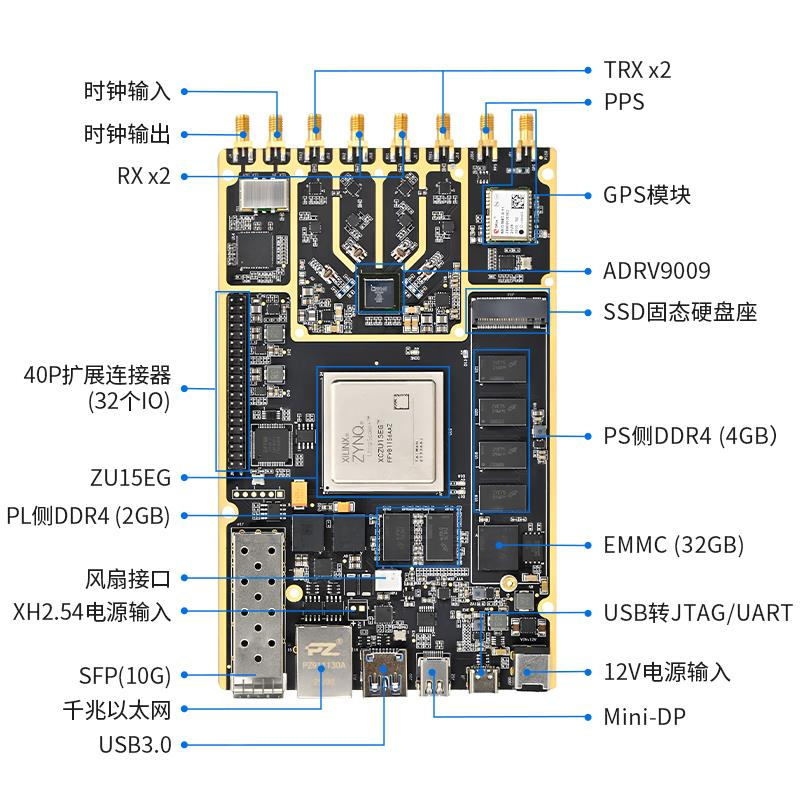

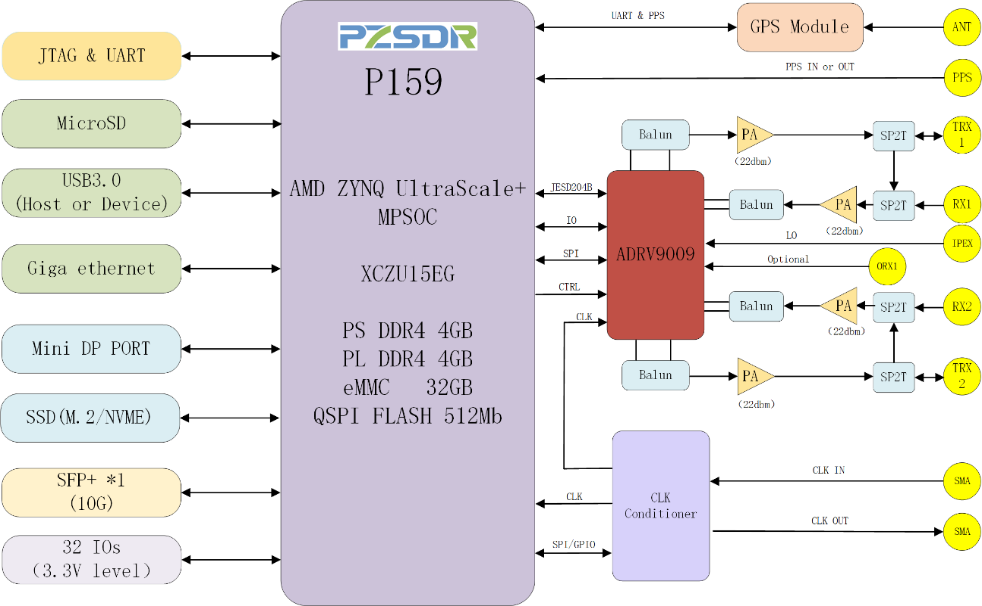

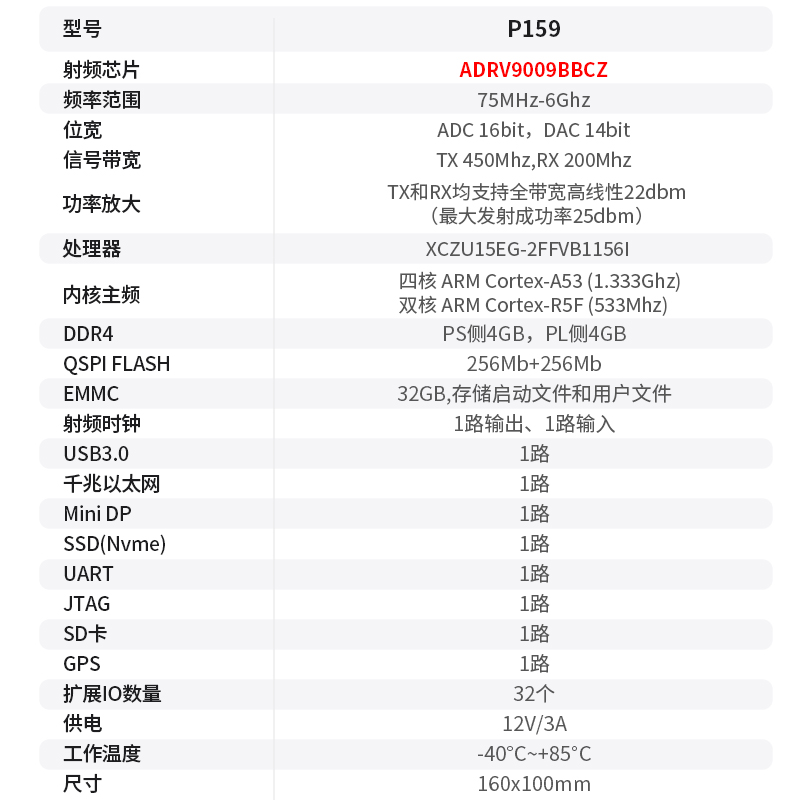

璞致软件无线电 PZSDR 系列包括了众多产品类别,本文介绍的是璞致公 司设计的 P159 产品,本产品使用了 XILINX 公司的 XCZU15EG-2FFVB1156I 作 为主控制器,搭载 ADI 公司的 ADRV9009BBCZ 射频芯片构成了产品的主体架 构。P159 集成了多路射频和其他硬件接口,资源丰富、方便易用,如下图可 以概览产品内部资源结构。

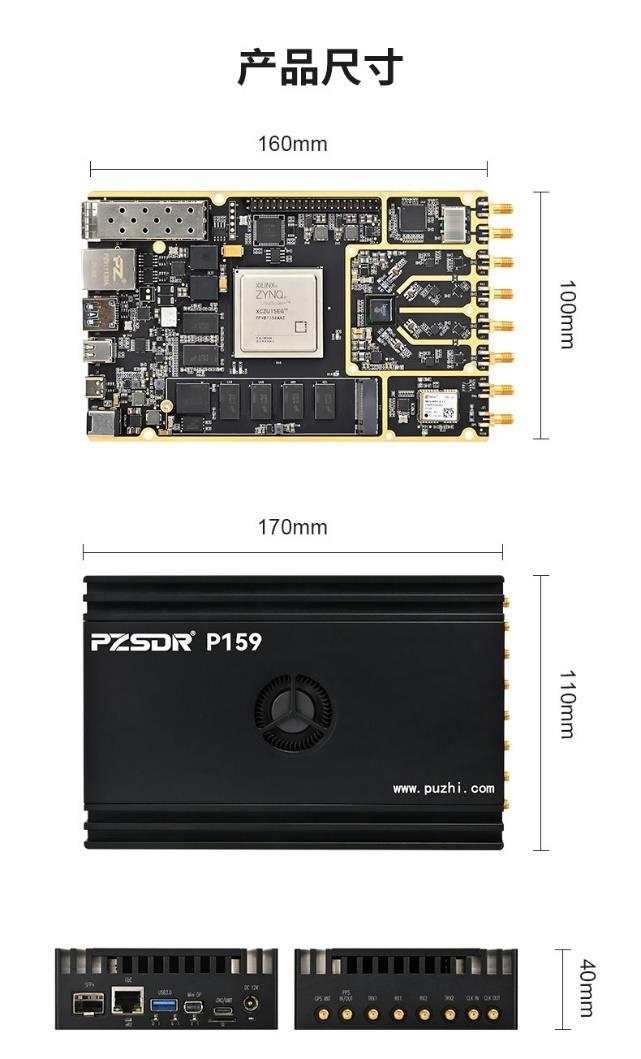

P159 的 PCB 尺寸是长宽=160100mm,PCB 上预留了多个固定孔,方便 用户直接集成到设备中。此外我们为产品配备了精美外壳,整个外壳起到 了散热的作用,确保了产品稳定运行。

产品按照工业级标准设计,工作温度-40—85℃,采用了高精度时钟, 所有接口都做了静电防护。

编辑

[]()1.2********产品资源与框图

如下框图已列出产品板载资源,通过下表可以看到开发板所包含的所 有功能。

编辑

[]()1.3********产品尺寸与外壳

如下图分别展示了产品单板尺寸和外壳尺寸,需要注意的是:对于外壳 logo,可 以为用户提供定制方案,用户提供 logo 文件即可定制成自己的专属 logo。

编辑

[]()[]()第二章:硬件使用说明

本章节开始我们将系统介绍 P159 的各个硬件功能,以便用户快速上手使用。

[]()2.1P159框架概览

如下表列出了 P159 的参数指标以及板卡设计的外部资源。板卡采用单片 ADRV9009BBCZ 设计 2T2R 射频通道以及多个高速数据传输接口,完成了整个射频 链路的收发功能。其他更详细信息可以参照我司提供的图纸。

编辑

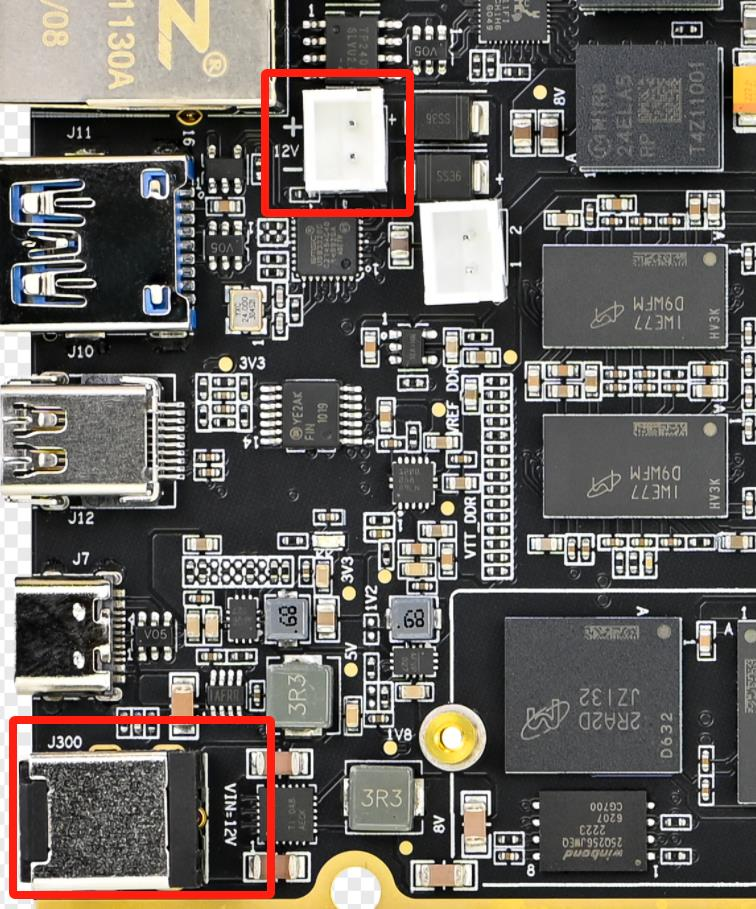

[]()2.2********关于供电

产品提供了两种供电方式:XH2.54 接口、DC-007B 接口,两种供电方式为客 户在不同使用模式下供电。

XH2.54: 如果集成单板到自己的设备中,就可以通过 XH2.54 接口供电,供 电电压电流需求是 12V/3A。

DC-007B:此接口可以外接璞致提供的 12V/3A 电源适配器为设备供电,即插 即用。DC-007B 与 XH2.54 是连通的,两者只可接一个,防止两个电源互相影响。

编辑

[]()2.3********时钟部分

P159 板卡上设计了多路时钟,分别满足不同功能,更详细信息可以参考我 司提供的图纸。

1)为 PS 侧设计了 33.33Mhz 的时钟输入,输入的管脚位置为 PS_REF_CLK, 此时钟为 ARM 侧提供时钟来源,管脚位置为 U24。

2)为 PL 端提供 200M 时钟,输入管脚位置为 IO_L13P_GC_66/IO_L13N_GC_66, 此时钟为 PL 侧提供时钟来源,管脚位置为Y4/Y3。

3)为 MGT 提供了两路时钟,分别为 125Mhz 和 156.25Mhz,时钟输入管脚对应 关系是 125Mhz 连接 MGT_REF_CLK_P0_230/ MGT_REF_CLK_N0_230,管脚位置 为 C8/C7;156.25Mhz 连接 MGT_REF_CLK_P1_230/ MGT_REF_CLK_N1_230,管 脚位置为 B10/B9;

4)为 GTR 部分提供了 26Mhz/27Mhz/100hz,分别给 USB3.0/MiniDP/SSD 三个外 设接口使用。

5)为射频电路提供了专用的时钟芯片 HMC7044LP10BE,输出多路时钟,提供 给 JESD204B 接口使用。时钟对应接口可以参考我司图纸。

[]()2.4********复位按键

P159 板卡在靠近板边位置提供了nGST 复位按键,为系统复位按键,低电平 有效。此引脚分别连接到 PS 侧的 PS_POR_B(V23)和 PL 侧的 IO_12P_44(AE15) 管脚上。

编辑

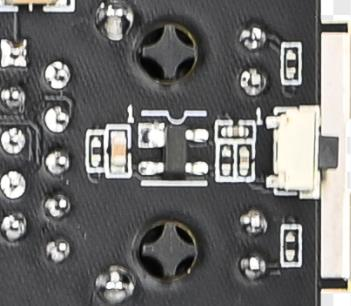

[]()2.5********主控启动模式

P159 支持四种启动模式,分别是 JTAG、QSPI Flash、EMMC、SD 卡。启动模 式的切换可以通过板边的拨动开关选择,如下图为 M2/M1/M0 三个拨码选择开关, 可以根据启动真值表来选择对应启动模式。

编辑

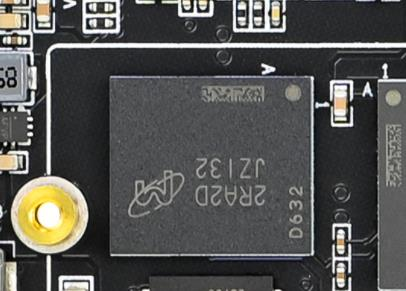

[]()2.6DDR4介绍

PS 侧设计了四颗工业级DDR4 芯片,单颗容量 1GB,四颗共计容量为 4GB,PL 侧也设计了四颗工业级 DDR4 芯片,单颗容量 1GB,四颗共计容量为4GB。型号为 MT40A512M16LY-062E IT:E。PS 侧 DDR4 管脚分配直接调用系统分配即可,PL 侧 DDR4 管脚分配可以参考下表,也可以参考我司提供的例程。

| DDR4********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DDR4_DQ0 | IO_L17N_64 | AN4 |

| DDR4_DQ1 | IO_L17P_64 | AM4 |

| DDR4_DQ2 | IO_L15P_64 | AP5 |

| DDR4_DQ3 | IO_L14N_64 | AM5 |

| DDR4_DQ4 | IO_L14P_64 | AM6 |

| DDR4_DQ5 | IO_L18N_64 | AK4 |

| DDR4_DQ6 | IO_L15N_64 | AP4 |

| DDR4_DQ7 | IO_L18P_64 | AK5 |

| DDR4_DM0 | IO_L13P_64 | AL6 |

| DDR4_DQS_P0 | IO_L16P_64 | AN6 |

| DDR4_DQS_N0 | IO_L16N_64 | AP6 |

| DDR4_DQ8 | IO_L21N_64 | AN1 |

| DDR4_DQ9 | IO_L23P_64 | AK1 |

| DDR4_DQ10 | IO_L21P_64 | AM1 |

| DDR4_DQ11 | IO_L24N_64 | AK2 |

| DDR4_DQ12 | IO_L20N_64 | AP3 |

| DDR4_DQ13 | IO_L24P_64 | AK3 |

| DDR4_DQ14 | IO_L20P_64 | AN3 |

| DDR4_DQ15 | IO_L23N_64 | AL1 |

| DDR4_DM1 | IO_L19P_64 | AN2 |

| DDR4_DQS_P1 | IO_L22P_64 | AL3 |

| DDR4_DQS_N1 | IO_L22N_64 | AL2 |

| DDR4_DQ16 | IO_L6N_64 | AK10 |

| DDR4_DQ17 | IO_L3N_64 | AM10 |

| DDR4_DQ18 | IO_L5P_64 | AN9 |

| DDR4_DQ19 | IO_L2N_64 | AM11 |

| DDR4_DQ20 | IO_L6P_64 | AJ10 |

| DDR4_DQ21 | IO_L2P_64 | AL11 |

| DDR4_DQ22 | IO_L5N_64 | AP9 |

| DDR4_DQ23 | IO_L3P_64 | AL10 |

| DDR4_DM2 | IO_L1P_64 | AJ12 |

| DDR4_DQS_P2 | IO_L4P_64 | AP11 |

| DDR4_DQS_N2 | IO_L4N_64 | AP10 |

| DDR4_DQ24 | IO_L9P_64 | AJ9 |

| DDR4_DQ25 | IO_L12P_64 | AL8 |

| DDR4_DQ26 | IO_L11P_64 | AK8 |

| DDR4_DQ27 | IO_L8P_64 | AM9 |

|---|---|---|

| DDR4_DQ28 | IO_L11N_64 | AK7 |

| DDR4_DQ29 | IO_L9N_64 | AK9 |

| DDR4_DQ30 | IO_L12N_64 | AL7 |

| DDR4_DQ31 | IO_L8N_64 | AM8 |

| DDR4_DM3 | IO_L7P_64 | AN8 |

| DDR4_DQS_P3 | IO_L10P_64 | AN7 |

| DDR4_DQS_N3 | IO_L10N_64 | AP7 |

| DDR4_DQ32 | IO_L15P_65 | AH4 |

| DDR4_DQ33 | IO_L17P_65 | AE3 |

| DDR4_DQ34 | IO_L14P_65 | AG5 |

| DDR4_DQ35 | IO_L17N_65 | AF3 |

| DDR4_DQ36 | IO_L15N_65 | AJ4 |

| DDR4_DQ37 | IO_L18N_65 | AE4 |

| DDR4_DQ38 | IO_L14N_65 | AG4 |

| DDR4_DQ39 | IO_L18P_65 | AD4 |

| DDR4_DM4 | IO_L13P_65 | AE5 |

| DDR4_DQS_P4 | IO_L16P_65 | AJ6 |

| DDR4_DQS_N4 | IO_L16N_65 | AJ5 |

| DDR4_DQ40 | IO_L11N_65 | AG6 |

| DDR4_DQ41 | IO_L12P_65 | AE7 |

| DDR4_DQ42 | IO_L12N_65 | AF7 |

| DDR4_DQ43 | IO_L9N_65 | AD6 |

| DDR4_DQ44 | IO_L8N_65 | AH8 |

| DDR4_DQ45 | IO_L9P_65 | AD7 |

| DDR4_DQ46 | IO_L8P_65 | AG8 |

| DDR4_DQ47 | IO_L11P_65 | AF6 |

| DDR4_DM5 | IO_L7P_65 | AH7 |

| DDR4_DQS_P5 | IO_L10P_65 | AE8 |

| DDR4_DQS_N5 | IO_L10N_65 | AF8 |

| DDR4_DQ48 | IO_L3N_65 | AF12 |

| DDR4_DQ49 | IO_L5P_65 | AG10 |

| DDR4_DQ50 | IO_L6P_65 | AD10 |

| DDR4_DQ51 | IO_L5N_65 | AG9 |

| DDR4_DQ52 | IO_L3P_65 | AE12 |

| DDR4_DQ53 | IO_L2P_65 | AH12 |

| DDR4_DQ54 | IO_L6N_65 | AE9 |

| DDR4_DQ55 | IO_L2N_65 | AH11 |

| DDR4_DM6 | IO_L1P_65 | AE10 |

| DDR4_DQS_P6 | IO_L4P_65 | AF11 |

| DDR4_DQS_N6 | IO_L4N_65 | AG11 |

| DDR4_DQ56 | IO_L23N_65 | AD1 |

| DDR4_DQ57 | IO_L20N_65 | AH3 |

| DDR4_DQ58 | IO_L24N_65 | AE1 |

|---|---|---|

| DDR4_DQ59 | IO_L21P_65 | AF2 |

| DDR4_DQ60 | IO_L23P_65 | AD2 |

| DDR4_DQ61 | IO_L20P_65 | AG3 |

| DDR4_DQ62 | IO_L24P_65 | AE2 |

| DDR4_DQ63 | IO_L21N_65 | AF1 |

| DDR4_DM7 | IO_L19P_65 | AH2 |

| DDR4_DQS_P7 | IO_L22P_65 | AH1 |

| DDR4_DQS_N7 | IO_L22N_65 | AJ1 |

| DDR4_A0 | IO_L15P_66 | W5 |

| DDR4_A1 | IO_L20P_66 | AB3 |

| DDR4_A2 | IO_L16N_66 | AC4 |

| DDR4_A3 | IO_L17P_66 | V4 |

| DDR4_A4 | IO_L15N_66 | W4 |

| DDR4_A5 | IO_L21N_66 | AA1 |

| DDR4_A6 | IO_L18P_66 | U5 |

| DDR4_A7 | IO_L17N_66 | V3 |

| DDR4_A8 | IO_L21P_66 | AA2 |

| DDR4_A9 | IO_L19P_66 | AC2 |

| DDR4_A10 | IO_L11N_66 | Y7 |

| DDR4_A11 | IO_L22P_66 | Y2 |

| DDR4_A12 | IO_L8P_66 | AB8 |

| DDR4_A13 | IO_L23P_66 | V2 |

| DDR4_A14 | IO_L10P_66 | AB6 |

| DDR4_A15 | IO_L10N_66 | AB5 |

| DDR4_A16 | IO_L7N_66 | AC6 |

| DDR4_A17 | IO_L20N_66 | AC3 |

| DDR4_BA0 | IO_L9N_66 | W6 |

| DDR4_BA1 | IO_L12N_66 | AA6 |

| DDR4_BG0 | IO_L16P_66 | AB4 |

| DDR4_nCS | IO_L11P_66 | Y8 |

| DDR4_ODT | IO_L8N_66 | AC8 |

| DDR4_nRESET | IO_L9P_66 | W7 |

| DDR4_CLK_P | IO_L14P_66 | Y5 |

| DDR4_CLK_N | IO_L14N_66 | AA5 |

| DDR4_CKE | IO_L6P_66 | Y10 |

| DDR4_nACT | IO_L12P_66 | AA7 |

| DDR4_nALERT | IO_L22N_66 | Y1 |

| DDR4_PARITY | IO_L19N_66 | AC1 |

[]()2.7EMMC介绍

P159 设计了 32GB 的 EMMC,用户可用于存储启动文件和用户文件。 管脚定义如下表。

| EMMC********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| EMMC_D0 | MIO13 | AK17 |

| EMMC_D1 | MIO14 | AL16 |

| EMMC_D2 | MIO15 | AN16 |

| EMMC_D3 | MIO16 | AM16 |

| EMMC_D4 | MIO17 | AP16 |

| EMMC_D5 | MIO18 | AE18 |

| EMMC_D6 | MIO19 | AL17 |

| EMMC_D7 | MIO20 | AD18 |

| EMMC_CLK | MIO22 | AD20 |

| EMMC_CMD | MIO21 | AF18 |

| EMMC_nRST | MIO23 | AD19 |

编辑

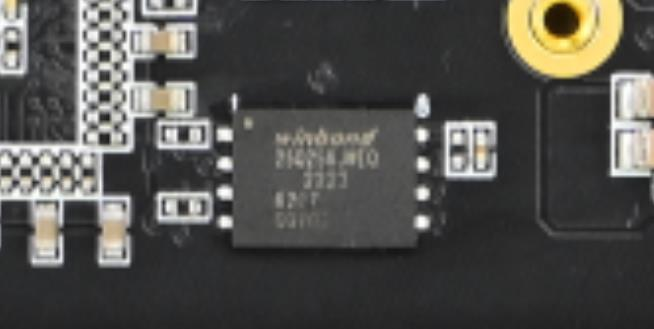

[]()2.8QSPIFLASH********介绍

P159 设计了两路 256Mb 的 QSPI FLASH,合计 512Mb,组成 x8 模式。可用于 存储启动文件和用户文件。管脚定义如下表。

| QSPI0********FLASH | 管脚名称 | 管脚位置 |

|---|---|---|

| QSPI0_DQ0 | MIO2 | AH16 |

| QSPI0_DQ1 | MIO3 | AJ16 |

| QSPI0_DQ2 | MIO4 | AD16 |

| QSPI0_DQ3 | MIO5 | AG16 |

| QSPI0_CS | MIO1 | AM15 |

| QSPI0_CLK | MIO6 | AF16 |

| QSPI1********FLASH | 管脚名称 | 管脚位置 |

|---|---|---|

| QSPI1_DQ0 | MIO2 | AE17 |

| QSPI1_DQ1 | MIO3 | AP15 |

| QSPI1_DQ2 | MIO4 | AH17 |

|---|---|---|

| QSPI1_DQ3 | MIO5 | AF17 |

| QSPI1_CS | MIO1 | AD17 |

| QSPI1_CLK | MIO6 | AJ17 |

编辑

编辑

[]()2.9E2PROM介绍

单板上预留了一颗 E2PROM,容量为 256Kb,管脚定义如下表。

| E2PROM********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| E2PROM_I2C_SCL | IO_L8N_HDGC_50 | G13 |

| E2PROM_I2C_SDA | IO_L9N_50 | G14 |

编辑

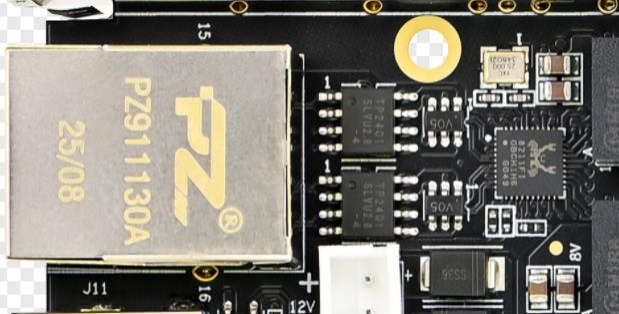

[]()2.10********千兆以太网

单板 PS 侧设计了一颗千兆以太网芯片,以太网芯片与 ZYNQ 芯片之间通过 RGMII 接口互联,连接对应管脚见下表芯片地址 PHY_AD[2:0]=001。

| RMGII 信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| GPHY_GTX_CLK | MIO26_501 | P21 |

| GPHY_TXD0 | MIO27_501 | M21 |

| GPHY_TXD1 | MIO28_501 | N21 |

| GPHY_TXD2 | MIO29_501 | K22 |

| GPHY_TXD3 | MIO30_501 | L21 |

| GPHY_TX_EN | MIO31_501 | J22 |

| GPHY_RX_CLK | MIO32_501 | H22 |

| GPHY_RXD0 | MIO33_501 | H23 |

| GPHY_RXD1 | MIO34_501 | L22 |

|---|---|---|

| GPHY_RXD2 | MIO35_501 | P22 |

| GPHY_RXD3 | MIO36_501 | K23 |

| GPHY_RX_DV | MIO37_501 | N22 |

| GPHY_MDC | MIO76_502 | H25 |

| GPHY_MDIO | MIO77_502 | F25 |

编辑

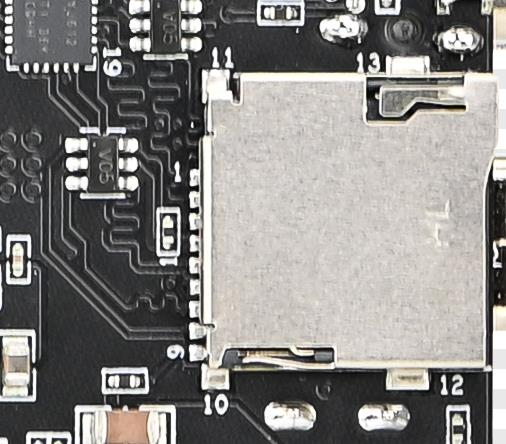

[]()2.11SD卡

单板上设计了 SD 卡座,与PS 侧 BANK501 相连,因为 BANK501 的电平为 1.8V,但 SD 的数据电平为 3.3V,所以使用 TXS02612RTWR 进行电平转换。

如下是 SD 卡的管脚分配,更详细电路可参考原理图。

| SD********卡 | 管脚名称 | 管脚位置 |

|---|---|---|

| SD_CLK | MIO51 | N25 |

| SD_CMD | MIO50 | P25 |

| SD_DATA0 | MIO46 | J25 |

| SD_DATA1 | MIO47 | L25 |

| SD_DATA2 | MIO48 | M25 |

| SD_DATA3 | MIO49 | K25 |

编辑

[]()2.12USB转JTAG和********UART

P159 上设计了一路 USB 转 JTAG/UART 接口,JTAG 连接到主控芯片的 JTAG 接口上, UART 连接到主控的 UART0 管脚上。

如下是 UART0 管脚分配,更详细电路可参考原理图。

| UART0 | 管脚名称 | 管脚位置 |

|---|---|---|

| UART0_TX | MIO43 | K24 |

| UART0_RX | MIO42 | M24 |

编辑

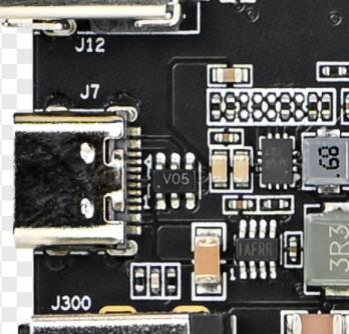

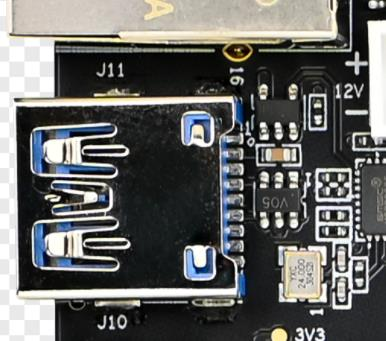

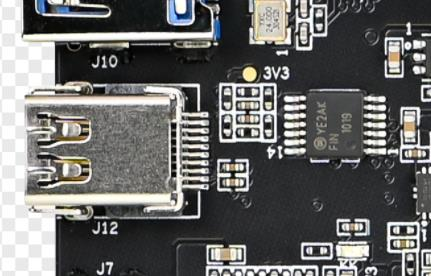

[]()2.13USB3.0接口

P159 上设计了一路 USB3.0 接口,接口类型为 Type-A,可以灵活的定义成 Host 模式或者 Device 模式,如下表列出了 USB PHY 与主芯片的对应关系。详细 信息参见底板原理图。

| USB 信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| USBPHY_DATA0 | MIO56 | C23 |

| USBPHY_DATA1 | MIO57 | A23 |

| USBPHY_DATA2 | MIO54 | F23 |

| USBPHY_DATA3 | MIO59 | B24 |

| USBPHY_DATA4 | MIO60 | E24 |

| USBPHY_DATA5 | MIO61 | C24 |

| USBPHY_DATA6 | MIO62 | G24 |

| USBPHY_DATA7 | MIO63 | D24 |

| USBPHY_STP | MIO58 | G23 |

| USBPHY_NXT | MIO55 | B23 |

| USBPHY_DIR | MIO53 | E23 |

| USBPHY_CLKOUT | MIO52 | F22 |

| USBPHY_nRSET | MIO64 | A25 |

| GT2_USB3_SSTXP | PS_MGTRTXP2_505 | W31 |

| GT2_USB3_SSTXN | PS_MGTRTXN2_505 | W32 |

| GT2_USB3_SSRXP | PS_MGTRRXP2_505 | Y33 |

| GT2_USB3_SSRXN | PS_MGTRRXN2_505 | Y34 |

| CLK_FPGA_26M_P | MGT_505_TX_P2 | U27 |

| CLK_FPGA_26M_N | MGT_505_TX_N2 | U28 |

编辑

[]()2.14MiniDP********接口

P159 上设计了一个Mini DP 输出接口,接口信号与 FPGA 的 BANK50/BANK505 相连,详细可参考原理图。

如下是 Mini DP 的引脚分配, 详细电路可以参考开发板原理图。

| MiniDP引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| GT3_DP_LINE_P0 | MGT_505_TX_P3 | V29 |

| GT3_DP_LINE_N0 | MGT_505_TX_N3 | V30 |

| DP_HPD | IO_L7P_HDGC_50 | J12 |

| DP_AUX_OUT | IO_L12N_50 | J15 |

| DP_OE | IO_L10P_50 | J14 |

| DP_AUX_IN | IO_L12P_50 | J16 |

| DP_CLK_P_27M | MGT_505_CLK_P2 | U31 |

| DP_CLK_N_27M | MGT_505_CLK_N2 | U32 |

编辑

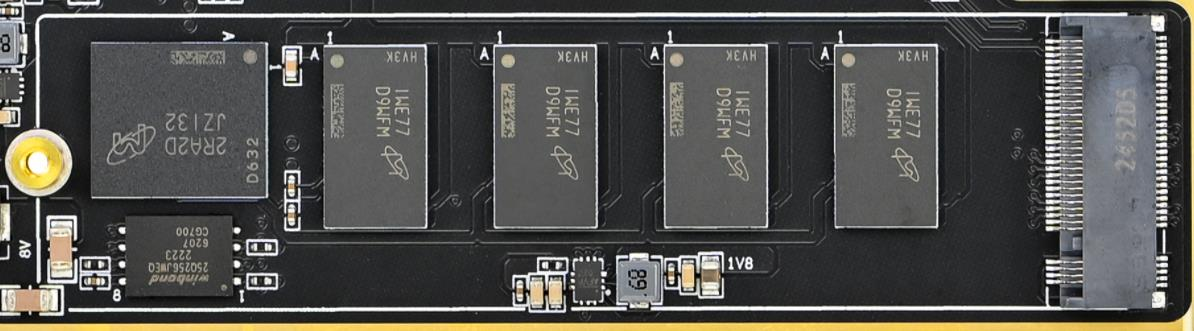

[]()2.15SSD接口

P159 的 PS 侧设计了一路 SSD(x2 模式),接口类型为 M.2,走 NVME 协议。 SSD 接口的管脚位置如下表,详细电路可以参考开发板原理图。

| SSD 接口 | 管脚名称 | 管脚位置 |

|---|---|---|

| SSD_nRST | MIO70 | C26 |

| CLK_FPGA_100M_P | MGT_505_CLK_P0 | AA27 |

| CLK_FPGA_100M_N | MGT_505_CLK_N0 | AA28 |

| GT0_SSD_TX_P0 | MGT_505_TX_P0 | AB29 |

16 / 22

| GT0_SSD_TX_N0 | MGT_505_TX_N0 | AB30 |

|---|---|---|

| GT0_SSD_RX_P0 | MGT_505_RX_P0 | AB33 |

| GT0_SSD_RX_N0 | MGT_505_RX_N0 | AB34 |

| GT0_SSD_TX_P1 | MGT_505_TX_P1 | Y29 |

| GT0_SSD_TX_N1 | MGT_505_TX_N1 | Y30 |

| GT0_SSD_RX_P1 | MGT_505_RX_P1 | AA31 |

| GT0_SSD_RX_N1 | MGT_505_RX_N1 | AA32 |

编辑

[]()2.16SFP接口

P159 上设计了一路 10G SFP 接口,接口信号与 MPSOC 的 BANK230 相连,详 细可参考原理图。

如下是 SFP 的引脚分配, 详细电路可以参考开发板原理图。

| QSFP1********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| SFP1-TX-P | MGT_TX_P2_230 | B6 |

| SFP1-TX-N | MGT_TX_N2_230 | B5 |

| SFP1-RX-P | MGT_TX_P2_230 | B2 |

| SFP1-RX-N | MGT_TX_N2_230 | B1 |

编辑

[]()2.1740P扩展接口

P159 预留了一个40P 2.54mm 间距的连接器,用于扩展信号的连接,

信号与 FPGA 的 BANK49/50 连接,电平为 3.3V。如下表标出了信号所在的芯 片位置,详细连接关系参考原理图部分。

| JM1 信号顺序 | 管脚名称 | 管脚位置 | JM1 信号顺序 | 管脚名称 | 管脚位置 |

|---|---|---|---|---|---|

| 5 | IO_L3P_49 | B16 | 6 | IO_L1P_49 | F16 |

| 7 | IO_L3N_49 | A16 | 8 | IO_L1N_49 | F15 |

| 9 | IO_L4P_49 | B15 | 10 | IO_L2P_49 | D16 |

| 11 | IO_L4N_49 | A15 | 12 | IO_L2N_49 | C16 |

| 13 | IO_L7P_49 | C14 | 14 | IO_L5P_49 | E15 |

| 15 | IO_L7N_49 | B14 | 16 | IO_L5N_49 | D15 |

| 17 | IO_L8P_49 | C13 | 18 | IO_L6P_49 | E14 |

|---|---|---|---|---|---|

| 19 | IO_L8N_49 | B13 | 20 | IO_L6N_49 | D14 |

| 21 | IO_L10P_49 | C12 | 22 | IO_L12P_49 | F13 |

| 23 | IO_L10N_49 | B12 | 24 | IO_L12N_49 | E13 |

| 25 | IO_L1P_50 | J11 | 26 | IO_L9P_49 | A13 |

| 27 | IO_L1N_50 | J10 | 28 | IO_L9N_49 | A12 |

| 29 | IO_L3P_50 | F10 | 30 | IO_L11P_49 | E12 |

| 31 | IO_L3N_50 | E10 | 32 | IO_L11N_49 | D12 |

| 37 | IO_L2P_50 | H10 | 38 | IO_L4P_50 | D11 |

| 39 | IO_L2N_50 | G10 | 40 | IO_L4N_50 | D10 |

编辑

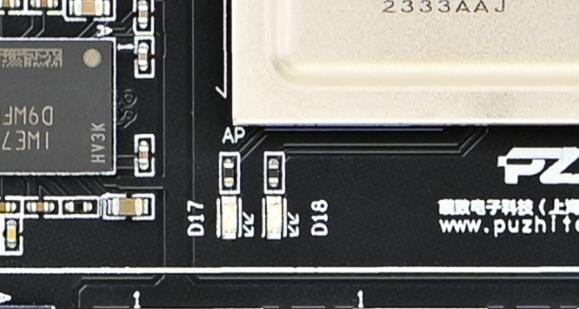

[]()2.18LED指示灯

P159 上设计了两路 LED,高电平亮,低电平灭。详细电路可参考开发板原理 图。

| LED 位号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1(D17) | IO_L3N_44 | AP12 |

| LED2(D18) | IO_L1N_44 | AP14 |

编辑

[]()

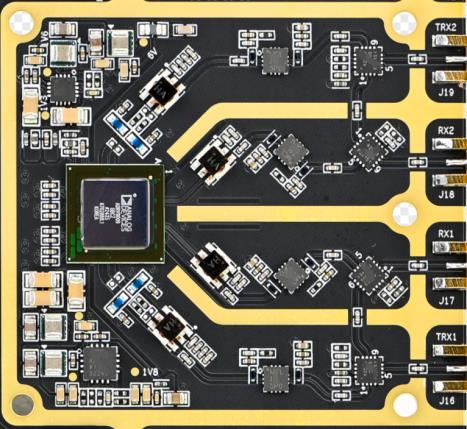

2.19ADRV9009介绍

P159 射频部分使用了 ADI 公司的 ADRV9009,本小节我们将从射频链路、数 据通道、时钟部分详细介绍。

编辑

[]()2.19.1********射频前端电路

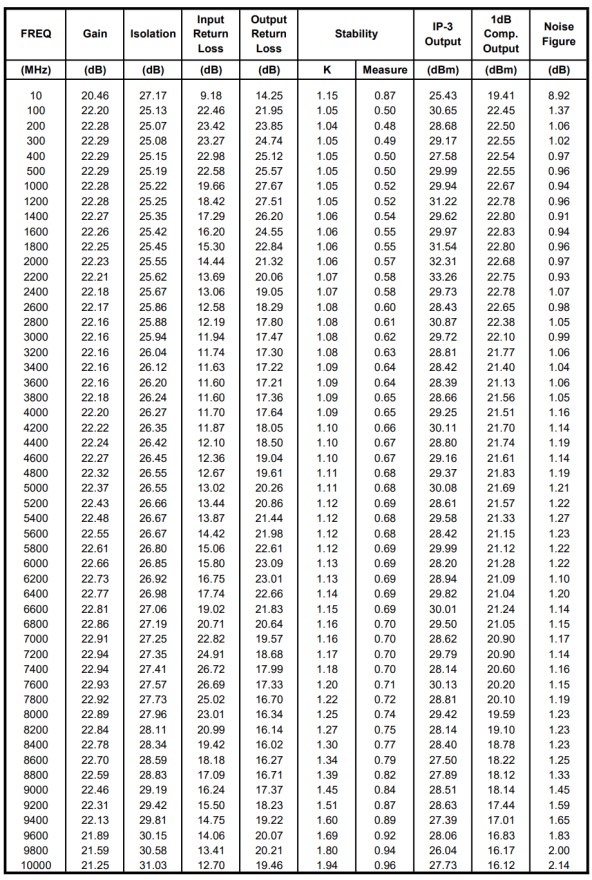

射频前端电路涉及到巴伦、功放、以及射频开关三部分。巴伦的带宽为 10M- 8Ghz,覆盖了 ADRV9009 的通信带宽。

功放带宽是 10M-10Ghz,也是覆盖了 ADRV9009 的通信带宽,整个通信带宽 内功放的增益线性非常好,如下表可以详细看到功放在各频点指标。

编辑

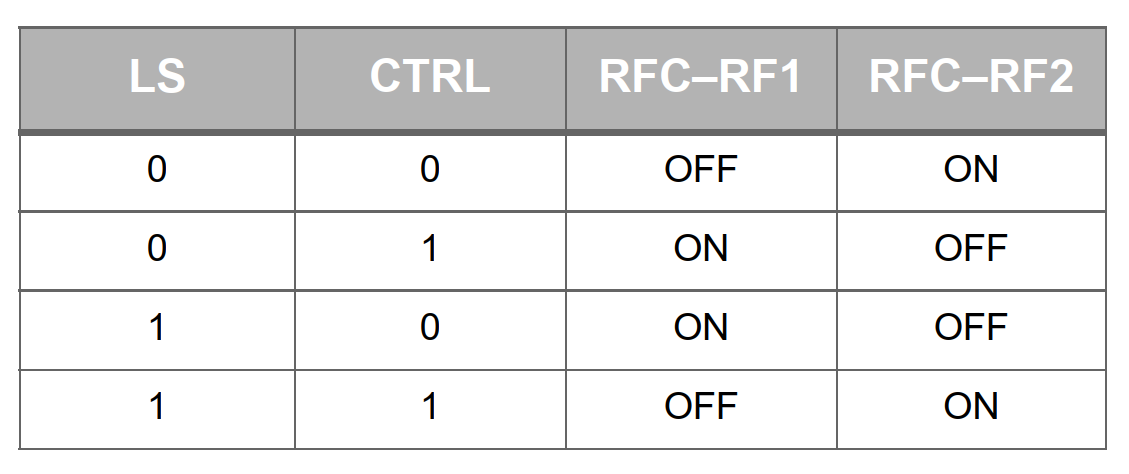

射频开关采用的是 SPDT 一进两出,带宽为 9K-8G,并且射频开关内部集成 了静电防护电路,有效防护了射频端口。对应射频开关的切换逻辑可以参考下表, 对于 ADRV9009 的 TX/RX 切换,可以参考原理图实际连接关系来对应调整。

编辑

[]()2.19.2ADRV9009通信端口

ADRV9009 数字端口分为数据端口和控制端口两部分,数据端口如下表列出 了管脚对应关系,也可以参考 P159 原理图和对应的工程代码。

| ADRV9009 接口 | 管脚名称 | 管脚位置 |

|---|---|---|

| ADRV9009_SERDIN_P0 | MGT_TX_P0_128 | T29 |

| ADRV9009_SERDIN_N0 | MGT_TX_N0_128 | T30 |

| ADRV9009_SERDIN_P1 | MGT_TX_P2_128 | P29 |

| ADRV9009_SERDIN_N1 | MGT_TX_N2_128 | P30 |

| ADRV9009_SERDIN_P2 | MGT_TX_P1_128 | R31 |

| ADRV9009_SERDIN_N2 | MGT_TX_N1_128 | R32 |

| ADRV9009_SERDIN_P3 | MGT_TX_P3_128 | M29 |

| ADRV9009_SERDIN_N3 | MGT_TX_N3_128 | M30 |

| ADRV9009_SYNCIN_P0 | IO_L4P_67 | T12 |

| ADRV9009_SYNCIN_N0 | IO_L4N_67 | R12 |

| ADRV9009_SYNCIN_P1 | IO_L3P_67 | U10 |

| ADRV9009_SYNCIN_N1 | IO_L3N_67 | T10 |

| ADRV9009_SERDOUT_P0 | MGT_RX_P0_128 | T33 |

| ADRV9009_SERDOUT_N0 | MGT_RX_N0_128 | T34 |

| ADRV9009_SERDOUT_P1 | MGT_RX_P2_128 | N31 |

| ADRV9009_SERDOUT_N1 | MGT_RX_N2_128 | N32 |

| ADRV9009_SERDOUT_P2 | MGT_RX_P1_128 | P33 |

| ADRV9009_SERDOUT_N2 | MGT_RX_N1_128 | P34 |

| ADRV9009_SERDOUT_P3 | MGT_RX_P3_128 | M33 |

| ADRV9009_SERDOUT_N3 | MGT_RX_N3_128 | M34 |

| ADRV9009_SYNCOUT_P0 | IO_L2P_67 | T13 |

| ADRV9009_SYNCOUT_N0 | IO_L2N_67 | R13 |

| ADRV9009_SYNCOUT_P1 | IO_L1P_67 | W12 |

| ADRV9009_SYNCOUT_N1 | IO_L1N_67 | W11 |

| ADRV9009_SYSREFCLK_IN_P | Come from CLK IC HMC7044LP10BE | |

| ADRV9009_SYSREFCLK_IN_N | Come from CLK IC HMC7044LP10BE | |

| ADRV9009_DEVCLK_IN_P | Come from CLK IC HMC7044LP10BE | |

| ADRV9009_DEVCLK_IN_N | Come from CLK IC HMC7044LP10BE | |

| ADRV9009_TX_ENABLE1 | IO_L6N_47 | F20 |

| ADRV9009_TX_ENABLE2 | IO_L4P_47 | J19 |

| ADRV9009_RX_ENABLE1 | IO_L6P_47 | G20 |

| ADRV9009_RX_ENABLE2 | IO_L4N_47 | J20 |

| ADRV9009_SPI_CLK | IO_L6P_48 | F17 |

| ADRV9009_SPI_CS | IO_L6N_48 | F18 |

| ADRV9009_SPI_DI | IO_L8N_48 | E18 |

| ADRV9009_SPI_DO | IO_L12P_48 | A17 |

| ADRV9009_nRST | IO_L10P_48 | B18 |

| ADRV9009_GP_INT | IO_L7P_47 | E22 |

| ADVR9009_GPIO_0 | IO_L7P_48 | E19 |

| ADVR9009_GPIO_1 | IO_L7N_48 | D19 |

| ADVR9009_GPIO_2 | IO_L9N_48 | C17 |

| ADVR9009_GPIO_3 | IO_L9P_48 | D17 |

| ADVR9009_GPIO_4 | IO_L11N_48 | C19 |

|---|---|---|

| ADVR9009_GPIO_5 | IO_L10N_48 | B19 |

| ADVR9009_GPIO_6 | IO_L11P_48 | C18 |

| ADVR9009_GPIO_7 | IO_L8P_48 | E17 |

| ADVR9009_GPIO_8 | IO_L2N_48 | H17 |

| ADVR9009_GPIO_9 | IO_L2P_48 | J17 |

| ADVR9009_GPIO_10 | IO_L4N_48 | K17 |

| ADVR9009_GPIO_11 | IO_L4P_48 | L17 |

| ADVR9009_GPIO_12 | IO_L3P_48 | L18 |

| ADVR9009_GPIO_13 | IO_L3N_48 | K18 |

| ADVR9009_GPIO_14 | IO_L5P_48 | G18 |

| ADVR9009_GPIO_15 | IO_L1N_48 | H19 |

| ADVR9009_GPIO_16 | IO_L1P_48 | H18 |

| ADVR9009_GPIO_17 | IO_L5N_48 | G19 |

| ADVR9009_GPIO_18 | IO_L12N_48 | A18 |

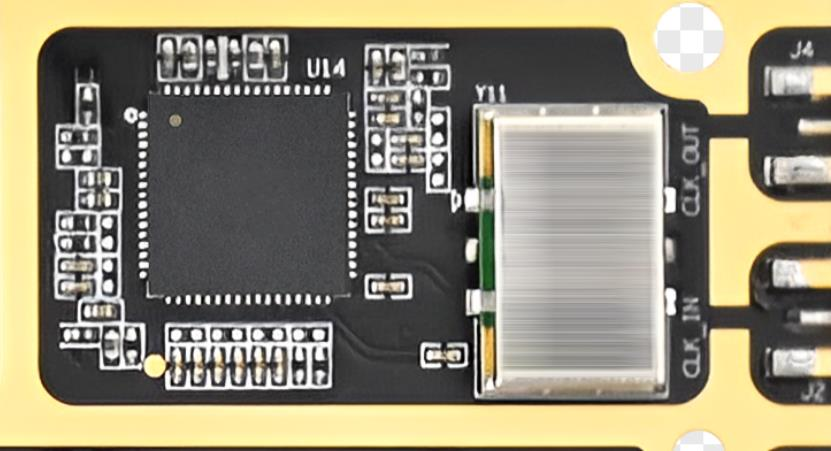

[]()2.19.3ADRV9009时钟电路

ADRV9009 的输入时钟采用了高精度 VCXO 时钟,频率在 122.88Mhz,通过专 用的时钟芯片产生所需的多路时钟,同时 P159 预留了时钟输入输出接口,如用 户需要更高精度时钟,可以从外部灌入时钟,可以输出所需时钟。对于时钟的详 细使用可以参考璞致提供的原理图以及提供的代码工程来编程。

编辑

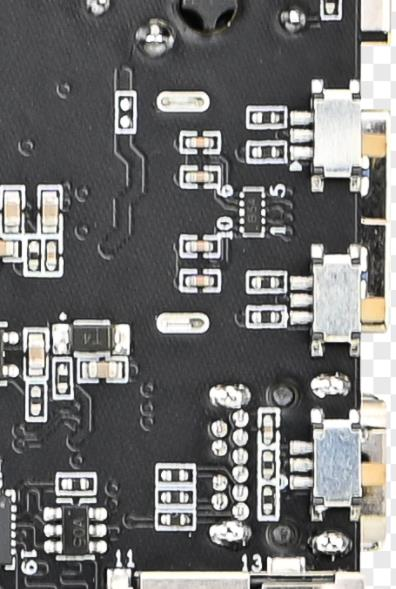

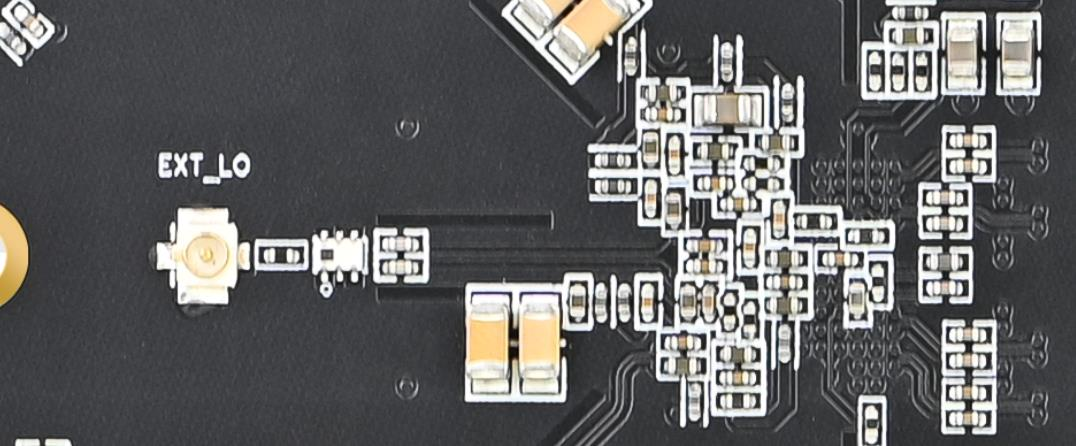

[]()2.19.4ADRV9009外本振输入

P159 上预留了外本振输入,接口类型为一代 IPEX 接口,如下图参考,也可 以参考璞致提供的原理图

编辑

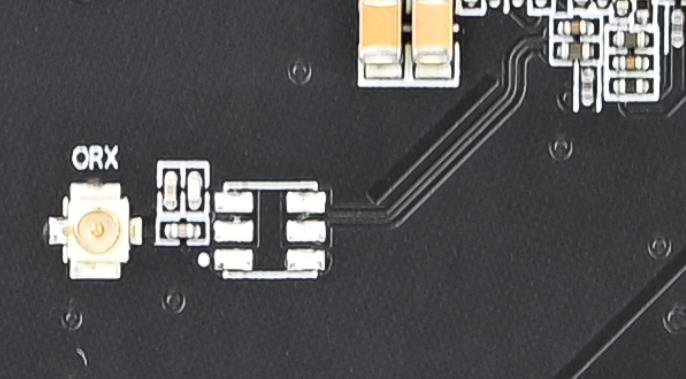

[]()2.19.5ADRV9009ORX1********输入

P159 上预留了ORX1 输入,接口类型为一代 IPEX 接口,默认情况下输出 BALUN 没有焊接,如用户需要使用此电路,需要提前告知。如下图参考,也可以参考璞 致提供的原理图

编辑

[]()PPS********接口

P159 上设计了一路 PPS,PPS 信号可以通过方向脚配置成 PPS 输入,也可 以通过方向脚配置成 PPS 输出,默认为 PPS 输入,用户可以根据实际需要来选 择。PPS 和方向脚分别连到 FPGA 的如下管脚:

| 信号名 | 管脚名称 | 管脚位置 |

|---|---|---|

| PPS_IN_OUT | IO_11N_44 | AG15 |

| PPS_DIR | IO_7P_44 | AH14 |

编辑

[]()2.21GPS模块

底板上集成一颗 GPS 模块,可以实现 GPS 和北斗定位功能。我们可以通过 UART 来配置和读取 GPS 模块数据,另外模块提供了PPS 信号。如下表列出了 GPS 模块的管脚对应关系,更详细说明可以参考提供的原理图。

| GPS 模块 | 管脚名称 | 管脚位置 |

|---|---|---|

| GPS_UART_TXD | IO_6P_44 | AK13 |

| GPS_UART_RXD | IO_2N_44 | AN13 |

| GPS_nRESET | IO_6P_44 | AM13 |

| GPS_PPS | IO_6P_44 | AH13 |

编辑

审核编辑 黄宇

-

PZSDR 软件无线电 开发板系列板卡之P201Pro P203Pro 硬件说明—AD9361 AD93632025-08-27 1803

-

PZSDR璞致软件无线电P159(ZU15EG+ADRV9009)为通信系统设计赋能hongying188 2025-08-06

-

璞致电子软件无线电(PZSDR)系列——从嵌入式到高端射频的全场景解决方案2025-07-22 1821

-

AD9088: 阿波罗MxFE Octal, 16Bit, 16PSS RF DAC和Octal, 12Bit, 8 PSS RF ADC初步数据表 ADI2023-10-09 234

-

FMC子卡设计资料:FMC144 -八路 250MSPS 14bit AD FMC子卡2021-12-09 802

-

基于Xilinx XC7Z100+ADRV9009的双收双发无线电射频板卡2021-09-02 4752

-

9009开发板学习资料第428篇:基于XC7Z100+ADRV9009的双收双发无线电射频板卡 ADRV9009板卡 XC7Z100板卡 XC7Z100+ADRV90092021-07-09 5672

-

ADRV9009-ZU11EG RF-SOM-设计文件2021-03-23 2308

-

基于XC7Z100+ADRV9009的双收双发无线电射频板卡2020-12-21 1153

-

ADC3444IRTQT详细参数IC ADC 14BIT PIPELINED 56QFN2020-09-04 841

-

请问如何正确测量AD7988-5 16bit ADC DC&AC performance?2018-10-09 1817

-

dm368 14bit sensor 输入问题,请问14bit数据输入需要修改哪些寄存器?2018-05-31 3013

-

14bit ADC单片机2013-04-11 5058

全部0条评论

快来发表一下你的评论吧 !