德州仪器LMX1214射频缓冲器与分频器技术解析

描述

Texas Instruments LMX1214射频缓冲器和分频器具有高输出频率、超低噪声基底和极低偏斜时钟分布。该设备有四个高频输出时钟和一个低频辅助时钟输出。Texas Instruments LMX1214支持高频时钟的缓冲和分频模式。此设备可将多通道、低偏斜、超低噪声本地振荡器信号分配给多个混频器。

数据手册:*附件:Texas Instruments LMX1214射频缓冲器和分频器数据手册.pdf

特性

- 300MHz至16GHz频率的时钟缓冲器

- 支持的分频器输出频率最高可达6.4GHz

- 超低噪声

- 噪声本底:-161dBc/Hz(6GHz输出时)

- 附加抖动:36fs(100Hz至f

CLK)(6GHz输出时) - 附加抖动:5fs(100Hz至100MHz)

- 四个高频时钟输出

- 通过1(旁路)、2、3、4、5、6、7和8共享分频器

- 典型输出到输出偏斜:1ps

- 支持输出启用和分频器/2、/3和/4值设置的引脚模式选项

- AUXCLK输出

- 独立的分隔存储体

- 1、2、4预分频器

- 1(旁路)、2、......、1023后分频器

- 八个可编程输出功率级别

- 所有分频器的SYNC功能

- 工作电压:2.5V

- -40 °C 到 +85 °C 工作温度

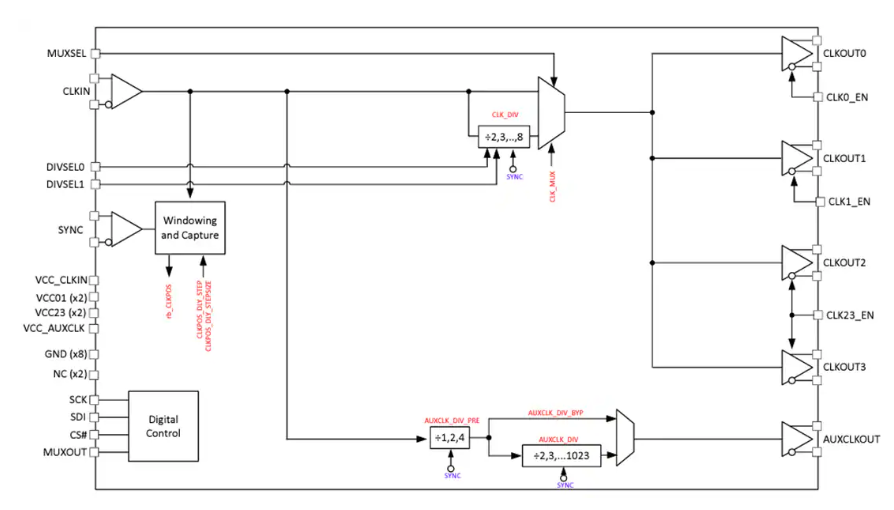

功能框图

德州仪器LMX1214射频缓冲器与分频器技术解析

一、产品概述

LMX1214是德州仪器(TI)推出的一款低噪声高频缓冲器与分频器,专为300MHz至18GHz高频时钟信号处理设计。该器件具有以下核心特性:

- 支持高达18GHz的输入频率和8GHz的分频输出频率

- 超低噪声基底:-161dBc/Hz @6GHz输出

- 极低附加抖动:36fs (100Hz-fCLK)和5fs (100Hz-100MHz)

- 提供4路高频时钟输出和1路辅助时钟输出

- 支持1/2/3/4/5/6/7/8分频比

- 2.5V单电源工作电压

二、关键技术创新

1. 超低噪声架构

LMX1214采用优化的R-2R梯形电阻网络与轨到轨输出缓冲放大器组合架构,实现了:

- 噪声基底低至-161dBc/Hz @6GHz

- 典型附加抖动仅5fs RMS (100Hz-100MHz)

- 二次谐波抑制达-25dBc @6GHz差分输出

2. 灵活的时钟分配

- 主时钟通道:4路共享分频器(÷1至÷8)

- 辅助时钟通道:独立分频链(预分频÷1/2/4 + 主分频÷2-1023)

- 输出功率8级可调(通过CLKOUTx_PWR寄存器)

3. 同步功能

集成SYNC引脚支持:

- 多器件相位同步

- 窗口捕获功能(精度达8ps/step)

- 支持AC/DC耦合输入(1.1V-1.5V可编程共模电压)

三、寄存器配置指南

关键寄存器组

- 时钟控制寄存器(R25) :

- CLK_MUX[2:0]:0x1=缓冲模式,0x2=分频模式

- CLK_DIV[5:3]:分频值设置(0x1=÷2,0x7=÷8)

- 输出配置寄存器(R3-R5) :

- CLKOUTx_EN:输出使能位

- CLKOUTx_PWR:输出功率等级(0-7)

- SYNC时序寄存器(R13-R15) :

- SYNC_DLY_STEP:延迟步长选择

- SYNC_DLY[6:1]:精细延迟调整

典型配置流程

- 上电后执行软复位(R25.CLK_DIV_RST=1→0)

- 设置主时钟模式(R25.CLK_MUX=0x2)

- 配置分频比(R25.CLK_DIV=0x3 for ÷4)

- 使能所需输出(R3=0xF0FE使能所有输出)

- 设置SYNC参数(R13.SYNC_DLY_STEP=0x3)

四、PCB设计要点

1. 电源处理

- 每路VCC引脚就近放置:

- 0.1μF RF电容(0402封装)

- 1μF+10μF大容量电容(间距>5mm)

- 电源隔离:时钟与辅助通道间加10Ω磁珠

2. 信号布线

- 差分对长度匹配:±50μm

- 输入时钟走线:

- 优先使用Rogers 4350B板材

- 最大长度<5mm(@18GHz)

- 热焊盘设计:

- 6×6mm 2oz铜面积

- 至少9个0.3mm过孔

五、性能实测数据

相位噪声对比(@6GHz)

| 条件 | 1kHz偏移 | 100kHz偏移 | 1MHz偏移 |

|---|---|---|---|

| 输入源单独 | -85dBc | -110dBc | -140dBc |

| 通过LMX1214缓冲 | -84dBc | -109dBc | -139dBc |

| 附加噪声贡献 | +1dB | +1dB | +1dB |

温度稳定性

- 输出功率变化:±0.5dB(-40°C至+85°C)

- 延迟温漂:0.06ps/°C(缓冲模式)

六、选型建议

| 需求场景 | 推荐配置 | 备注 |

|---|---|---|

| 毫米波雷达LO分配 | 缓冲模式+全输出启用 | 需外置散热片 |

| 高速ADC时钟链 | 分频模式+SYNC同步 | 建议÷4保持50%占空比 |

| 多设备测试系统 | 主设备缓冲+从设备分频 | 需共享SYNC信号 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

德州仪器LMK1C110x时钟缓冲器的特性与设计应用2026-02-08 251

-

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析2026-02-06 216

-

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析2026-01-26 387

-

LMX1205-EP:低噪声、高频JESD缓冲器/乘法器/分频器的深度解析2026-01-25 592

-

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要2025-09-16 910

-

LMX1214 低噪声高频缓冲器与分频器技术文档总结2025-09-11 893

-

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析2025-09-10 1162

-

Texas Instruments LMX1860SEPEVM评估模块数据手册2025-07-29 811

-

LMK01000高性能时钟缓冲器、分频器和分配器数据表2024-08-21 485

-

AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整2021-03-21 1032

-

ADI发布新款时钟缓冲器和分频器IC AD95082013-02-21 5035

-

德州仪器推出超低噪声底限及附加抖动时钟缓冲器2012-04-05 1469

全部0条评论

快来发表一下你的评论吧 !