Texas Instruments ADC3910D125EVM评估模块技术解析

描述

Texas Instruments ADC3910D125EVM ADC评估模块(EVM)用于评估ADC3910D125系列高速模数转换器(ADC)。ADC3910D125EVM配备有ADC3910D125,这是一个10位双通道ADC,具有LVCMOS接口,运行速度高达125MSPS。Texas Instruments ADC3910D125EVM可用于评估所有器件速度等级:25MSPS、65MSPS和125MSPS。

数据手册:*附件:Texas Instruments ADC3910D125EVM ADC评估模块 (EVM)数据手册.pdf

特性

- 双通道

- 超低功耗

- 一个时钟周期延迟

- 缓冲输入

- 32引脚VQFN (4 mm x 4 mm),占用空间小

电路板概述

Texas Instruments ADC3910D125EVM评估模块技术解析

一、产品核心特性

ADC3910D125EVM是德州仪器(TI)推出的一款高性能模数转换器评估模块,专为ADC3910D125系列高速ADC设计。该评估板具有以下突出特点:

关键性能参数:

- 10位双通道ADC:支持25MSPS/65MSPS/125MSPS三种速率等级

- 超低功耗设计:优化供电架构实现高效能转换

- 极低延迟:仅1个时钟周期转换延迟

- 紧凑封装:32引脚VQFN(4mm×4mm)

- 灵活接口:支持LVCMOS数字接口

典型应用场景:

- 无线电接收机

- 激光雷达(LiDAR)系统

- 低延迟控制环路

- 激光扫描仪

- GPS接收机

- 源测量单元(SMU)

- 检测设备

二、硬件架构解析

1. 系统组成架构

评估模块采用分层设计架构:

- 模拟前端:

- 集成巴伦实现单端转差分信号

- 带缓冲输入级提高驱动能力

- 时钟子系统:

- 支持外部LVCMOS时钟输入

- 内置时钟调理电路

- 数字接口:

- FMC连接器对接TSW1418EVM

- 支持DDR数据传输模式

2. 关键电路设计

- 电源管理:

- 支持+12V单电源输入

- 多级LDO提供清洁电源轨

- 信号链设计:

- 50Ω匹配输入阻抗

- 交流耦合输入配置

- ESD保护:

- 全接口2kV HBM防护

- TVS二极管阵列保护关键节点

三、开发环境搭建

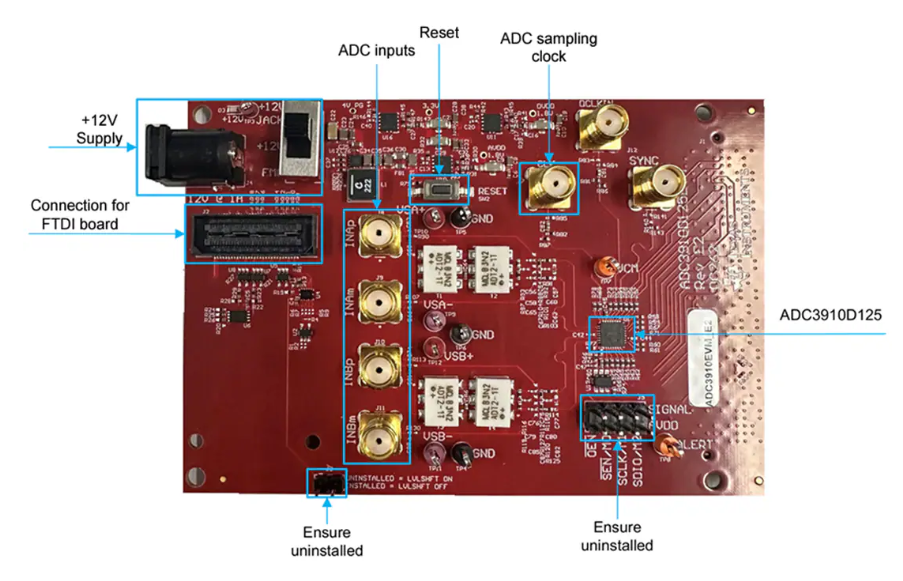

1. 硬件连接步骤

- 通过FMC连接器对接TSW1418EVM

- 安装FTDI板至J2接口

- 配置TSW1418EVM跳线(J13 pin2-3)

- 连接+12V电源至筒形插座

- 分别用mini USB连接PC与FTDI板、TSW1418EVM

- 连接滤波后的时钟信号至J7(CLK)

- 连接模拟输入至J8(INAp)/J10(INBp)

2. 软件安装要求

| 软件组件 | 版本要求 | 功能说明 |

|---|---|---|

| HSDC Pro | 最新版 | 数据采集与分析 |

| Python | 3.10.9 | API运行环境 |

| Vivado Lab | 2023.2 | FPGA编程工具 |

| VS Code | 最新版 | 开发环境 |

四、性能评估方法

1. 测试信号要求

- 时钟信号:

- 推荐Rohde & Schwarz SMA100A/B信号源

- 带通滤波(带宽5%-15%目标频率)

- 125MHz典型测试频率

- 模拟输入:

- 10.097503662MHz测试信号

- 8.2dBm输入电平

- 推荐使用高质量SMA电缆

2. 数据采集流程

- 运行ADC3910D125EVM_API_Rev0.1.py初始化ADC

- 使用Vivado Lab编程FPGA(加载10b_DDR.bit)

- 启动HSDC Pro软件

- 通过TCL命令触发数据捕获

- 分析FFT频谱结果

典型测试结果:

在FS=125MSPS,Fin=10.097503662MHz@8.2dBm条件下,模块表现出优良的线性度和动态范围。

五、设计资源获取

TI提供完整的开发资源支持:

- 原理图:官网产品页面下载

- PCB布局:包含完整Gerber文件

- 物料清单(BOM) :标注关键器件规格

- API软件包:包含Python控制脚本

- 参考设计:多场景应用方案

六、应用设计建议

- 电源设计:

- 推荐使用低噪声LDO

- 每路电源配置1μF+0.1μF去耦电容

- 布局布线:

- 敏感模拟走线远离数字区域

- 保持完整地平面

- 时钟信号采用差分走线

- 热管理:

- 评估板θJA=52.2°C/W

- 持续工作建议增加散热措施

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Texas Instruments UCC27624EVM驱动器评估模块技术解析2025-09-18 874

-

Texas Instruments CDCBT1001EVM评估模块技术解析2025-09-15 1098

-

Texas Instruments LMR51450EVM同步降压转换器评估模块技术解析2025-09-01 1247

-

Texas Instruments LP5811-10EVM驱动器评估模块 (EVM)数据手册2025-07-30 871

-

Texas Instruments ADS9219EVM评估模块数据手册2025-07-28 880

-

Texas Instruments PGA849EVM 评估模块(EVM)数据手册2025-07-24 812

-

Texas Instruments TMUXS7614DEVM开关评估模块 (EVM)数据手册2025-07-21 799

-

Texas Instruments TPS25762DQ1EVM 评估模块(EVM)数据手册2025-07-18 967

-

Texas Instruments TPSM83102EVM-125 评估模块(EVM)数据手册2025-07-15 803

-

Texas Instruments TRF0208-SP-EVM/TRF0208-SEP-EVM评估模块数据手册2025-07-06 987

-

Texas Instruments ADC3669EVM ADC评估模块 (EVM)数据手册2025-07-04 1031

-

ADC3910D125评估模块2024-11-05 425

全部0条评论

快来发表一下你的评论吧 !