LMK04832SEPEVM评估模块技术解析与应用指南

描述

Texas Instruments LMK04832SEPEVM评估模块为LMK04832-SEP开发提供了绝佳的入门方法。LMK04832-SEP是一款空间级、超低噪声、JESD204B/C、双环路时钟抖动清除器。TI LMK04832SEPEVM评估模块采用LMK04832-SEP作为工程模型,仅用于工程评估。LMK04832-SEP和LMK04832SEPEVM不适合用于认证、生产、辐射测试或飞行用途。

数据手册:*附件:Texas Instruments LMK04832SEPEVM评估模块数据手册.pdf

特性

- 单事件锁存(SEL)和单事件功能中断(SEFI)抑制 > 43MeV.cm2/mg

- JESD204B/C支持需要系统基准 (SYSREF) 的空间应用

- 6GHz外部压控振荡器 (VCO) 或分配输入

- 多模

- 双锁相环 (PLL)

- 单PLL

- 包含时钟分配

- 用于双环路时钟抖动清除器的完整电路,经过性能优化和测试

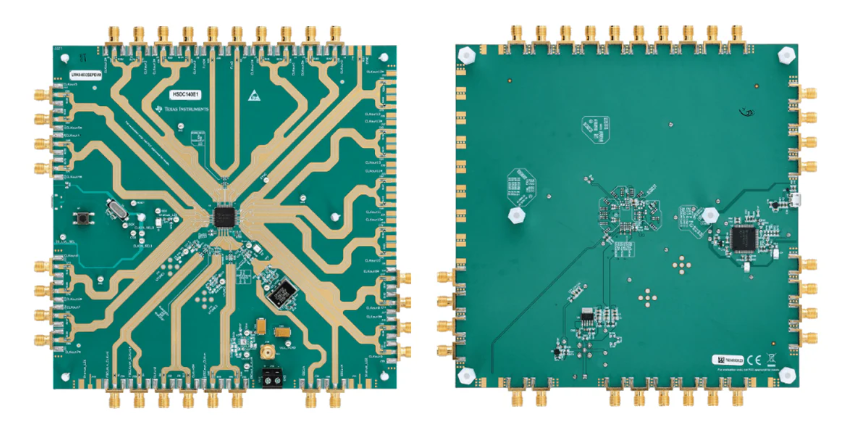

PCB布局

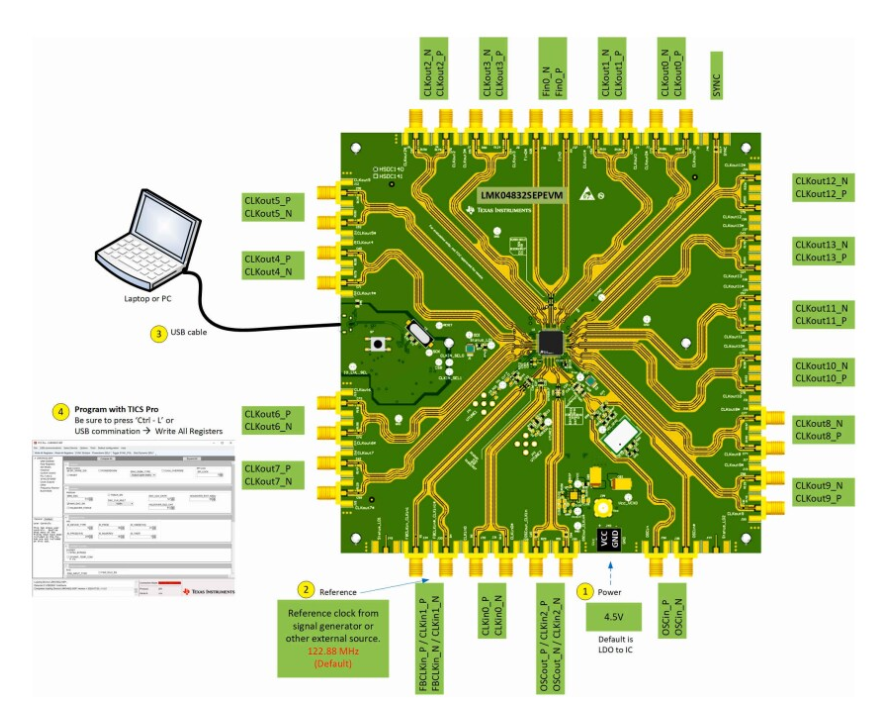

快速入门

LMK04832SEPEVM评估模块技术解析与应用指南

一、产品概述

LMK04832SEPEVM是德州仪器(TI)推出的太空级超低噪声JESD204B双环路时钟抖动消除器评估模块,基于LMK04832-SEP器件设计。该评估板专门用于工程评估,不适合用于资格认证、生产、辐射测试或飞行用途。

核心特性:

- 采用LMK04832-SEP太空级时钟抖动消除器

- 双PLL架构设计(PLL1+PLL2)

- 集成122.88MHz VCXO(默认配置)

- 支持12路差分时钟输出(LVPECL/LVDS/HSDS/CML)

- 输入频率范围:122.88MHz(默认配置)

- 输出频率范围:最高245.76MHz

二、硬件架构分析

1. 电源管理系统

- 输入保护:4.5-5V主供电输入,通过TPS73801-SEP LDO稳压至3.3V

- 关键电源轨:

- VDD_CORE:0.75V/0.85V可调

- VDD_DDR4:1.2V

- SoC_DVDD3V3:3.3V

- 独立VCXO供电:采用LP5900 LDO提供3.3V

2. 时钟路径设计

- 参考输入:

- CLKin1 SMA接口(122.88MHz默认)

- OSCin接口连接板载Crystek CVHD-950 VCXO

- 输出配置:

- 12路差分时钟输出

- 可编程输出格式(LVPECL/LVDS/HSDS/CML)

- 每对输出可独立配置为设备时钟或SYSREF时钟

三、关键性能参数

1. PLL性能指标

- PLL1:

- 相位检测频率:1.024MHz

- 环路带宽:14Hz(窄带宽设计)

- 相位裕度:50°

- PLL2:

- 相位检测频率:122.88MHz

- 集成VCO频率范围:1966-2949MHz

- 环路带宽:210-326kHz

2. 时钟输出特性

- 输出抖动:<100fs RMS(典型值)

- 可编程数字延迟:0-163ns分辨率

- 支持半周期调整(HS)和占空比校正(DCC)

四、评估软件配置

1. TICS Pro基本操作流程

- 启动TICS Pro软件

- 选择设备:Clock Generator/Jitter Cleaner → LMK04832-SEP

- 配置通信接口:USB2ANY模式

- 加载默认配置:"CLKin1 122.88MHz, OSCin 122.88MHz, VCO1 2949.12MHz"

- 执行Ctrl+L写入所有寄存器

2. 关键配置页面

- 时钟输出页面:配置输出格式、分频比、相位延迟

- PLL1和PLL2页面:设置环路参数和分频比

- SYNC/SYSREF页面:配置JESD204B同步功能

- 原始寄存器页面:直接访问所有寄存器

五、典型应用场景

1. 高速数据转换系统

- JESD204B接口时钟同步

- 多通道ADC/DAC时钟分配

- 相位对齐的系统参考时钟(SYSREF)生成

2. 航天电子系统

- 卫星通信时钟网络

- 星载数据处理单元时钟分配

- 抗辐射时钟解决方案

3. 测试测量设备

- 高精度仪器时钟源

- 低抖动参考时钟生成

- 多通道同步测试系统

六、设计注意事项

- PCB布局建议:

- 保持时钟走线对称性

- 控制差分对阻抗(50/100Ω)

- 敏感模拟电源独立布线

- 热管理:

- 确保器件底部散热焊盘良好接地

- 高负载输出考虑增加散热措施

- 测试测量:

- 使用50Ω终端匹配测量高速时钟

- 推荐使用频谱分析仪测量相位噪声

- 避免使用示波器探头直接测量高频信号

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索LMK04832:高性能时钟调节器的卓越之选2026-02-08 400

-

LMK1D1216EVM缓冲器评估模块技术解析与应用指南2025-09-18 940

-

德州仪器LMK1D1212EVM缓冲器评估模块技术解析2025-09-17 993

-

LMK04368EPEVM评估模块技术解析与应用指南2025-09-07 1136

-

LMK3H0102EVM评估模块深度解析与技术应用指南2025-09-05 1121

-

ADC32RF5xEVM评估模块技术解析与应用指南2025-09-02 1104

-

Texas Instruments LMK6EVM评估模块技术解析与应用指南2025-09-01 858

-

LMK5B33216EVM评估模块技术解析与应用指南2025-08-12 1234

-

Texas Instruments LMX1860SEPEVM评估模块数据手册2025-07-29 845

-

LMK01000评估板用户指南2024-11-26 391

-

LMK04832SEPEVM用户指南2024-11-18 591

-

LMK04832 oscin悬空的时候,clkout可以输出时钟吗?2024-11-12 248

-

LMK04832 CMOS输出衰减怎么解决?2024-11-11 726

-

LMK04832-SP时钟抖动清除器2021-03-24 1500

全部0条评论

快来发表一下你的评论吧 !