SN74LV244A Octal Buffer/Driver技术解析:高速3态输出的多功能解决方案

描述

Texas Instruments SN74LV244A和SN74LV244A-Q1 8通道缓冲器/线路驱动器适用于2V至5.5V VCC 电压工作。SN74LV244A和SN74LV244A-Q1设备设计用于改善三态存储器地址驱动器、时钟驱动器及面向总线的接收器和发送器的密度和性能。Texas Instruments SN74LV244A设备由两个4位线路驱动器组成,具有独立的输出使能 (OE) 输入。SN74LV244A-Q1设备符合汽车应用类AEC-Q100标准。

数据手册:

特性

- 工作电压:2V至5.5V V

CC - 最大t

pd:6.5ns(5V时) - 典型V

OLP(输出接地弹跳)- <>

CC= 3.3V,TA= 25°C时)

- <>

- 典型V

OHV(输出VOH下冲)2.3V(V

CC= 3.3V,TA= 25°C时)

- 支持所有端口的混合模式电压操作

- I

off支持局部关断模式运行 - 闭锁性能超过250 mA,符合JESD 17标准

- ESD保护性能超出JESD 22标准

- 2000V人体模型 (A115-A)

- 200V机器模型 (A115-A)

- 1000V充电器件模型 (C101)

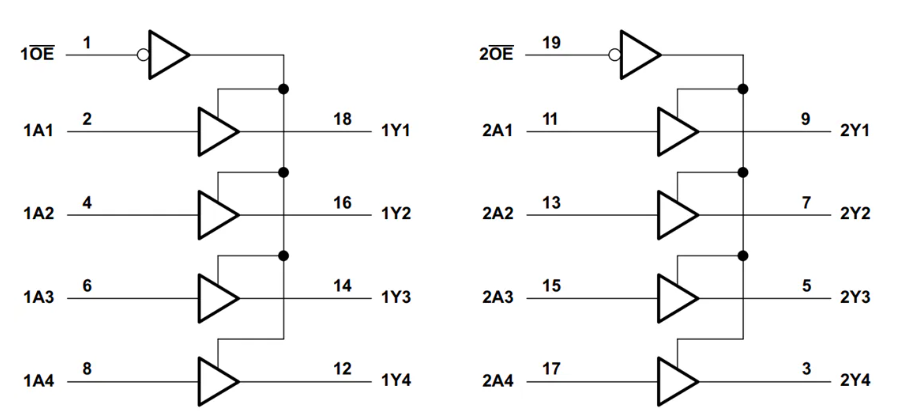

功能框图

SN74LV244A Octal Buffer/Driver技术解析:高速3态输出的多功能解决方案

产品概述

SN74LV244A是德州仪器(TI)推出的一款高性能CMOS逻辑器件,属于LV(低电压)系列产品。该器件包含8个独立的缓冲器/驱动器单元,采用3态输出设计,专为2V至5.5V电压系统优化。

核心特性:

- 宽工作电压范围:2V至5.5V VCC操作

- 超快传输延迟:5V供电时最大6.5ns

- 优化的信号完整性:

- 典型输出地弹(VOLP)<0.8V @3.3V

- 典型VOH下冲(VOHV)>2.3V @3.3V

- 先进的电源管理:

- 支持混合电压操作

- Ioff特性支持部分断电模式

- 增强可靠性:

- 抗闩锁性能超过250mA(JESD 17标准)

- ESD保护:2000V HBM/1000V CDM

功能架构

逻辑结构与引脚配置

器件采用两组独立控制的4位缓冲器结构:

- 控制引脚:

- 1OE(引脚1):控制1A1-1A4输入组

- 2OE(引脚19):控制2A1-2A4输入组

- 信号路径:

- 输入:1A1-1A4(引脚2,4,6,8) / 2A1-2A4(引脚11,13,15,17)

- 输出:1Y1-1Y4(引脚18,16,14,12) / 2Y1-2Y4(引脚9,7,5,3)

封装选项:

- 小型封装:VQFN(RGY/RKS,3.5x4.5mm/4.5x2.5mm)

- 标准封装:SOIC(DW,12.8x10.3mm)

- 薄型封装:TSSOP(PW,6.5x7.8mm)

电气特性分析

关键性能参数

**直流特性(VCC=3.3V,TA=25°C)** :

- 高电平输出(VOH):

- IOH=-8mA时最小2.48V

- IOH=-16mA时最小3.8V

- 低电平输出(VOL):

- IOL=8mA时最大0.44V

- IOL=16mA时最大0.55V

- 静态电流(ICC):最大20μA

交流特性:

| 条件 | 参数 | 值 |

|---|---|---|

| VCC=3.3V | 传输延迟(tpd) | 8.4ns(CL=15pF) |

| 输出使能时间(ten) | 10.6ns | |

| 输出禁用时间(tdis) | 11.7ns | |

| VCC=5V | 传输延迟(tpd) | 5.5ns |

| 输出偏移(tsk(o)) | 1ns |

热特性

热阻参数(θJA) :

- SOIC(DW):102.3°C/W

- TSSOP(PW):128.2°C/W

- VQFN(RGY):34.9°C/W

工作温度范围:-40°C至125°C

应用设计指南

典型电路配置

- 电源设计:

- 推荐0.1μF陶瓷去耦电容靠近VCC引脚

- 双电源系统需匹配电压轨时序

- 输入处理:

- 未用输入必须接VCC或GND

- 推荐10kΩ上拉/下拉电阻

- 输入信号边沿速率>200ns/V

- 输出设计:

- 最大容性负载50pF(保证性能)

- 并联输出可增加驱动能力

- 避免直接连接推挽输出

PCB布局要点

- 关键信号路径:

- 保持差分对对称走线

- 避免90°转角,使用弧形走线

- 电源处理:

- 多层板使用完整地平面

- 去耦电容<5mm距离

- 热管理:

- VQFN封装需焊接散热焊盘

- 高负载应用添加散热过孔

典型应用场景

- 通信基础设施:

- 网络交换机信号缓冲

- 电信背板驱动器

- 工业控制系统:

- 电机驱动板信号隔离

- PLC数字I/O扩展

- 显示技术:

- LED显示屏行列驱动

- 液晶时序控制

- 计算设备:

- 服务器内存地址驱动

- PCIe总线缓冲

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74HCT244 Octal Buffer/Line Driver技术解析与应用指南2025-08-29 1346

-

具有三态输出的八路缓冲器和驱动器SN74LV244A数据表2024-05-06 515

-

SN74LV244A 具有三态输出的八路缓冲器/驱动器2018-10-16 1378

-

SN54LV244A, SN74LV244A,pdf(OCT2010-07-19 699

-

SN74AUC244,pdf(OCTAL BUFFER/DR2010-07-17 5318

-

SN74ACT244-Q1,pdf(Octal Buffer2010-07-16 485

全部0条评论

快来发表一下你的评论吧 !