璞致 PZSDR 系列板卡之 软件无线电 P9009-ADRV9009 硬件说明 16bit ADC & 14bit DAC

电子说

描述

第一章:LMK04828及ADRV9009****简介

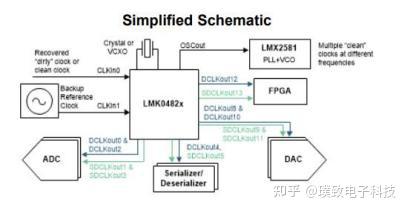

1.1LMK04828简介

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动七个 JESD204B 转换器或其他逻辑器件。

SYSREF 可使用直流和交流耦合提供。不限于 JESD204B 应用,14 个输 出中的每一个均可单独配置为传统时 钟系统的高性能输出。

高性能,加上在功率或性能之间进行权衡的能力、双 VCO、动态数字延

迟、保持和无故障模拟延迟等特性, 使 LMK0482x 系列成为提供灵活的高 性能时钟树的理想选择。

| 功能 | 双环路 PLL |

|---|---|

| 输出数量 | 15 |

| RMS 抖动(fs) | 88 |

| 输出频率(最小值)(MHz) | 0.289 |

| 输出频率(最大)(MHz) | 3080 |

| 输入类型 | LVCMOS、LVDS、LVPECL |

| 输出类型 | LVCMOS、LVDS、LVPECL |

| 供电电压(最小值)(V) | 3.15 |

| 电源电压(最大)(V) | 3.45 |

| 特征 | JESD204B |

| 等级 | 目 录 |

| 工作温度范围(C) | -40 至 85 |

| 输入通道数 | 3 |

4 / 15

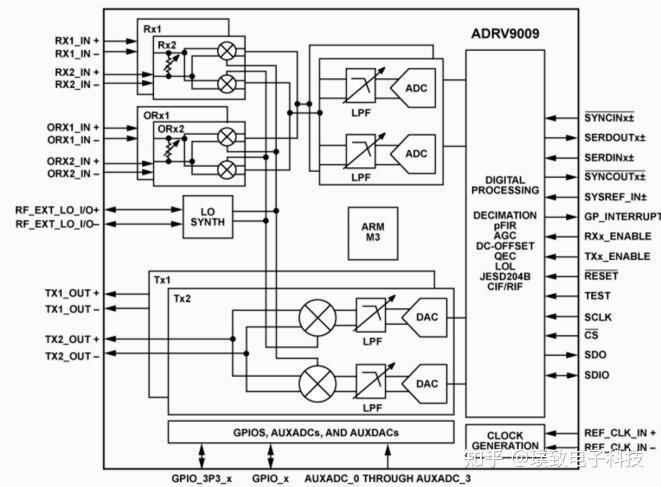

1.2ADRV9009简介

ADRV9009 是一款高度集成的射频(RF) 捷变收发器,提供双发射器和接收 器、集成合成器和数字信号处理 功能。该 IC 提 供 3G、4G 和 5G 宏蜂窝时分 双工(TDD) 基站应用所需的高性能和低功耗的多功能组合。

接收路径由两个独立的、宽带宽的直接转换接收器组成, 具有最先进的动态 范围。该设备还支持宽带宽、时 间共享观察路径接收器 (ORx), 用 于 TDD 应 用。完整的接收子系统包括自动和手动豪减控制、直流失调校 正、正交误差校 正(QEC) 和数字滤波,从而无需在数字基带中使用这些功能。还集成了多种辅助 功能,例如 模拟数字转换器(ADC)、 数模转换器(DAC)、 功率放大器(PA) 的通 用输入/输出(GPIO) 以及射频前端控制。

除了自动增益控制(AGC) 之 外 ,ADRV9009 还具有灵活的外部增益控制 模式,可以非常灵活地动态设置系统级增益。

接收信号通过一组四个高动态范围、连续时间 Z-△ADC 进行数字化,这些 ADC 具有固有的抗混叠功能。与 传统中频(IF) 接收器相比,直接转换架构不 受带外图像混合的影响,且没有混叠,因此放宽了对 RF 滤波器的要求。

发射器使用创新的直接转换调制器,可实现高调制精度和极低的噪声。

观察接收机路径由具有最先进动态范围的宽带宽、直接转换接收器组成。

完全集成的锁相环(PLL) 为发射器(Tx) 和接收器(Rx) 信号路径提供高性 能、低功耗、小数 N RF 频率合成。附加合成器生成转换器、数字电路和串行接 口所需的时钟。多芯片同步机制可同步多个 ADRV9009 芯 片之间的 RF 本 振(LO) 和基带时钟的相位。采取预防措施以提供高性能基站应用所需的隔离。 所有压控振荡 器(VCO) 和环路滤波器元件均已集成。

高速 JESD204B 接口支持高达 12.288 Gbps 的通道速率,在最宽带宽模式 下,每个发射器有两条通道,每 个接收器有一条通道。该接口还支持较低带宽 的交叉模式,从而将高速数据接口通道总数减少到一条。支持 定点和浮点数据 格式。浮点格式允许内部 AGC 对解调器设备不可见。

ADRV9009 的核心可直接由 1.3V 稳压器和 1.8 V 稳压器供电,并通过标准 4 线串行端口进行控制。它包含 全面的省电模式,以最大限度地降低正常使用 时的功耗。ADRV9009 采用 12 mm×12mm、196 球芯片级球栅阵列(CSP_BGA) 封 装。

应用

3G 、4G 和 5G TDD 宏蜂窝基站 TDD 有源天线系统

大规模多输入多输出 (MIMO)

相控阵雷达 电子战

军事通信

便携式测试设备

特征

· 双发射器

· 双接收器

· 双输入共享观测接收器

· 最大接收器带宽:200 MHz

· 最大可调谐发射机合成带宽:450 MHz

· 最大观测接收器带宽:450 MHz

· 完全集成的小数 N 射频合成器

· 完全集成的时钟合成器

· 针对 RF LO 和基带时钟的多芯片相位同步

· JESD204B 数据路径接口

· 调谐范围(中心频率):75 MHz 至 6000 MHz

第二章:PZ-FH9009****开发例程

2.1****功能概述

本例程在 FPGA 内部生成 DDS 信号源,通过 ADRV9009 进行单音信号发射测 试,同时,可以把 ADRV9009 发射的信号,接收回来,用 ILA 进行查看,用户也 可以把数据保存下来导入到 Matlab 等工具进行分析。

2.2****管脚配置

管脚约束如下(根据购买的开发板,自行选择):

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property -dict {PACKAGE_PIN F10 IOSTANDARD LVCMOS18} [get_ports led]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets IBUFDS_inst/O]

set_property -dict {PACKAGE_PIN R10 IOSTANDARD LVDS DIFF_TERM_ADV TERM_100 IBUF_LOW_PWR FALSE} [get_ports sysref_p ]

set_property -dict {PACKAGE_PIN T13 IOSTANDARD LVDS DIFF_TERM_ADV TERM_100} [get_ports syncout0_p ]

set_property -dict {PACKAGE_PIN L16 IOSTANDARD LVDS DIFF_TERM_ADV TERM_100} [get_ports fpga_gc_clk_p ]

set_property -dict {PACKAGE_PIN V12 IOSTANDARD LVDS} [get_ports syncinb0_p ]

set_property -dict {PACKAGE_PIN V11 IOSTANDARD LVDS} [get_ports syncinb0_n ]

set_property -dict {PACKAGE_PIN Y5 IOSTANDARD LVDS} [get_ports

syncinb1_p ]

set_property -dict {PACKAGE_PIN AA5 IOSTANDARD LVDS} [get_ports syncinb1_n ]

set_property -dict {PACKAGE_PIN G8 } [get_ports ref_clk0_p ]; ##

set_property -dict {PACKAGE_PIN L8 } [get_ports ref_clk1_p ]; ##

set_property -dict {PACKAGE_PIN F2} [get_ports rx_data_p[0] ]; ##

set_property -dict {PACKAGE_PIN J4} [get_ports rx_data_p[1] ]; ##

set_property -dict {PACKAGE_PIN K2} [get_ports rx_data_p[2] ]; ##

set_property -dict {PACKAGE_PIN H2 } [get_ports rx_data_p[3] ]; ##

set_property -dict {PACKAGE_PIN G4 } [get_ports tx_data_p[0] ]; ##

set_property -dict {PACKAGE_PIN F6} [get_ports tx_data_p[1] ]; ##

set_property -dict {PACKAGE_PIN K6} [get_ports tx_data_p[2] ]; ##

set_property -dict {PACKAGE_PIN H6} [get_ports tx_data_p[3] ]; ##

set_property -dict {PACKAGE_PIN W4 IOSTANDARD LVCMOS18} [get_ports

adrv9009_spi_csn ]

set_property -dict {PACKAGE_PIN W5 IOSTANDARD LVCMOS18} [get_ports adrv9009_spi_clk ]

set_property -dict {PACKAGE_PIN V4 IOSTANDARD LVCMOS18} [get_ports adrv9009_spi_mosi ]

set_property -dict {PACKAGE_PIN V3 IOSTANDARD LVCMOS18} [get_ports adrv9009_spi_miso ]

set_property -dict {PACKAGE_PIN L13 IOSTANDARD LVCMOS18} [get_ports adrv9009_tx1_enable ]

set_property -dict {PACKAGE_PIN K13 IOSTANDARD LVCMOS18} [get_ports adrv9009_tx2_enable ]

set_property -dict {PACKAGE_PIN L12 IOSTANDARD LVCMOS18} [get_ports adrv9009_rx1_enable ]

set_property -dict {PACKAGE_PIN K12 IOSTANDARD LVCMOS18} [get_ports adrv9009_rx2_enable ]

set_property -dict {PACKAGE_PIN L10 IOSTANDARD LVCMOS18} [get_ports adrv9009_resetb ]

set_property -dict {PACKAGE_PIN M10 IOSTANDARD LVCMOS18} [get_ports adrv9009_gp_interrupt ]

set_property -dict {PACKAGE_PIN Y2 adrv9009_gpio_rf[0 ] ]

set_property -dict {PACKAGE_PIN AA12 adrv9009_gpio_rf[1 ] ]

set_property -dict {PACKAGE_PIN Y12 adrv9009_gpio_rf[2 ] ]

set_property -dict {PACKAGE_PIN V1 adrv9009_gpio_rf[3 ] ]

set_property -dict {PACKAGE_PIN V2 adrv9009_gpio_rf[4 ] ]

set_property -dict {PACKAGE_PIN V8 adrv9009_gpio_rf[5 ] ]

set_property -dict {PACKAGE_PIN V7 adrv9009_gpio_rf[6 ] ]

set_property -dict {PACKAGE_PIN AB10 adrv9009_gpio_rf[7 ] ]

set_property -dict {PACKAGE_PIN AC11 adrv9009_gpio_rf[8 ] ]

set_property -dict {PACKAGE_PIN AA2 adrv9009_gpio_rf[9 ] ]

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

set_property -dict {PACKAGE_PIN AB8 adrv9009_gpio_rf[10] ]

set_property -dict {PACKAGE_PIN AC8 adrv9009_gpio_rf[11] ]

set_property -dict {PACKAGE_PIN AC12 adrv9009_gpio_rf[12] ]

set_property -dict {PACKAGE_PIN Y1 adrv9009_gpio_rf[13] ]

set_property -dict {PACKAGE_PIN W2 adrv9009_gpio_rf[14] ]

set_property -dict {PACKAGE_PIN W1 adrv9009_gpio_rf[15] ]

set_property -dict {PACKAGE_PIN AA10 adrv9009_gpio_rf[16] ]

set_property -dict {PACKAGE_PIN AA11 adrv9009_gpio_rf[17] ]

set_property -dict {PACKAGE_PIN AB11 adrv9009_gpio_rf[18] ]

set_property -dict {PACKAGE_PIN AC1

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

IOSTANDARD LVCMOS18} [get_ports

lmk04828_reset ]

set_property -dict {PACKAGE_PIN AC4 IOSTANDARD LVCMOS18} [get_ports lmk04828_spi_csn ]

set_property -dict {PACKAGE_PIN AC2 IOSTANDARD LVCMOS18} [get_ports lmk04828_spi_sdio ]

set_property -dict {PACKAGE_PIN AB4 IOSTANDARD LVCMOS18} [get_ports lmk04828_spi_sclk ]

set_property -dict {PACKAGE_PIN AA1 IOSTANDARD LVCMOS18} [get_ports lmk04828_sync ]

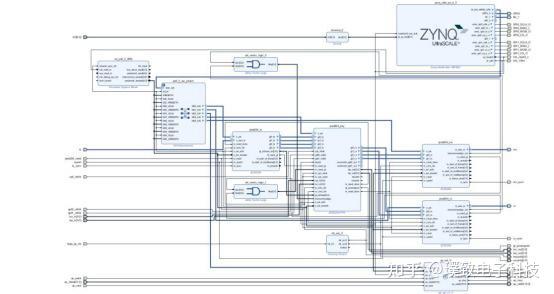

2.3Vivado工程介绍

FPGA 工程,包括 PL 逻辑部分和 PS 处理器配置部分,详情可以看下我们提 供的 Vivado 工程,我们提供的都是源码工程,建议版本跟我们保持一致,也 使用 2019.1,其他版本需要移植,不保证可以正常使用。

Jesd204B-IP 需要 license,可以到 xilinx 官网申请试用。

测试工程的“Sources ”目录如下图:

Block Design 设计如下图:

我们配置 ADRV9009 和 LMK04828 是在 PS 端完成,用的 PS 端的 SPI 控制

器,用户如果需要在 Fpga 端完成的话,可以改成软核加SPI-IP 完成或者纯 Fpga 代码去完成配置部分。

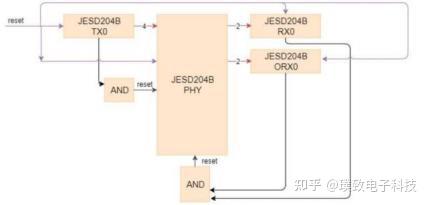

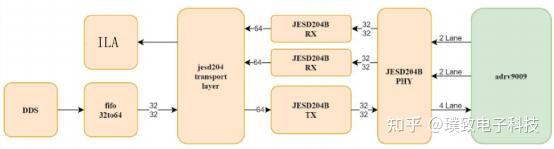

2.3.1简单说明下JESD204B****部分的功能。

JESD204B 是两个 ip core,JESD204 和 JESD204 PHY。每组端口都需要一 个 JESD204 IP,它用来产生或处理了 JESD204 帧格式,TX、RX 和 ORX。

JESD204 PHY 实现了 GTX 物理层,它根据线路速率正确的配置 GTX 硬件的 各级锁相环路设置。

连接关系如下图:

TX 端使用四个 lane 发送通道,RX 端使用两个 lane 接收通道,ORX 端 使用两个接收通道。

当采样率是 245.76MHz 时,txoutclk 是 122.88MHz,rxoutclk 是

245.76MHz。

2.3.2简单说明下FPGA****数据流。

发送方向,tx 端 IQ 数据从 DDS 模块产生,驱动时钟采用 245.76MHz 的 rxoutclk。IQ 两路数据分别进入 fifo_32to64 将 IQ 两路数据分别转换成 64 bit 位宽给 jesd204_transport_layer 模块,时钟采用 txoutclk,

122.88MHz,通过 jesd204_transport_layer 转换为 JESD204 所需的 axi stream 数据流,时钟采用 txoutclk,122.88MHz。

接收方向,rx 端 axi_stream 数据从 JESD204 输出,rx 端 rx_tdata 宽度 64 位,时钟 rxoutclk,245.76MHz。orx 端 orx_tdata 宽度 64 位,时钟

rxoutclk。rx 端数据通过 jesd204_transport_layer 转换位 16bit IQ 数据 流,通过 ILA 显示。

数据流图如下图:

2.4****裸机部分介绍

裸机部分的 demo 我们参考了 ADI 的 NOOS 工程进行了修改,链接如下:

https://wiki.analog.com/resources/eval/user-guides/mykonos/no-os-setup

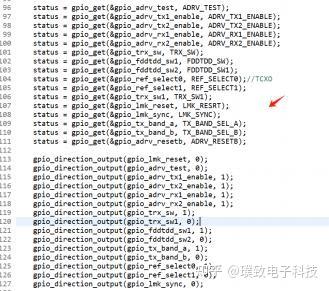

顶层文件是 headless.c,我们首先执行了 GPIO 的相关初始化,如下图:

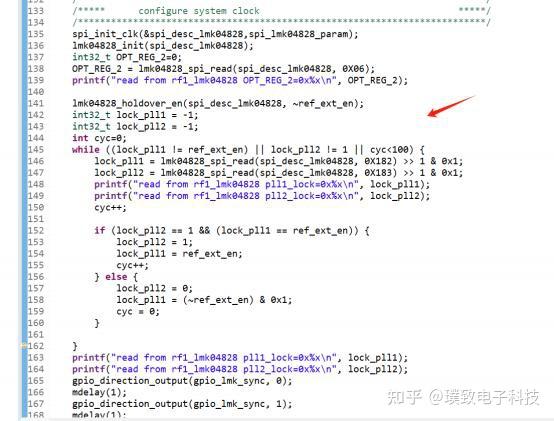

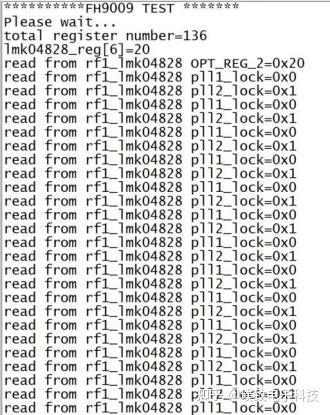

然后我们初始化了 LMK04828 芯片,采用的三线 SPI 总线进行配置,如下图:

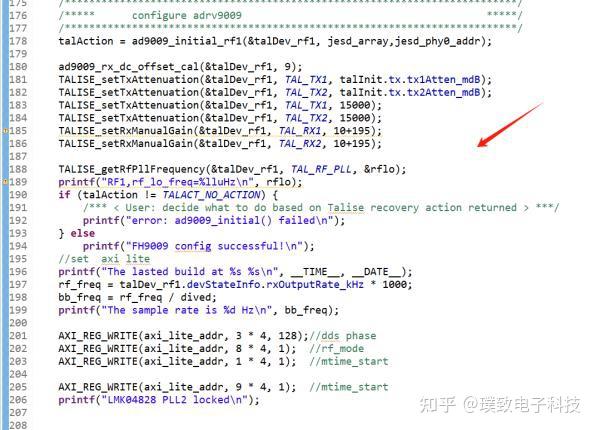

最后我们初始化 ADRV9009 芯片以及控制 ADRV9009 进行收发测试。

初始化 ADRV9009 时用到了用户自定义文件,本工程中是 talise_config.c 和 talise_config.h。

这两个文件由 ADRV9009 Transceiver Evaluation Software 产生。这个软 件可以在以下链接下载:

http://www.analog.com/cn/license/licensing-agreement/transceiver-evaluation-software.html

Device clock 默认选择 122.88MHz。

JESD204B 速率计算方法如下:

发送端=采样率*位宽/通道数=245.76MHz*80/4=4915.2Mbps

接收端=采样率*位宽/通道数=245.76MHz*80/2=9830.4Mbps 代码部分如下图:

2.5****运行测试说明

通过 SDK 下载完成后,串口会输出 log 信息,我们可以通过 log 信息查看 ADRV9009 等相关情况。

串口 LOG 如下图:

RX 部分测试,用回环射频缆将 TX 和 RX 回环,让 Vivado 工程中的 ILA 运 行,我们点击红色方框抓取数据,然后切换到模拟显示,如下图:

TX 部分测试,我们接到频谱分析仪进行查看分析,如下图:

审核编辑 黄宇

-

璞致 PZSDR 系列板卡之 P159 软件无线电硬件说明-ZU15EG+ADRV9009 16bit ADC & 14bit DAC2025-09-05 1866

-

PZSDR 软件无线电 开发板系列板卡之P201Pro P203Pro 硬件说明—AD9361 AD93632025-08-27 1791

-

请问如何使用 gpio 模式的 adrv9009 快速跳转?2025-08-13 4141

-

ADRV9009的datasheet中各等级电压的功耗是多少?2024-01-05 678

-

AD9088: 阿波罗MxFE Octal, 16Bit, 16PSS RF DAC和Octal, 12Bit, 8 PSS RF ADC初步数据表 ADI2023-10-09 234

-

FMC子卡设计方案保存:FMCJ450-基于ADRV9009的双收双发射频FMC子卡2022-07-27 17609

-

adrv9009_API有什么功能?2022-02-23 1450

-

基于Xilinx XC7Z100+ADRV9009的双收双发无线电射频板卡2021-09-02 4751

-

9009开发板学习资料第428篇:基于XC7Z100+ADRV9009的双收双发无线电射频板卡 ADRV9009板卡 XC7Z100板卡 XC7Z100+ADRV90092021-07-09 5671

-

基于XC7Z100+ADRV9009的双收双发无线电射频板卡2020-12-21 1153

-

ADC3444IRTQT详细参数IC ADC 14BIT PIPELINED 56QFN2020-09-04 839

-

ADRV9009板卡学习资料:FMCJ450-基于ADRV9009的射频收发模块2020-03-20 3501

-

如何使用ADRV9009评估平台进行性能测试2019-05-21 6256

-

请问如何正确测量AD7988-5 16bit ADC DC&AC performance?2018-10-09 1817

全部0条评论

快来发表一下你的评论吧 !