ADC3564低噪声超低功耗14位125MSPS高速ADC技术解析

描述

Texas Instruments ADC3564低噪声超低功耗模数转换器 (ADC) 是一款低功耗设计的14位125 MSPS模数转换器。该器件具有-156dBFS/Hz噪声频谱密度以及出色的线性动态范围。ADC3564提供IF采样支持,因此适合用于各种应用。仅一个时钟周期的短延迟对高速控制环路有益。该ADC在125MSP时仅消耗137mW,并且随采样速率降低,功耗变化非常好。

数据手册:*附件:Texas Instruments ADC3564低噪声超低功耗ADC数据手册.pdf

Texas Instruments ADC3564使用串行LVDS (SLVDS) 接口输出数据。该特性可最大限度地减少数字互连数量。该器件支持半通道、单通道和双通道选项。该器件是引脚对引脚兼容系列,具有不同速度等级。它采用40引脚VQFN封装,支持–40°C至+105°C扩展工业温度范围。

特性

- 14位125MSPS ADC

- 噪声基底:–156dBFS/Hz

- 超低功耗:137mW(在125Msps时)

- ≤ 2个时钟周期延迟

- 14位分辨率,无失码

- INL:±1.5LSB;DNL:±0.5LSB

- 基准:外部或内部

- 1200MHz (3dB) 输入带宽

- -40°C至+105°C工业温度范围

- 片上数字滤波器(可选)

- 抽取2、4、8、16、32

- 32位NCO

- 串行LVDS数字接口(2线、1线和1/2线)

- 小占位面积:40-WQFN (5mm × 5mm) 封装

- 频谱性能 (f

IN= 10MHz)- SNR:77.5dBFS

- SFDR:80dBc HD2、HD3

- SFDR:95dBFS最差杂散

- 频谱性能 (f

IN= 70MHz)- SNR:75dBFS

- SFDR:75dBc HD2、HD3

- SFDR:90dBFS最差杂散

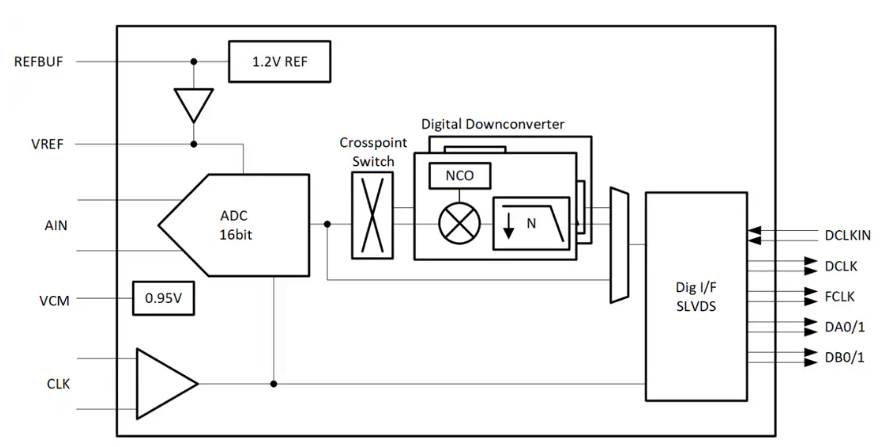

简化框图

ADC3564低噪声超低功耗14位125MSPS高速ADC技术解析

一、产品概述

ADC3564是德州仪器(TI)推出的一款14位125MSPS低噪声、超低功耗高速模数转换器,采用5mm×5mm WQFN-40封装。该器件具有-156dBFS/Hz的噪声谱密度和仅137mW@125MSPS的功耗,专为需要高动态范围和高能效的应用设计,如工业监测、热成像、软件定义无线电和雷达系统等。

核心特性:

- 超低噪声:-156dBFS/Hz噪声谱密度(fIN=5MHz)

- 卓越动态性能:77.5dBFS SNR、80dBc HD2/HD3@10MHz

- 超低功耗:137mW@125MSPS,支持功耗分级调节

- 极低延迟:≤2时钟周期(1-wire SLVDS接口)

- 宽输入带宽:1.4GHz(-3dB),支持IF采样

- 灵活数字处理:集成可编程数字下变频器(DDC),支持2/4/8/16/32倍实数/复数抽取

- 工业级温度范围:-40°C至+105°C

二、架构与关键电路设计

1. 模拟信号链架构

ADC3564采用创新的流水线架构与电容阵列DAC组合设计:

- 前端采样网络:8kΩ差分输入阻抗,5.4pF输入电容

- 宽带采样保持:支持1.4GHz全功率带宽

- 参考电路:可选内部1.6V参考(±3%精度)或外部1.2V/1.6V参考

2. 数字下变频器(DDC)

关键功能单元:

- 32位NCO:调谐范围±FS/2,频率分辨率0.03Hz@125MSPS

- 复数混频器:支持6dB数字增益补偿

- 抽取滤波器:80%通带带宽,>85dB阻带抑制

- 双通道处理:支持独立频段分离(DDC MUX功能)

工作模式:

- 复数模式:输出I/Q数据,适用于频移应用

- 实数模式:作为低通滤波器,功耗降低30%

三、关键性能参数

1. 动态性能(125MSPS, -1dBFS输入)

| 参数 | 5MHz输入 | 10MHz输入 | 70MHz输入 |

|---|---|---|---|

| SNR(dBFS) | 77.5 | 77.5 | 75.5 |

| SFDR(dBc) | 80(HD2) | 80(HD2) | 75(HD2) |

| 无杂散动态范围 | 92 | 95 | 84 |

| ENOB(bits) | 12.6 | 12.6 | 12.3 |

2. 接口时序特性

- 延迟特性:

- 1-wire模式:1时钟周期

- 2-wire模式:2时钟周期

- SLVDS接口速率:

- 14位2-wire:875Mbps/通道

- 16位1-wire:1Gbps

四、典型应用设计

1. 宽带频谱分析前端

设计要点:

- 输入驱动:THS4541 FDA提供3.6Vpp差分驱动

- 抗混叠滤波:

- 7阶椭圆滤波器(30MHz截止)

- 配合8倍抽取实现240MHz有效带宽

- 时钟设计:

- LMK04828提供<100fs抖动时钟

- 差分布线长度匹配±50μm

PCB布局关键:

- 采样网络对称布局

- VREF去耦电容紧贴引脚(10μF+0.1μF组合)

- SLVDS差分对等长(±5ps偏差)

2. 多通道采集系统同步

同步方案:

- 时钟分配:

- 使用LMK04828扇出缓冲

- 添加ADCLK854时钟缓冲器

- 数据对齐:

- 通过SYNC引脚复位NCO相位

- FPGA基于FCLK进行通道间校准

五、电源与布局指南

1. 电源设计方案

推荐架构:

- 一级转换:TPS62821(3.3V@93%效率)

- 二级稳压:TPS7A4701 LDO(1.8V, 4μVRMS噪声)

- 去耦方案:

- 每电源引脚10μF+0.1μF MLCC

- 铁氧体磁珠隔离模拟/数字供电

2. 热设计考虑

- PCB散热:

- 2oz铜厚

- 散热过孔阵列(φ0.3mm, 1mm间距)

- 结温控制:

- θJA=30.7°C/W

- 最大功耗时ΔT≈4.2°C

六、配置与编程

1. 工作模式设置

通过SPI接口(20MHz时钟)配置:

- 基准模式:寄存器0x0E[2:1]

- 00:内部基准

- 01:外部1.2V(REFBUF引脚)

- 10:外部1.6V直接输入

- 接口模式:寄存器0x07[2:0]

- 011:2-wire LVDS

- 100:1-wire LVDS

- 抽取设置:寄存器0x25[6:4]

2. 输出位映射

支持14/16/18/20位可编程输出格式,通过0x39-0x88寄存器实现:

- 数据重组:可交换I/Q顺序

- 位宽扩展:零填充LSB实现高位对齐

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC3664 双通道、14位、125MSPS、高信噪比、低功耗ADC技术手册2025-11-01 1160

-

ADC3564 技术文档总结2025-10-30 798

-

ADC3910D065 10 位高速低功耗 ADC 技术文档总结2025-10-24 1247

-

德州仪器ADC3910系列:高性能低功耗10位125MSPS ADC技术解析2025-09-05 1567

-

ADC3544超低功耗、14位、125MSPS高速模数转换器(ADC)数据表2024-07-18 599

-

ADS41xx 14、12位、65MSPS或125MSPS超低功耗ADC数据表2024-07-17 901

-

ADC3564 14位、125MSPS、低噪声、超低功耗ADC数据表2024-07-12 509

-

ADC3564 单通道、14 位、125 毫秒/分钟、高信噪比、低功耗模数转换器,带 SLVDS 接口2022-09-29 14903

-

14位25Msps至125Msps八路ADC2021-04-26 755

-

非常低功耗的 12 位 / 14 位 25Msps 至 125Msps ADC 在 125Msps 时以低于 100mW 工作2021-03-19 792

全部0条评论

快来发表一下你的评论吧 !