一些关于多层PCB叠层设计的原则

描述

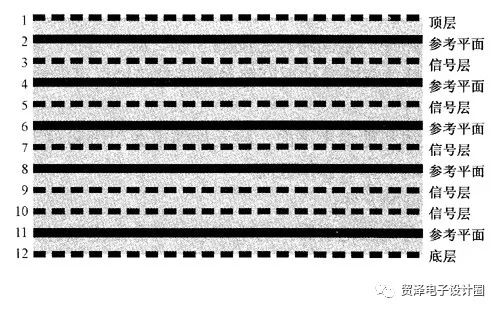

多层PCB通常用于高速、高性能的系统,其中一些层用于电源或地参考平面,这些平面通常是没有分割的实体平面。无论这些层做什么用途,电压为多少,它们将作为与之相邻的信号走线的电流返回路径。构造一个好的低阻抗的电流返回路径最重要的就是合理规划这些参考平面的设计。图1所示为一种典型多层PCB叠层配置。

信号层大部分位于这些金属实体参考平面层之间,构成对称带状线或是非对称带状线。此外,板子的上、下两个表面(顶层和底层),主要用于放置元件的焊盘,其上也有一些信号走线,但不能太长,以减少来自走线的直接辐射。

图1 一种典型多层PCB叠层配置

通常用P表示参考平面层;S表示信号层;T表示顶层;B表示底层。下面以一个12层的PCB来说明多层PCB的结构和布局,如图6-14所示,其层的用途分配为“T—P—S—P—s—P—S—P—S—s—P—B”。

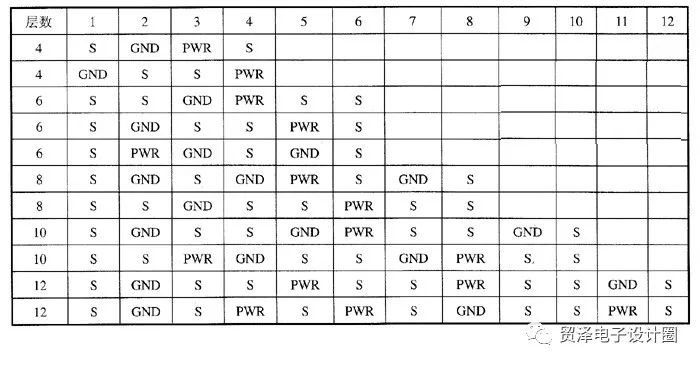

下面是一些关于多层PCB叠层设计的原则。

1

为参考平面设定直流电压:解决电源完整性的一个重要措施是使用去耦电容,而去耦电容只能放置在PCB的顶层和底层,去耦电容的效果会严重受到与其相连的走线、焊盘,以及过孔的影响,这就要求连接去耦电容的走线尽量短而宽,过孔尽量短。如图所示,将第2层设置成分配给高速数字器件(如处理器)的电源;将第4层设置成高速数字地;而将去耦电源放置在PCB的顶层;这是一种比较合理的设计。此外,要尽量保证由同一个高速器件所驱动的信号走线以同样的电源层作为参考平面,而且此电源层为高速器件的电源。

2

确定多电源参考平面:多电源层将被分割成几个电压不同的实体区域,如图所示中将第11层分配为多电源层,那么其附近的第10层和底层上的信号电流将会遭遇不理想的返回路径,使返回路径上出现缝隙。对于高速信号,这种不合理的返回路径设计可能会带来严重的问题。所以,高速信号布线应该远离多电源参考平面。

3

多个地敷铜层可以有效地减小PCB的阻抗,减小共模EMI。

4

信号层应该和邻近的参考平面紧密耦合(即信号层和邻近敷铜层之间的介质厚度要很小);电源敷铜和地敷铜应该紧密耦合。

5

合理设计布线组合:为了完成复杂的布线,走线的层间转换是不可避免的,而把同一个信号路径所跨越的两个层称为一个“布线组合”。信号层间转换时要保证返回电流可以顺利地从-个参考平面流到另一个参考平面。事实上,最妤的布线组合设计是避免返回电流从一个参考平面流到另一个参考平面,而是简单地从参考平面的一个表面流到另一个表面。如图所示中,第3层和第5层、第5层和第7层,以及第7层和第9层都可以作为一个布线组合。但是把第3层和第9层作为一个布线组合就不是合理的设计,它需要返回电流从第4层耦合到第6层,再从第6层耦合到第8层,这条路径对于返回电流并不通畅。尽管可以通过在过孔附近放置去耦电容或者减小参考平面间的介质厚度来减小地弹,但并非上策,在实际系统中可能还无法实现。

6

设定布线方向:在同一信号层上,保证大多数布线的方向是一致的,同时与相邻信号层的布线方向正交。如图所示中,可将第3层和第7层的布线方向设为“南北”走向,而将第5层和第9层的布线方向设为“东西”走向。 针对不同的系统,其叠层设计的配置有所不同,下面列出一些常用的配置,如表所示。

-

PCB叠层设计2016-05-17 0

-

PCB叠层设计的原则和结构2018-09-18 0

-

高速PCB多层板叠层设计原则2018-11-27 0

-

【资料】一些关于多层PCB叠层设计的原则2021-03-25 0

-

【精选资料】PCB设计资料大全(珍藏系列)2021-03-26 0

-

【资料】浅谈PCB叠层设计2021-08-04 0

-

多层PCB如何定义叠层呢?求解2023-04-11 0

-

为什么要进行PCB叠层2020-11-03 4763

-

6个关于多层PCB叠层设计的原则资料下载2021-04-26 854

-

介绍一些PCB布局的思路和原则2023-05-17 1106

-

6层PCB叠层设计指南2023-10-16 2316

-

PCB叠层结构设计详解2022-09-30 2245

-

PCB设计中的叠层原则2023-11-13 1789

全部0条评论

快来发表一下你的评论吧 !