LMK5C22212A网络同步器技术文档总结

描述

该LMK5C22212A是一款高性能网络同步器和抖动清除器,旨在满足无线通信和基础设施应用的严格要求。

网络同步器集成了 2 个 DPLL,可提供无中断开关和抖动衰减,具有可编程环路带宽,无需外部环路滤波器,从而最大限度地提高灵活性和易用性。每个 DPLL 相位将成对的 APLL 锁定到基准输入。

APLL1 采用 TI 专有的体声波 (BAW) 技术(称为 BAW APLL)的超高性能 PLL,可在 491.52MHz 时生成典型值为 40fs/最大 12kHz 至 20MHz RMS 抖动为 60fs 的输出时钟,与 XO 和 DPLL 基准输入的抖动和频率无关。APLL2/DPLL2 提供了第二频率和/或同步域的选项。

*附件:lmk5c22212a.pdf

基准验证电路监控 DPLL 基准时钟,并在检测到切换事件时在输入之间执行无中断切换。可以启用零延迟模式 (ZDM) 和相位消除,以控制从输入到输出的相位关系。

该器件可通过I2C或SPI进行完全编程。集成的EEPROM可用于自定义系统启动时钟。该器件还具有出厂默认ROM配置文件作为回退选项。

特性

- 基于超低抖动 BAW VCO 的无线基础设施和以太网时钟

- 40MHz时典型值为40fs/最大RMS抖动为57fs(491.52MHz时)

- 245.76MHz时50fs(典型值)/62fs(最大RMS抖动)

- 2 个高性能数字锁相环 (DPLL),带 2 个模拟锁相环 (APLL)

- 可编程 DPLL 环路滤波器带宽范围为 1mHz 至 4kHz

- < 1ppt DCO调频步长

- 2 个差分或单端 DPLL 输入

- 1Hz (1PPS) 至 800MHz 输入频率

- 数字保持和无中断开关

- 12 个差分输出,具有可编程 HSDS、AC-LVPECL、LVDS 和 HSCL 格式

- 当配置在 OUT0_P/N、OUT1_P/N、GPIO1 和 GPIO2 上配置 6 个 LVCMOS 频率输出时,总频率输出高达 16 个,在 OUT2_P/N 至 OUT11_P/N 上配置 10 个差分输出

- 1Hz (1PPS) 至 1250MHz 输出频率,具有可编程摆幅和共模

- 符合 PCIe Gen 1 至 6 标准

- I2C 或 3 线/4 线 SPI

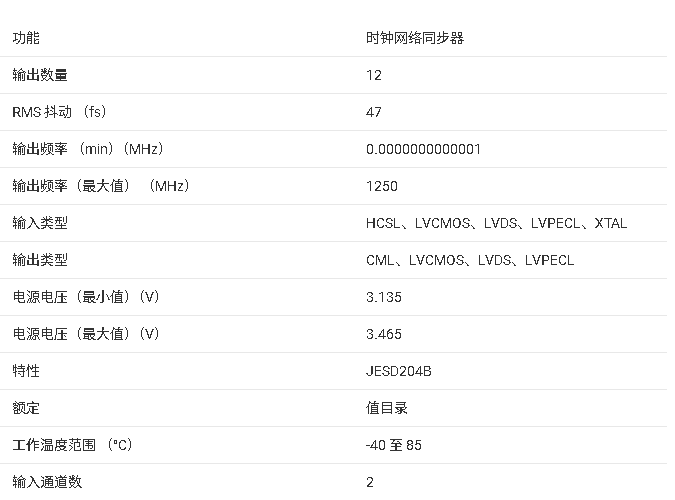

参数

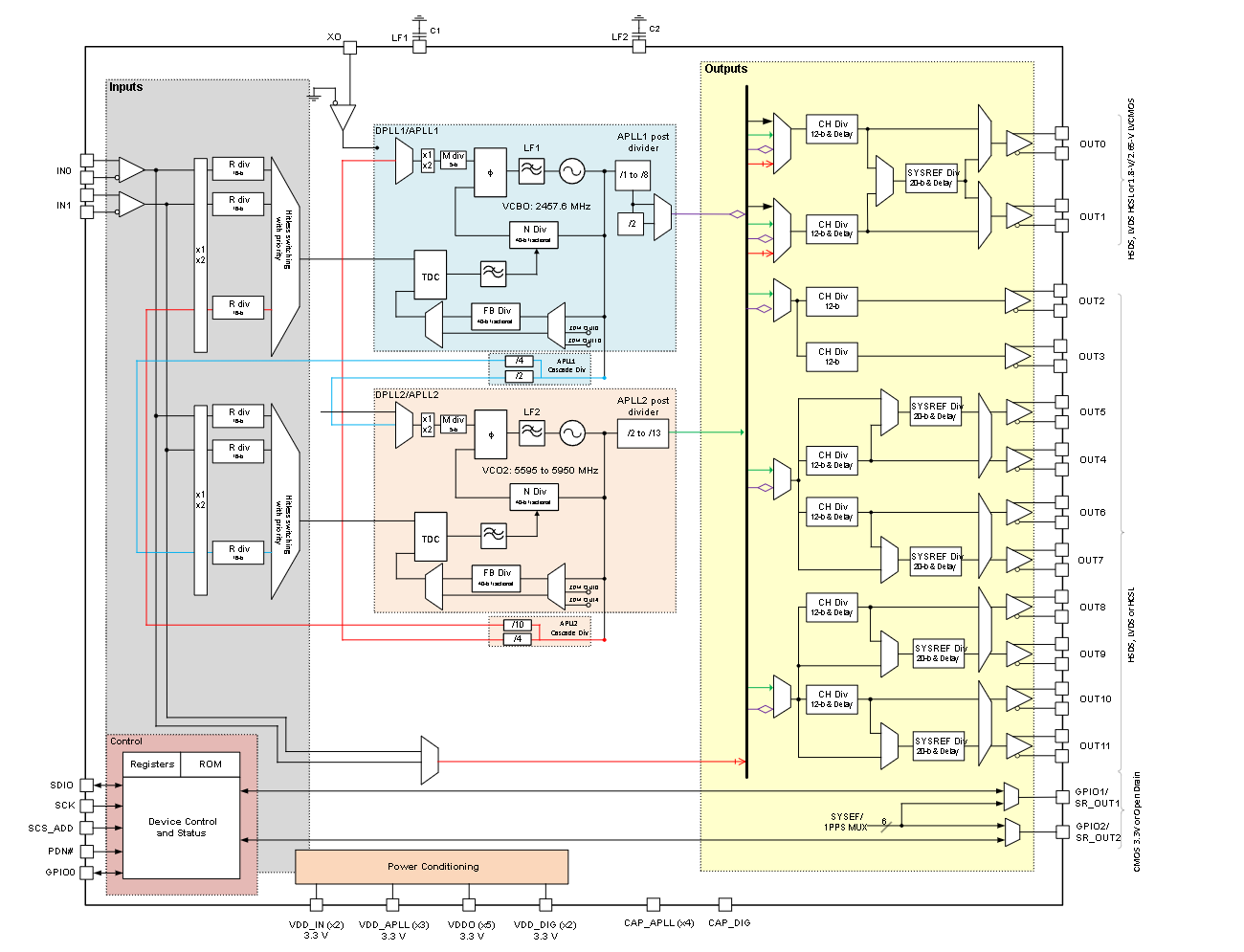

方框图

1. 产品概述

LMK5C22212A是德州仪器(TI)推出的高性能网络同步器和抖动清除器,专为无线通信及基础设施应用设计。其核心特性包括:

- 超低抖动BAW VCO:支持无线和以太网时钟,典型RMS抖动低至40fs(491.52MHz)。

- 双DPLL+双APLL架构:集成2个数字锁相环(DPLL)和2个模拟锁相环(APLL),支持1mHz至4kHz可编程带宽。

- 多格式输出:12路差分输出,支持HSDS、LVDS、HCSL等格式,频率范围1Hz至1250MHz。

- 接口控制:支持I2C或SPI编程,内置EEPROM存储自定义配置。

2. 关键特性

- 时钟性能:

- 491.52MHz输出时典型抖动40fs,最大57fs。

- 支持PCIe Gen1-6合规时钟生成。

- 输入/输出灵活性:

- 2路差分/单端输入(1Hz至800MHz)。

- 12路输出可配置为差分或单端(如1.8V/2.65V LVCMOS)。

- 应用场景:

- 4G/5G无线网络(RRU、小型基站等)。

- 同步以太网(SyncE)、IEEE-1588 PTP二级时钟。

- 光传输网络(OTN)和工业测试设备。

3. 功能模块详解

- APLL1(BAW技术) :

- 基于体声波谐振器,提供超低相位噪声,独立于外部XO抖动。

- 固定频率2457.6MHz ±100ppm,支持分数分频。

- APLL2(LC VCO) :

- 宽调谐范围(5595-5950MHz),适用于多频段需求。

- DPLL功能:

- 支持无中断切换(Hitless Switching)和数字保持模式(Holdover)。

- 可编程DCO模式,频率调整步长<1ppt(万亿分之一)。

4. 封装与电气特性

- 封装:64引脚VQFN(9mm×9mm),带裸露焊盘增强散热。

- 电源要求:

- 核心电压3.135V至3.465V,输出电源3.3V独立供电。

- 功耗典型值750mA(全输出激活时)。

- 环境适应性:工作温度-40°C至85°C,符合工业级标准。

5. 设计支持

- 配置工具:推荐使用TI的TICS Pro软件生成寄存器配置。

- 参考设计:提供典型应用框图(如无线基站时钟架构)。

- 布局建议:强调电源去耦、差分信号阻抗匹配及热焊盘设计。

6. 文档附加信息

- 包含完整引脚定义、时序图、热阻参数及ROM预配置选项。

- 提供PCB布局示例和焊接指南,确保信号完整性。

该文档为硬件工程师提供了从芯片选型到系统集成的全面技术参考,适用于高精度时钟同步需求的通信设备设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

解析LMK5C23208A:高性能网络同步器的卓越之选2026-02-06 286

-

LMK5C33414A网络同步器技术文档总结2025-09-11 941

-

LMK5C23208A网络同步器技术文档总结2025-09-10 674

-

高性能网络同步器LMK5C33216A技术解析与应用2025-09-04 926

-

Texas Instruments LMK5C33216AS1网络同步器数据手册2025-08-03 1149

-

Texas Instruments LMK5C22212A网络同步器数据手册2025-07-05 1028

-

LMK5C33414A网络同步器数据表2024-08-20 409

全部0条评论

快来发表一下你的评论吧 !