LMX1906-SP 芯片技术文档总结

描述

LMX1906-SP 是一款缓冲器、分频器和乘法器,具有高频、超低抖动和 SYSREF 输出。该器件与超低噪声参考时钟源相结合,是时钟数据转换器的典范设计,尤其是在采样高于 3GHz 时。4 个高频时钟输出和附加 LOGICLK 输出中的每一个都与一个 SYSREF 输出时钟信号配对。JESD接口的SYSREF信号可以在内部生成,也可以作为输入传入并重新时钟到器件时钟。该器件可以通过禁用SYSREF输出,将多通道、低偏斜、超低噪声的本地振荡器信号分配到多个混频器。

*附件:lmx1906-sp.pdf

特性

- 贴片 #5962-23202

- 总电离剂量 100krad(不含 ELDRS)

- 单事件闩锁 (SEL) 免疫高达 87MeV - cm2 /mg

- 单事件功能中断 (SEFI) 免疫高达 87MeV - cm2 /mg

- 300MHz至15GHz频率的时钟缓冲器

- 超低噪声

- 6GHz输出时本底噪声为–159dBc/Hz

- 6GHz 输出时为 36 fs 附加抖动(100Hz 至 fCLK)

- 5fs 附加抖动 (100Hz - 100MHz)

- 4 个高频时钟,具有相应的 SYSREF 输出

- 共享除法 1(缓冲区)、2、3、4、5 和 7

- 共享可编程乘法器 x2、x3 和 x4

- 支持引脚模式选项,无需SPI即可配置器件

- LOGICLK 输出与相应的 SYSREF 输出

- 在单独的分库上

- 1、2、4 预分频器

- 1(旁路)、2、...、1023 柱分隔器

- 8 个可编程输出功率级别

- 同步 SYSREF 时钟输出

- 508 次延迟步进调整,每次小于 2.5ps,频率在 12.8GHz 时

- 发生器和中继器模式

- SYSREFREQ 引脚的窗口功能,用于优化时序

- SYNC 功能到所有分部和多个设备

- 2.5V工作电压

- –55ºC 至 125ºC 工作温度

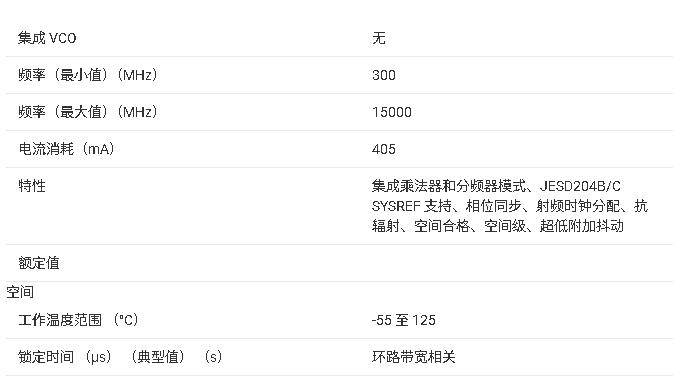

参数

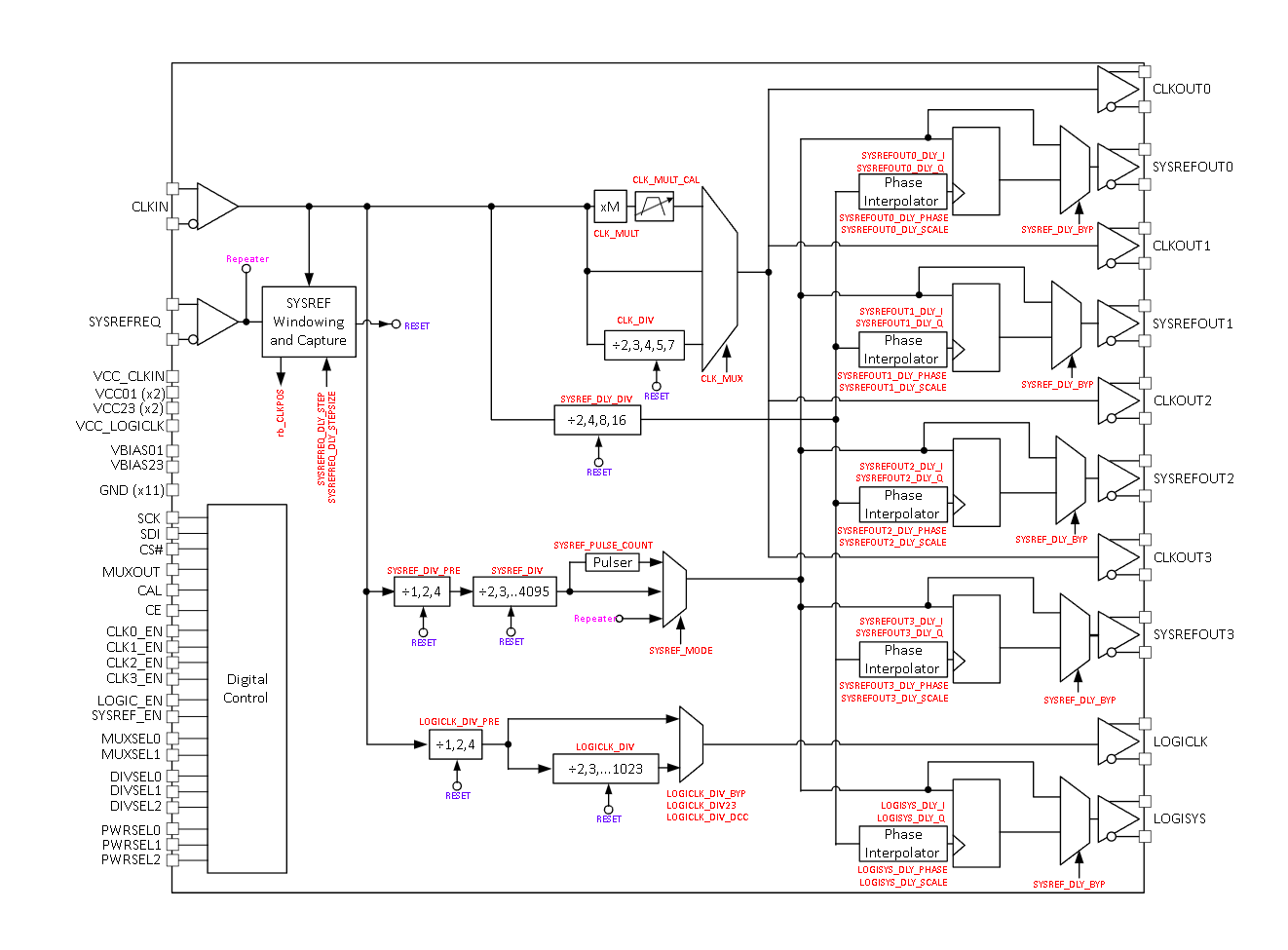

方框图

1. 产品概述

LMX1906-SP是一款航天级低噪声高频JESD204B/C缓冲器、乘法器和分频器,适用于300MHz至15GHz时钟处理。关键特性包括:

- 抗辐射设计:总电离剂量100krad(无ELDRS效应),抗单粒子锁定(SEL)和功能中断(SEFI)。

- 超低噪声:噪声基底-159dBc/Hz(6GHz输出),36fs附加抖动(100Hz至fCLK)。

- 多通道输出:4路高频时钟(支持分频/倍频)及对应SYSREF输出,1路独立逻辑时钟(LOGICLK)。

- 灵活配置:支持SPI或引脚模式控制,可编程输出功率(8级)、延迟调整(508步进,步长<2.5ps@12.8GHz)。

2. 主要应用场景

- 雷达成像载荷

- 通信载荷时钟分配

- 数据转换器时钟生成(如JESD204B/C接口)

- 多设备同步系统

3. 核心功能模块

- 时钟处理

- 缓冲模式:直通输入时钟(0.3-15GHz)。

- 分频模式:支持÷2/3/4/5/7(非50%占空比的奇数分频)。

- 倍频模式:支持×2/3/4(集成PLL,需校准)。

- SYSREF生成

- 发生器模式:内部生成连续或脉冲同步信号。

- 中继模式:外部SYSREFREQ信号重定时输出。

- 窗口功能:优化SYSREFREQ与CLKIN的时序对齐。

- 逻辑时钟输出:独立可编程分频(÷1-1023),支持LVDS/CML格式。

4. 电气特性

- 工作电压:2.5V(2.4-2.6V范围)。

- 温度范围:-55°C至125°C。

- 关键性能:

- 输出功率:单端最高10dBm(15GHz)。

- 传播延迟:180ps(缓冲模式),温度漂移0.06ps/°C。

5. 封装与引脚

- 封装类型:64引脚HTQFP(10mm×10mm)。

- 关键引脚:

- CLKIN_P/N:差分时钟输入(50Ω内部终端)。

- CLKOUTx_P/N:差分时钟输出(开集电极,需AC耦合)。

- SYSREFOUTx_P/N:可编程共模电压(0.6-2V)。

6. 设计支持

- 寄存器配置:通过SPI接口控制功能模式、分频/倍频比、输出使能等。

- 开发工具:TI提供TICS Pro软件用于寄存器编程和性能仿真。

7. 典型应用示例

- 本地振荡器分配:配合LMX2615-SP生成6GHz时钟,附加抖动仅16fs(×2倍频模式)。

- JESD204B/C系统:多通道时钟分发至ADC/DAC,支持FPGA逻辑时钟同步。

文档结构

全文包含详细引脚定义、电气参数、时序图、寄存器映射(34个关键寄存器)及典型应用电路,适用于高可靠性航天与通信系统设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LMX2615 - SP:太空级宽带合成器的技术解析与应用指南2026-02-08 282

-

LMX2624-SP:高性能宽带频率合成器的深度剖析与设计指南2026-02-06 279

-

LMX2624-SP:高性能宽带频率合成器的深度解析2026-01-26 464

-

LMX2470芯片技术文档总结2025-09-22 860

-

LMX2486芯片技术文档总结2025-09-19 1002

-

LMX2485Q-Q1 芯片技术文档总结2025-09-15 1149

-

LMX2491 6.4-GHz低噪声RF PLL芯片技术文档总结2025-09-13 1547

-

LMX2615-SP 空间级宽带合成器技术文档总结2025-09-12 1017

-

LMX1404-EP 芯片技术文档总结2025-09-10 974

-

LMX1906-SP评估模块2024-11-14 317

-

LMX2615-SP 具有相位同步功且支持 JESD204B 的航空级 40MHz 至 15GHz 宽带合成器2018-08-03 1536

-

STM32调试SP3485技术总结2018-01-17 19748

全部0条评论

快来发表一下你的评论吧 !