LMK6x系列高性能BAW振荡器技术文档总结

描述

德州仪器 (TI) 的体声波 (BAW) 是一种微谐振器技术,可将高精度 BAW 谐振器直接集成到具有超低抖动时钟电路的封装中。BAW 与其他硅基制造工艺一样,完全在 TI 工厂设计和制造。

*附件:lmk6d.pdf

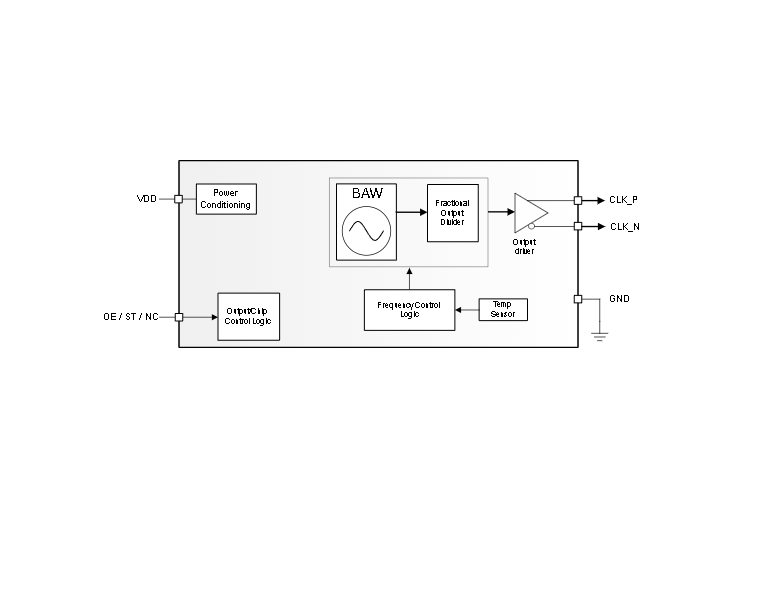

LMK6x 器件是一款超低抖动、固定频率振荡器,将 BAW 作为谐振器源。该器件在工厂根据特定工作模式进行编程,包括频率、电压、输出类型和功能引脚。LMK6x 采用高性能小数分频器,能够产生指定范围内的任何频率,为所有频率需求提供单一器件系列。

该器件具有高性能时钟、机械稳定性、灵活性和小封装选项,专为电信、数据和企业网络以及工业应用中使用的高速 SERDES 中的参考时钟和核心时钟而设计。

特性

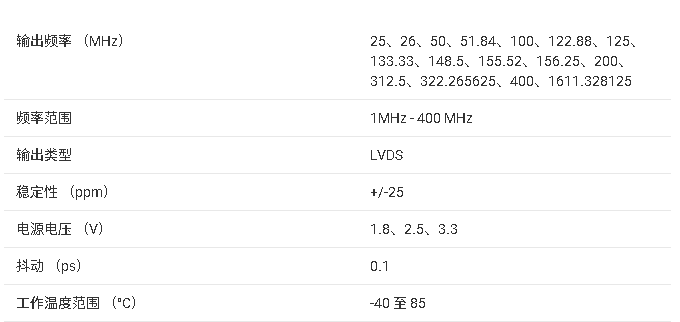

- 高性能差分和单端输出振荡器,支持以下范围内的任何固定频率:

- LMK6D:1MHz至400MHz,LVDS输出

- LMK6H:1MHz至400MHz,HCSL输出

- LMK6P:1MHz至400MHz,LVPECL输出

- LMK6C:1MHz至200MHz,LVCMOS输出

- 超低抖动:

- LMK6D/LMK6H/LMK6P:156.25MHz(12kHz至20MHz)时典型值为100fs/最大RMS抖动为125fs。

- LMK6C:100MHz(12kHz至20MHz)时典型值为350fs/最大RMS抖动为500fs。

- LMK6H:符合 PCIe Gen 1 至 Gen 7 标准

- ±25ppm 总频率稳定性,包括 10 年老化和所有其他因素

- 最小的行业标准 DLE 和 DLF 封装

- 支持扩展工业温度等级:

- LMK6P/LMK6D/LMK6H:–40°C 至 85°C

- LMK6C:–40°C 至 105°C

- 集成LDO,具有强大的电源抗噪性:

- 500kHz纹波时–72dBc PSRR

- 启动时间:< 5ms

- 标准频率:

- LVCMOS (MHz):1、2.04、4、8.192、10、12、12.288、16、19.2、20、23.5、24、24.57、25、25.6、26、26.21、27、28.12、32.768、33.333、40、48、49.15、50、54、60、65.53、66、74.25、76.8、80、100、108、125、133.330 和 156.25

- 差分 (MHz):25、26、32.5、50、51.84、54、65、76.8、80、100、108、122.88、125、133.330、148.35、148.5、150、155.52、156.25、161.1328125、200、312.5 和 400

- 设备可以支持 1MHz 至 400MHz 之间的任何频率。请联系 TI 代表了解所需的任何频率和样品

参数

方框图

1. 产品概述

LMK6x是德州仪器(TI)推出的基于体声波(BAW)技术的超低抖动固定频率振荡器系列,包含LMK6C(LVCMOS输出)、LMK6D(LVDS输出)、LMK6H(HCSL输出)和LMK6P(LVPECL输出)四种型号。其核心特点包括:

- 频率范围:1MHz至400MHz(差分型号)或1MHz至200MHz(LVCMOS型号)。

- 超低抖动性能:典型RMS抖动低至100fs(差分型号)和350fs(LVCMOS型号)。

- 高稳定性:总频率稳定性±25ppm(含10年老化及环境因素)。

- 小型封装:采用行业标准DLE(3.2mm×2.5mm)和DLF(2.5mm×2.0mm)封装。

2. 关键特性

- 输出类型:支持LVDS、HCSL、LVPECL差分输出及LVCMOS单端输出。

- 电源适应性:工作电压覆盖1.8V至3.3V,集成LDO实现-72dBc PSRR(500kHz纹波抑制)。

- 快速启动:启动时间<5ms。

- 工业级温度范围:-40°C至85°C(LMK6D/H/P)或-40°C至105°C(LMK6C)。

3. 应用领域

- 高速数据通信:56G/112G PAM4时钟、100G-800G光传输网络。

- 网络设备:交换机、路由器、基带单元(BBU)。

- PCIe时钟:兼容Gen1至Gen7标准。

- 工业与测试:FPGA/ASIC参考时钟、高性能晶振替代方案。

4. 技术亮点

- BAW谐振器技术:通过压电效应实现高Q值谐振,无需真空腔体,抗机械振动性能优异(灵敏度约2ppb/g)。

- 功能引脚配置:支持输出使能(OE)、待机(ST)或空接(NC)模式,可通过型号后缀区分功能。

5. 性能参数

- 相位噪声:典型值-156dBc/Hz(1MHz偏移,156.25MHz输出)。

- PCIe兼容性:Gen5 RMS抖动低至150fs,Gen7达67fs。

- 热设计:提供θJA、θJB等热阻参数,支持PCB散热优化。

6. 设计支持

- 推荐布局:提供评估模块(EVM)参考设计,强调电源去耦和信号完整性。

- 输出接口:详述差分/单端输出的匹配电路设计(如LVDS需100Ω端接,LVPECL需T/Y型网络)。

7. 文档结构

数据手册包含特性、应用、引脚定义、电气规格、时序图、典型曲线及封装信息,并附修订历史确保版本跟踪。

8. 订购信息

通过型号解码器选择频率、封装、电压/温度等级及功能引脚配置(如LMK6PA156.250ADLFR表示LVPECL输出、156.25MHz频率、DLE封装)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LMK62XX高性能低抖动振荡器:技术解析与应用指南2026-02-08 723

-

深入剖析LMK6x低抖动高性能BAW振荡器:性能、设计与应用全解析2026-02-06 211

-

LMK6C 低抖动、高性能、体声波 (BAW) 固定频率 LVCMOS 振荡器技术手册2025-09-11 1073

-

德州仪器LMK6x系列BAW振荡器技术解析2025-08-29 1340

-

适用于LMK6D、LMK6P和LMK6H BAW振荡器的通用焊盘图案2024-09-03 480

-

LMK6x低抖动高性能BAW振荡器数据表2024-08-20 444

全部0条评论

快来发表一下你的评论吧 !