CDCBT1001 1.2V至1.8V时钟缓冲器与电平转换器技术文档总结

描述

该CDCBT1001是1.2 V至1.8 V时钟缓冲器和电平转换器。VDD_IN引脚电源电压定义输入LVCMOS时钟电平。VDD_OUT引脚电源电压定义输出LVCMOS时钟电平。VDD_IN = 1.2 V ± 10%。VDD_OUT = 1.8 V ± 10%

24 MHz时的12 kHz至5 MHz附加RMS抖动小于0.8 ps。

*附件:cdcbt1001.pdf

特性

- 时钟频率范围:直流至24 MHz

- 1.2V 至 1.8V LVCMOS 时钟电平转换:

- VDD_IN = 1.2 V ± 10%

- VDD_OUT = 1.8 V ± 10%

- 低附加抖动和相位噪声:

- 0.8 ps最大12 kHz至5 MHz附加RMS抖动(f

外= 24 兆赫) - –120 dBc/Hz 在 1 kHz 偏移时的最大相位噪声 (f

外= 24 兆赫) - –148dBc/Hz 最大相位本底噪声 (f

外= 24 MHz,f抵消≥ 1 MHz)

- 0.8 ps最大12 kHz至5 MHz附加RMS抖动(f

- 5 ns 20% 至 80% 的上升/下降时间

- 10 ns 传播延迟

- 低电流消耗

- –40°C 至 85°C 工作温度范围

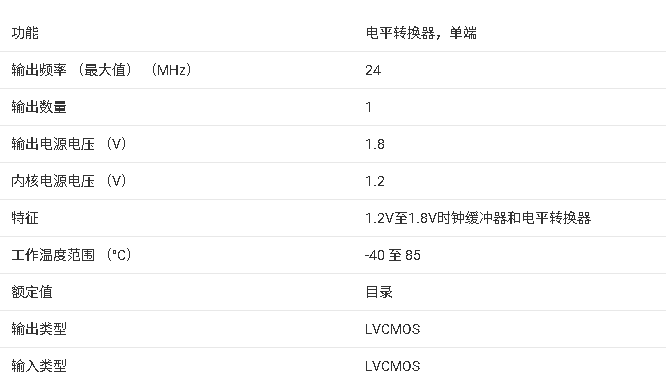

参数

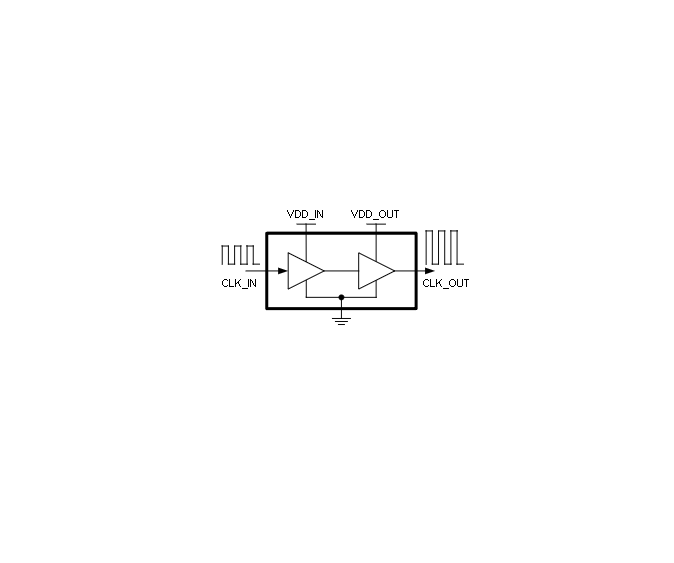

方框图

1. 核心功能

- 电平转换:支持1.2V(输入)至1.8V(输出)的LVCMOS时钟信号转换,输入/输出电压容差分别为±10%。

- 低抖动性能:12kHz至5MHz频段内最大附加RMS抖动仅0.8ps(24MHz输出时)。

- 低功耗:典型电流消耗35μA(12MHz)至60μA(24MHz)。

2. 关键参数

- 电气特性

- 工作频率范围:DC至24MHz

- 传播延迟:10ns

- 上升/下降时间:5ns(20%-80%)

- 相位噪声:≤-120dBc/Hz @1kHz偏移(24MHz输出)

- 工作条件

- 温度范围:-40°C至85°C

- 输入电压:1.08V-1.32V(VDD_IN)

- 输出电压:1.62V-1.98V(VDD_OUT)

3. 应用场景

- FPGA/处理器时钟缓冲与电平转换(消费电子)

- 服务器/扩展卡中的1.2V时钟信号处理

4. 封装与设计支持

- 封装:X2SON-5(0.8mm×0.8mm超小尺寸)

- 布局建议:

- 每个电源引脚需配置0.1μF去耦电容

- 缩短走线长度以减少负载影响

- 提供示例PCB布局图(图10-1)

5. 附加信息

- 版本历史:2022年5月首次发布

- 文档支持:包含热阻参数、ESD防护等级(HBM 2000V/CDM 1000V)及完整引脚功能说明

典型应用示例

- 处理器时钟升压转换:将1.2V处理器时钟信号转换为1.8V系统控制器兼容电平(图8-1),需满足输入摆幅≥850mVpp及边沿速率≥0.2V/ns。

注意:具体设计需参考完整数据手册的绝对最大额定值与测试条件,避免超出推荐工作范围。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IDT74SSTU32866B:1.8V可配置寄存器缓冲器的技术剖析2026-04-12 548

-

CDCBT1001:高性能时钟缓冲器与电平转换器的深度解析2026-02-06 1103

-

LMK00334四输出时钟缓冲器与电平转换器技术文档总结2025-09-15 1077

-

LMK00804B-Q1 1.5V至3.3V 1:4高性能LVCMOS扇出缓冲器与电平转换器技术文档总结2025-09-12 1145

-

CDCL6010 1.8V 11输出时钟乘法器、分配器、抖动消除器和缓冲器数据表2024-08-22 474

-

CDCBT1001 1.2V至1.8V时钟缓冲器和电平转换器数据表2024-08-20 457

-

配备电平转换器的 1.8V/3V SIM卡电源TXS4555数据表2024-05-23 540

-

8.5V到13.2V至1.2V/50A DC/DC转换器设计2022-09-06 692

-

DC1441A LTC3855EUJ演示板 | 双路输出, V = 4.5V 至 14V, V = 1.8V (17A), V = 1.2V (17A)2021-06-01 1058

-

LTC7851LTC4449项目-四路输出、多相降压模式DCDC控制器(7-14V至1.8V、1.2V和1V@30A)2021-05-29 886

-

LTC3546双输出转换器,在整个输出范围内具有高效率1.8V / 1A和1.2V / 3A输出2020-06-08 1413

-

1-Wire®双向电平转换器(1.8V至5V)参考设2010-02-05 2216

全部0条评论

快来发表一下你的评论吧 !