ISOW7721集成隔离电源与数字隔离器的技术解析与应用指南

描述

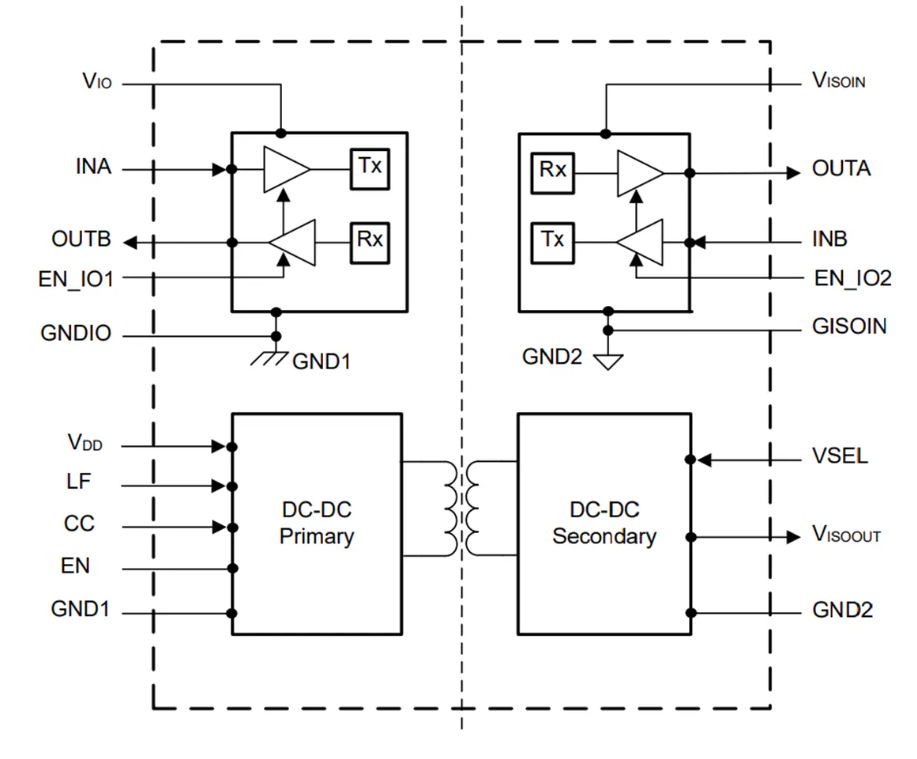

Texas Instruments ISOW7721两通道数字隔离器是一款电流隔离数字隔离器,集成了低排放高效功率转换器。集成的直流-直流转换器提供高达550mW隔离电源。该功能消除了在空间受限的隔离式设计中对单独的隔离式电源的需求。如果需要额外功率,Texas Instruments ISOW7721支持多器件链接,在系统中使用两个器件将集成功率输出提高到>1W。

数据手册:*附件:Texas Instruments ISOW7721两通道数字隔离器数据手册.pdf

特性

- 100Mbps数据速率

- 低排放、低噪声的集成式直流-直流转换器

- 辐射经过优化,符合CISPR 32和EN 55032 B类标准,在2层电路板上的裕度>5dB

- 25MHz的低频电源转换器可实现低噪声性能

- 低输出纹波:24mV

- 高效率输出功率

- 最大负载时的效率:46%

- 高达0.55W的输出功率

- V

ISOOUT精度:±5% - 最大可用负载电流:110mA(5V至5V时)

- 最大可用负载电流:140mA(5V至3.3V时)

- 最大可用负载电流:60mA(3.3V至3.3V时)

- 支持多ISOW7721链将系统功率输出提高到>1W和>200mA

- 用于通道隔离器和电源转换器的独立电源

- 逻辑电源 (V

IO):1.71V至5.5V - 电源转换器电源 (V

DD):3V至5.5V

- 逻辑电源 (V

- 稳健的电磁兼容性 (EMC)

- 系统级ESD、EFT和浪涌抗扰性

- ±8kV IEC 61000-4-2接触放电保护(整个隔离栅)

- 增强型和基础型隔离选项

- 高CMTI:100kV/µs(典型值)

- 安全相关认证(计划中)

- 符合DIN VDE V 0884-11:2017-01标准的VDE增强型和基础型绝缘

- UL 1577组件认证计划

- IEC 62368-1、IEC 61010-1、IEC 60601-1和GB 4943.1-2011认证

- 扩展温度范围:40°C至+125°C

- 20引脚宽体SOIC封装

简化示意图

ISOW7721集成隔离电源与数字隔离器的技术解析与应用指南

一、产品核心特性

ISOW7721是德州仪器推出的创新型集成器件,将两通道数字隔离器与高效DC-DC转换器整合在单芯片中。该器件采用20引脚宽体SOIC封装(12.83mm×7.5mm),具有以下突出特性:

隔离性能亮点:

- 强化隔离等级:通过VDE 0884-11认证,支持5000VRMS工作电压和7071VPK瞬态隔离电压

- 超高CMTI性能:典型值达100kV/μs,确保恶劣电磁环境下的稳定传输

- 双隔离屏障设计:信号通道采用SiO₂电容隔离,电源通道采用变压器磁隔离

电源转换特性:

- 宽输入范围:3V至5.5V(VDD),支持1.71V至5.5V逻辑电源(VIO)

- 可调输出:通过VSEL引脚选择3.3V或5V输出(精度±5%)

- 输出能力:最高提供550mW功率(5V输出时110mA,3.3V输出时140mA)

- 低纹波设计:典型输出纹波仅24mV(20MHz带宽)

数据传输性能:

- 高速传输:支持100Mbps数据速率

- 低传播延迟:5V供电时典型值7.6ns,最大值15.7ns

- 通道配置:1个正向通道(INA→OUTA)和1个反向通道(INB→OUTB)

二、创新架构设计

2.1 集成电源管理系统

器件采用创新的反馈控制架构,通过专用隔离通道实现次级电压监测。关键设计特点包括:

- 多级保护机制:集成过压锁定(OVLO)、欠压锁定(UVLO)和热关断(165°C触发)

- 软启动控制:典型启动时间1.9ms,有效抑制浪涌电流

- 多设备级联:支持最多8片并联,扩展输出能力至1W/200mA以上

2.2 信号传输技术

数据通道采用优化的OOK调制方案:

- 载波抑制技术:通过差分信号处理和屏蔽层设计降低辐射

- 失效保护设计:输入失电时自动进入预设状态(ISOW7721输出高,ISOW7721F输出低)

- 使能控制:通过EN_IOx引脚实现通道独立启停(响应时间<300ns)

三、关键设计规范

3.1 电源设计参数

| 参数 | 条件 | 最小值 | 典型值 | 最大值 |

|---|---|---|---|---|

| VDD UVLO阈值 | 上升沿 | 2.7V | 2.95V | - |

| VIO静态电流 | 100Mbps数据传输 | - | 11.6mA | 14.6mA |

| 转换效率 | VDD=5V, VISOOUT=5V满载 | - | 46% | - |

| 短路保护电流 | VISOOUT对GND2短路 | - | 250mA | - |

3.2 信号完整性要求

- 布局规范:

- 高频去耦电容(10nF)距引脚<1mm

- VDD/VISOOUT走线对称布置,长度匹配±5%

- 禁止在VISOOUT/GND2区域4mm内布置金属走线

- EMC设计:

- 辐射发射优化至CISPR 32 Class B余量>5dB

- 推荐使用四层板设计(信号-地-电源-信号)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电容隔离技术优势解析与乾鸿微全系列数字隔离器产品指南2026-01-23 328

-

ISOW7821:高性能数字隔离器的全方位解析2026-01-22 273

-

探究ISOW7721:双通道数字隔离器的全方位剖析2026-01-21 343

-

汽车级四通道数字隔离器ISOW774x-Q1:设计与应用全解析2026-01-20 1294

-

ISOW644x:高性能四通道数字隔离器的技术剖析与应用指南2026-01-19 372

-

ISOW7821 具有集成电源的双通道、1/1、增强型数字隔离器数据手册2025-03-04 1398

-

具有ISOW7841集成信号和功率隔离器的低辐射设计2024-09-26 507

-

ISOW7721具有集成式低辐射、低噪声直流/直流转换器的双通道数字隔离器数据表2024-08-19 461

-

全系列集成隔离电源的隔离器芯片2022-02-15 1919

全部0条评论

快来发表一下你的评论吧 !