SN74SSTUB32864 25位可配置寄存器缓冲器技术文档总结

描述

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC 工作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM 负载。在 1:2 引脚配置中,每个 DIMM 需要两个器件来驱动 18 个 SDRAM 负载。

所有输入均SSTL_18,但复位 (RESET) 和控制 (Cn) 输入除外,它们是 LVCMOS。所有输出均为边沿控制电路,针对未端接的DIMM负载进行了优化,并符合SSTL_18规格。

*附件:sn74sstub32864.pdf

SN74SSTUB32864采用差分时钟(CLK和CLK)工作。数据在 CLK 走高和 CLK 走低的交叉点上记录。

C0输入控制1:2引脚排列的引脚配置,从寄存器A配置(低电平时)到寄存器B配置(高电平时)。C1输入控制引脚配置,从25位1:1(低电平时)到14位1:2(高电平时)。正常运行期间不应切换 C0 和 C1。它们应硬连线到有效的低电平或高电平,以将寄存器配置为所需模式。在 25 位 1:1 引脚配置中,A6、D6 和 H6 端子被驱动为低电平,并且是不使用(DNU)引脚。

在DDR2 RDIMM应用中,RESET被指定为相对于CLK和CLK完全异步。因此,无法保证两者之间的时间关系。进入复位时,寄存器被清除,数据输出相对于禁用差分输入接收器所需的时间快速驱动为低电平。然而,当复位结束时,寄存器相对于使能差分输入接收器所需的时间迅速变为活动状态。只要数据输入为低电平,并且时钟在RESET从低到高转换到输入接收器完全使能期间保持稳定,SN74SSTUB32864的设计就可以确保输出保持低电平,从而确保输出上不会出现毛刺。

为确保在提供稳定时钟之前从寄存器获得定义的输出,在上电期间必须将RESET保持在低电平状态。

该器件支持低功耗待机作。当RESET为低电平时,差分输入接收器被禁用,未驱动(浮动)数据、时钟和基准电压(V 裁判 ) 输入。此外,当RESET为低电平时,所有寄存器都被复位,所有输出都强制为低电平,QERR除外。LVCMOS RESET和Cn输入必须始终保持在有效的逻辑高电平或低电平。

该器件还通过监控系统芯片选择(DCS 和 CSR)输入来支持低功耗有源作,并在 DCS 和 CSR 输入均为高电平时将 Qn 输出门控使其状态不变。如果DCS或CSR输入为低电平,则Qn输出正常工作。RESET输入优先于DCS和CSR控制,当驱动为低电平时,强制Qn输出为低电平。如果不需要DCS控制功能,则可以将CSR输入硬接线到地,在这种情况下,DCS的建立时间要求与其他D数据输入相同。要仅使用DCS控制低功耗模式,应将CSR输入上拉至VCC通过上拉电阻器。

两个V裁判引脚(A3 和 T3)在内部连接在一起大约 150 个。但是,需要只连接两个 V 中的一个裁判引脚连接到外部V裁判电源。未使用的 V裁判引脚应以 V 结尾裁判耦合电容器。

特性

- 德州仪器 (TI) Widebus+ ™ 系列成员

- 引脚排列优化了 DDR2 DIMM PCB 布局

- 可配置为 25 位 1:1 或 14 位 1:2 寄存器缓冲器

- 芯片选择输入可控制数据输出的状态变化,并最大限度地降低系统功耗

- 输出边沿控制电路可最大限度地降低未端接线路中的开关噪声

- 支持SSTL_18数据输入

- 差分时钟(CLK和CLK)输入

- 支持控制和RESET输入上的LVCMOS开关电平

- 支持工业温度范围(-40°C 至 85°C)

- 重置输入禁用差分输入接收器,复位所有寄存器,并强制所有输出为低电平

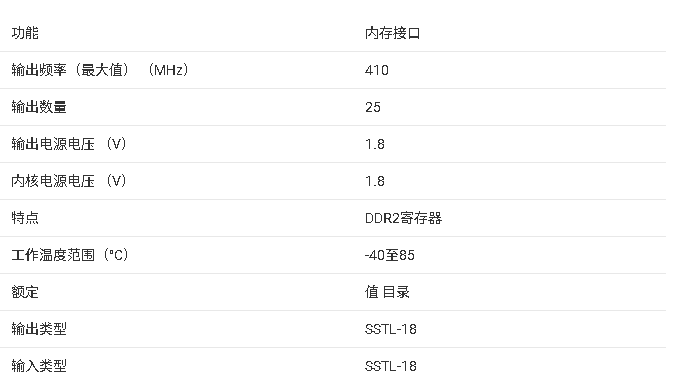

参数

1. 产品概述

- 型号:SN74SSTUB32864,隶属TI Widebus+™系列,专为DDR2 DIMM设计。

- 功能:支持25位1:1或14位1:2配置的寄存器缓冲模式,优化PCB布局,降低系统功耗。

- 工作电压:1.7V至1.9V VCC,工业级温度范围(-40°C至85°C)。

2. 关键特性

- 配置控制:通过C0/C1引脚选择工作模式(1:1或1:2),需硬接线避免运行时切换。

- 低功耗设计:

- 芯片选择(DCS/CSR)输入可禁用输出切换以节能。

- 异步复位(RESET)强制输出低电平并禁用差分接收器。

- 信号优化:边缘控制电路减少无端接线路的开关噪声,支持SSTL_18/LVCMOS输入电平。

3. 电气特性

- 时钟频率:最高410MHz,差分时钟(CLK/CLK)触发数据锁存。

- 时序要求:

- 建立/保持时间严格(如DCS需在CLK上升前600ps有效)。

- 复位后需保持输入稳定时间(tact/tinact)。

- 输出驱动:1.8V CMOS输出,支持SSTL_18规范,适应DIMM负载。

4. 封装与订购信息

- 封装:LFBGA-ZKE(96引脚),顶部标记“SB864”。

- 订购型号:SN74SSTUB32864ZKER(卷带包装)。

5. 应用注意事项

- 配置限制:1:1模式下A6/D6/H6引脚为DNU(禁用)。

- 复位优先级:RESET信号独立于时钟,确保上电时输出无毛刺。

- 热管理:热阻参数(RθJA/RθJB)提供散热设计参考。

-

74SSTUB32865A:28位到56位寄存器缓冲器的深度解析2026-04-18 67

-

探索ICSSSTUB32864A:DDR2的理想可配置缓冲器2026-04-14 367

-

深入解析Pericom PI74SSTU32864:25位1:1或14位1:2可配置寄存器缓冲器2026-03-27 186

-

探索SN74SSTEB32866:25位可配置寄存器缓冲器的卓越性能2026-02-09 239

-

SN74SSTU32864:25位可配置寄存器缓冲器的全面剖析2026-02-08 285

-

74SSTUB32868A:28位到56位寄存器缓冲器的技术剖析2025-12-29 682

-

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器2025-12-24 498

-

SN74SSTU32864 25位可配置寄存器缓冲器技术文档总结2025-09-12 839

-

SN74SSTU32864可配置寄存器缓冲器数据表2024-08-22 351

-

具备SSTL_18输入与输出的25 位可配置寄存缓冲器的特性及应用2009-10-28 2624

全部0条评论

快来发表一下你的评论吧 !