SN74SSTU32864 25位可配置寄存器缓冲器技术文档总结

描述

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC操作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM 负载。在 1:2 引脚配置中,每个 DIMM 需要两个器件来驱动 18 个 SDRAM 负载。

除LVCMOS复位(RESET)和LVCMOS控制(Cn)输入外,所有输入均为SSTL_18。所有输出均为边沿控制电路,针对未端接的DIMM负载进行了优化,并符合SSTL_18规格。

*附件:sn74sstu32864.pdf

SN74SSTU32864采用差分时钟(CLK和CLK)工作。数据在 CLK 走高和 CLK 走低的交叉点处记录。

C0输入控制1:2引脚排列的引脚配置,从寄存器A配置(低电平时)到寄存器B配置(高电平时)。C1输入控制引脚配置,从25位1:1(低电平时)到14位1:2(高电平时)。正常运行期间不应切换 C0 和 C1。它们应硬连线到有效的低电平或高电平,以将寄存器配置为所需模式。在 25 位 1:1 引脚配置中,A6、D6 和 H6 端子被驱动为低电平,不应使用。

该器件支持低功耗待机作。当RESET为低电平时,差分输入接收器被禁用,未驱动(浮动)数据、时钟和基准电压(V 裁判 ) 输入。此外,当RESET为低电平时,所有寄存器都复位,所有输出都强制为低电平。LVCMOS RESET和Cn输入必须始终保持在有效的逻辑高电平或低电平。

两个V裁判引脚(A3 和 T3)在内部连接在一起大约 150 个。但是,只需连接两个 V 中的一个裁判引脚连接到外部V裁判电源。未使用的 V裁判引脚应以 V 结尾裁判耦合电容器。

该器件还通过监控系统芯片选择(DCS 和 CSR)输入来支持低功耗有源作,并将在 DCS 和 CSR 输入都为高电平时控制 Qn 输出的状态变化。如果 DCS 或 CSR 输入为低电平,则 Qn 输出正常工作。RESET输入优先于DCS和CSR控制,并强制输出为低电平。如果不需要DCS控制功能,则可以将CSR输入硬接线到地,在这种情况下,DCS的建立时间要求与其他D数据输入相同。

为确保在提供稳定时钟之前从寄存器获得定义的输出,RESET在上电期间必须保持低电平状态。

特性

- 德州仪器 (TI) Widebus+ ™ 系列成员

- 引脚排列优化了 DDR-II DIMM PCB 布局

- 可配置为 25 位 1:1 或 14 位 1:2 寄存器缓冲器

- 芯片选择输入可控制数据输出的状态变化,并最大限度地降低系统功耗

- 输出边沿控制电路可最大限度地降低未端接线路中的开关噪声

- 支持SSTL_18数据输入

- 差分时钟(CLK和CLK)输入

- 支持控制和RESET输入上的LVCMOS开关电平

- RESET输入禁用差分输入接收器,复位所有寄存器,并强制所有输出为低电平

- 闩锁性能超过 100 mA,符合 JESD 78,II 类标准

- ESD 保护超过 JESD 22

- 5000V 人体模型 (A114-A)

- 200V 机器型号 (A115-A)

- 1000V 充电设备型号 (C101)

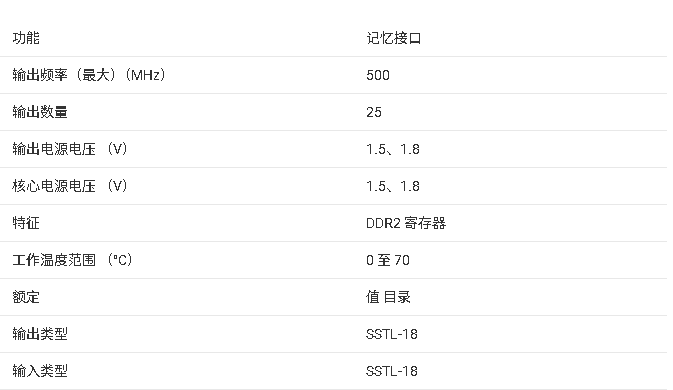

参数

1. 产品概述

SN74SSTU32864是德州仪器(TI)Widebus+系列成员,专为DDR-II DIMM PCB布局优化设计的25位可配置寄存器缓冲器,支持SSTL_18输入/输出。关键特性包括:

- 配置模式:可设置为25位1:1或14位1:2寄存器缓冲器,通过控制引脚(C0、C1)选择。

- 低功耗设计:芯片选择输入(DCS/CSR)可禁用数据输出切换以降低系统功耗,RESET引脚可强制所有输出低电平并禁用差分接收器。

- 抗噪设计:输出边缘控制电路减少未端接线路的开关噪声。

2. 电气特性

- 工作电压:1.7V至1.9V VCC,参考电压(VREF)为0.9V。

- 输入/输出标准:数据输入为SSTL_18(除LVCMOS控制的RESET和Cn引脚),输出满足SSTL_18规范。

- ESD保护:符合JESD 22标准(人体模型5000V,机器模型200V,充电设备模型1000V)。

3. 功能配置

- 引脚分配:提供三种终端分配模式(1:1寄存器、1:2寄存器A/B),具体由C0和C1控制。

- 控制逻辑:

- RESET低电平时禁用差分接收器并复位寄存器。

- DCS和CSR同时高电平时冻结输出状态。

4. 时序与性能

- 时钟频率:最高500MHz,差分时钟(CLK/CLK)触发数据锁存。

- 传播延迟:典型值1.4ns(VCC=1.8V±0.1V)。

- 输出压摆率:1.9V/ns至4.9V/ns(上升/下降沿)。

5. 封装与订购信息

- 封装类型:LFBGA-GKE(96引脚),尺寸13.6mm×13.4mm。

- 订购型号:SN74SSTU32864GKER(0°C至70°C工作温度)。

6. 应用场景

适用于需驱动多SDRAM负载的DDR-II内存模块设计,单设备可驱动9个负载(1:1模式),双设备驱动18个负载(1:2模式)。

7. 注意事项

- C0/C1需硬接线至固定电平,正常运行时不可切换。

- 未使用的VREF引脚需接耦合电容。

- 上电时需保持RESET低电平以确保输出定义明确。

-

74SSTUB32864A:25位可配置寄存器缓冲器的深度解析2026-04-18 51

-

IDT74SSTU32864/A/C/D/G:1.8V SSTL I/O的1:1与1:2寄存器缓冲器2026-04-12 403

-

深入解析Pericom PI74SSTU32864:25位1:1或14位1:2可配置寄存器缓冲器2026-03-27 186

-

探索SN74SSTEB32866:25位可配置寄存器缓冲器的卓越性能2026-02-09 241

-

SN74SSTU32864:25位可配置寄存器缓冲器的全面剖析2026-02-08 285

-

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器2025-12-24 499

-

SN74SSTUB32864 25位可配置寄存器缓冲器技术文档总结2025-09-12 933

-

SN74SSTU32864可配置寄存器缓冲器数据表2024-08-22 351

-

具备SSTL_18输入与输出的25 位可配置寄存缓冲器的特性及应用2009-10-28 2624

全部0条评论

快来发表一下你的评论吧 !