CDCU2A877 1.8-V相位锁定环时钟驱动器技术文档总结

描述

该CDCU2A877是一款高性能、低抖动、低偏斜、零延迟缓冲器,可将差分时钟输入对(CK、CK)分配给10个差分时钟输出对(Yn、Yn)和1个差分反馈时钟输出对(FBOUT、FBOUT)。时钟输出由输入时钟(CK、CK)、反馈时钟(FBIN、FBIN)、LVCMOS控制引脚(OE、OS)和模拟电源输入(AV DD ).当OE为低电平时,除FBOUT/FBOUT外,时钟输出被禁用,而内部PLL继续保持其锁定频率。OS(输出选择)是必须连接到 GND 或 V 的程序引脚 DD .当作系统为高电平时,OE 功能如前所述。当OS和OE都较低时,OE对Y7/Y7没有影响,它们是自由运行的。当 AVDD接地时,PLL 被关闭并旁路用于测试目的。

*附件:cdcu2a877.pdf

当两个时钟输入(CK、CK)逻辑低电平时,器件进入低功耗模式。差分输入上的输入逻辑检测电路独立于输入缓冲器,检测逻辑低电平,并在所有输出、反馈和PLL关闭的低功耗状态下运行。当时钟输入从逻辑低电平转换为差分信号时,PLL重新导通,输入和输出使能,PLL在规定的稳定时间内获得反馈时钟对(FBIN、FBIN)和时钟输入对(CK、CK)之间的锁相。

该CDCU2A877能够跟踪扩频时钟 (SSC) 以降低 EMI。该器件的工作温度范围为 0°C 至 70°C。

特性

- 1.8V/1.9V 锁相环时钟驱动器,适用于双倍数据速率 (DDR II) 应用

- 兼容扩频时钟

- 工作频率:125 MHz 至 410 MHz

- 应用频率:160 MHz 至 410 MHz

- 低抖动(周期间):±40 ps

- 低输出偏斜:35 ps

- 稳定时间 <6 μs

- 将一个差分时钟输入分配给10个差分输出

- CDCUA877的高驱动版本

- 52 球 mBGA(MicroStar Junior™;BGA,0.65 毫米间距)

- 外部反馈引脚(FBIN、FBIN)用于将输出同步到输入时钟

- 达到或超过PC2-3200/4300/5300/6400的CUA877/CUA878规范PLL标准

- 故障安全输入

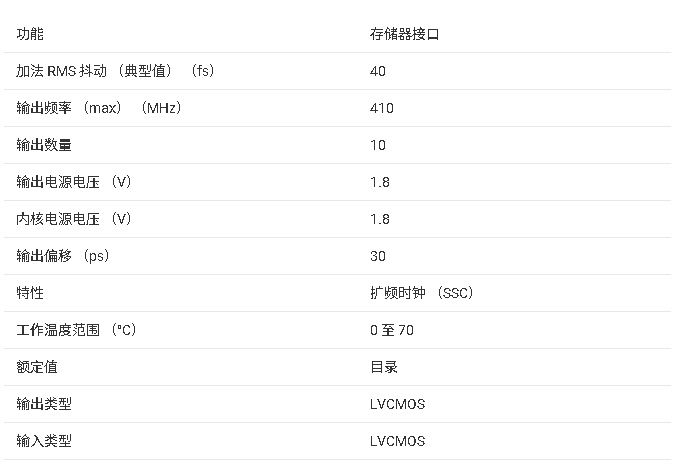

参数

1. 产品概述

CDCU2A877是德州仪器(TI)设计的高性能、低抖动、低偏斜的零延迟缓冲器,专为DDR II内存应用优化。核心功能是将一对差分时钟输入(CK/CK)分配至10对差分时钟输出(Yn/Yn)及1对反馈时钟输出(FBOUT/FBOUT),支持1.8V/1.9V工作电压,适用于PC2-3200/4300/5300/6400规范。

2. 关键特性

- 频率范围:操作频率125–410 MHz,应用频率160–410 MHz

- 低抖动性能:周期抖动±40 ps,输出偏斜仅35 ps

- 快速锁定:稳定时间<6 μs,支持扩频时钟(SSC)以降低EMI

- 节能模式:输入时钟为低电平时自动进入低功耗状态

- 封装:52球mBGA(0.65mm间距,MicroStar Junior™ BGA)

3. 功能控制

- OE(输出使能) :低电平时禁用输出(FBOUT除外),PLL保持锁定

- OS(输出选择) :接地或接VDD可配置Y7/Y7为自由运行模式

- 反馈同步:通过FBIN/FBIN引脚实现输入与输出的相位同步

4. 电气参数

- 工作条件:电压1.7–1.9V,温度0–70°C

- 绝对最大额定值:电源电压-0.5至2.5V,输入/输出电压-0.5至VDDQ+0.5V

- 时序要求:静态相位偏移±50 ps,动态相位偏移±30 ps

5. 应用设计

- 推荐电路:需在AVDD引脚附近放置2200pF电容,采用宽走线连接模拟电源/地

- 测试负载:输出需匹配2pF容抗与120Ω终端电阻

6. 封装与订购信息

- 型号示例:CDCU2A877ZQL(工业温度级)

- 包装选项:1000片大卷带(NMK封装)或250片小卷带

-

深入解析 ICS98ULPA877A:低功耗宽范围频率时钟驱动器2026-02-28 200

-

TI CDCU877和CDCU877A:高性能1.8V锁相环时钟驱动器深度解析2026-02-10 678

-

TI CDCU2A877:高性能DDR II时钟驱动器的卓越之选2026-02-08 315

-

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结2025-10-08 892

-

CDC2536 锁相环时钟驱动器技术文档总结2025-09-24 1017

-

CDC509 3.3V相位锁定环时钟驱动器技术文档总结2025-09-23 1118

-

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结2025-09-22 604

-

CDCU877/CDCU877A 1.8V锁相环时钟驱动器技术文档总结2025-09-19 1112

-

CDCV857A 2.5V锁相环时钟驱动器数据表2024-08-22 580

-

CDCU2A877锁相环时钟驱动器数据表2024-08-21 655

全部0条评论

快来发表一下你的评论吧 !