LMK05318B 带BAW的超低抖动单通道网络同步器时钟技术手册

描述

该LMK05318B是高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

该器件可以使用 TI 专有的体声波 (BAW) VCO 技术生成具有 50 fs RMS 抖动的输出时钟,与 XO 和基准输入的抖动和频率无关。

*附件:lmk05318b.pdf

特性

- 一个数字锁相环 (DPLL),具有:

- 无中断开关:±50ps 相位瞬变

- 带 Fastlock 的可编程环路带宽

- 使用低成本 TCXO/OCXO 实现符合标准的同步和保持

- 两个模拟锁相环 (APLL),具有行业领先的抖动性能:

- 312.5 MHz时的50 fs RMS抖动(APLL1)

- 155.52 MHz时的125fs RMS抖动(APLL2)

- 两个参考时钟输入

- 基于优先级的输入选择

- 失去参考的数字滞留

- 8个时钟输出,带可编程驱动器

- 多达六种不同的输出频率

- AC-LVDS、AC-CML、AC-LVPECL、HCSL和1.8V LVCMOS输出格式

- EEPROM / ROM,用于上电时自定义时钟

- 灵活的配置选项

- 输入和输出 1 Hz (1 PPS) 至 800 MHz

- XO/TCXO/OCXO 输入:10 至 100 MHz

- DCO 模式:< 0.001 ppb/步,用于精确时钟控制(IEEE 1588 PTP 从机)

- 高级时钟监控和状态

- 我^2^C 或 SPI 接口

- PSNR:–83 dBc(3.3V电源时噪声为50 mVpp)

- 3.3V电源,1.8V、2.5V或3.3V输出

- 工业温度范围:–40 °C 至 +85 °C

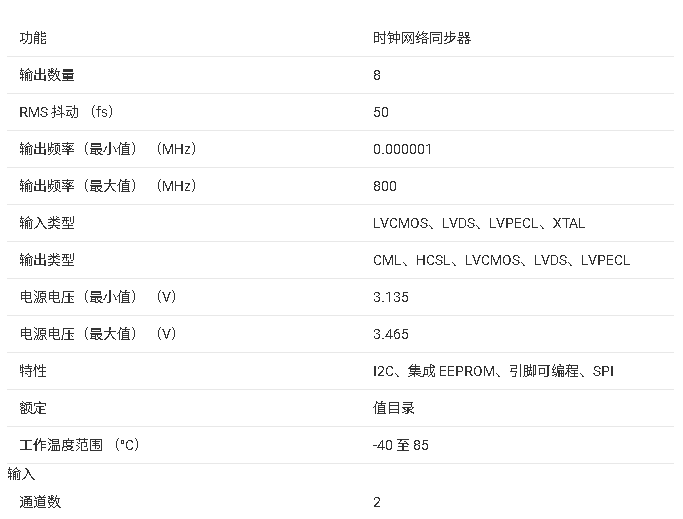

参数

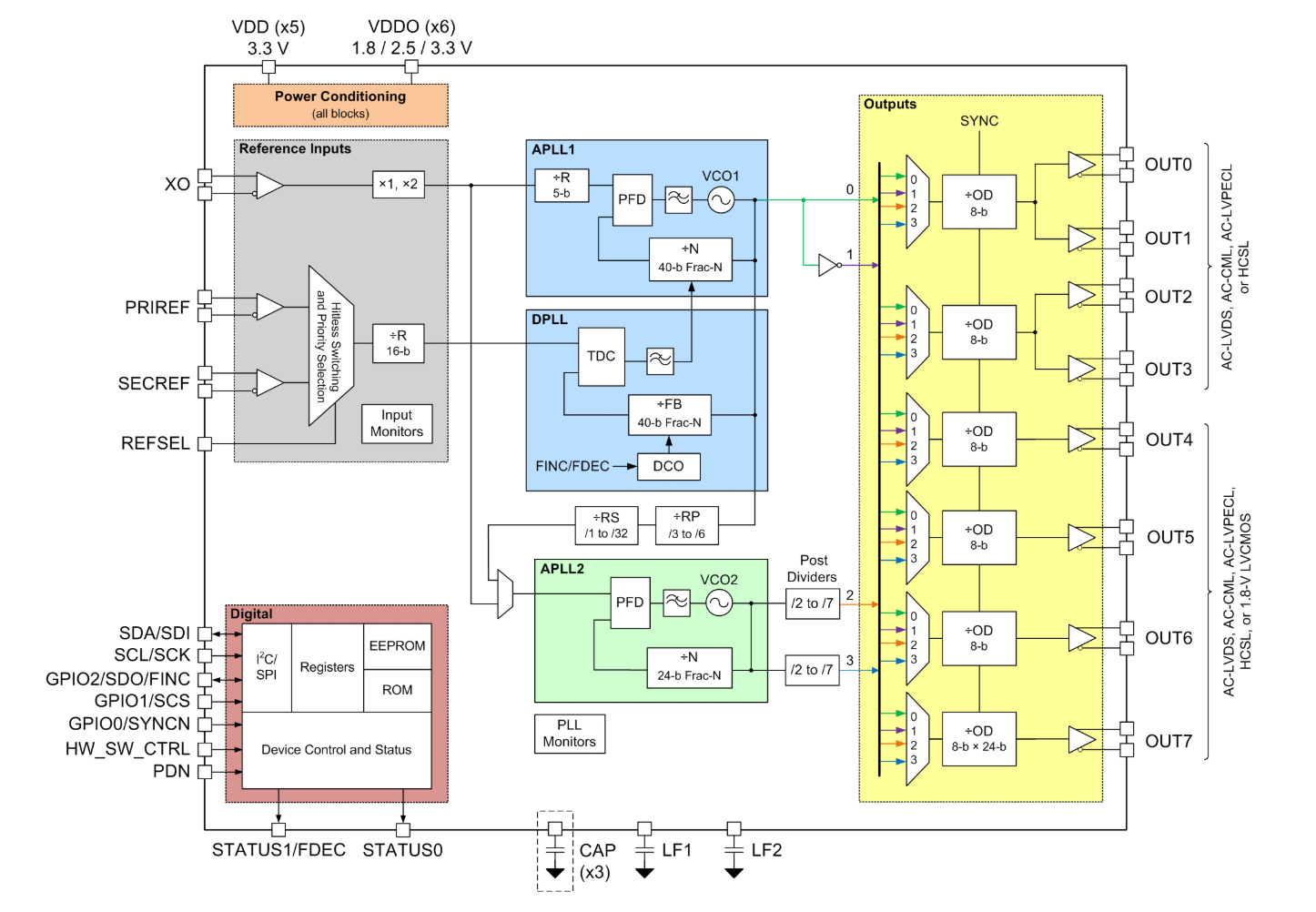

方框图

1. 核心特性

- 双锁相环架构:

- 数字锁相环(DPLL) :支持±50ps相位瞬态的无缝切换、可编程环路带宽、符合标准的同步与保持功能(需搭配低成本TCXO/OCXO)。

- 模拟锁相环(APLL) :

- APLL1:312.5MHz下仅50fs RMS抖动(行业领先)。

- APLL2:155.52MHz下125fs RMS抖动。

- 输入/输出配置:

- 2路参考时钟输入,支持优先级切换与数字保持功能。

- 8路可编程时钟输出,支持AC-LVDS/CML/LVPECL、HCSL及1.8V LVCMOS格式,最高支持6种不同频率。

- 配置灵活性:

- 通过EEPROM/ROM实现上电自定义配置,支持I²C/SPI接口编程。

- 输入/输出频率范围:1Hz至800MHz,XO输入支持10-100MHz。

2. 关键性能参数

- 抖动性能:

- APLL1输出312.5MHz时抖动低至50fs RMS,APLL2输出155.52MHz时为125fs RMS。

- 电源噪声抑制(PSNR):-83dBc(50mVpp噪声下)。

- 工作条件:

- 工业级温度范围:-40°C至+85°C。

- 供电电压:核心3.3V,输出可选1.8V/2.5V/3.3V。

3. 应用场景

- 通信基础设施:SyncE、SONET/SDH、IEEE 1588 PTP从时钟、光传输网络。

- 高速数据链路:400G线卡、以太网交换机和路由器的架构板卡。

- 无线与测试设备:基站(BTS)、回传设备、测试测量及医疗成像。

4. 功能描述

- 网络同步器:集成抖动清除、时钟生成及高级监控功能,支持BAW VCO技术实现独立于输入抖动的超低抖动输出。

- 同步模式:支持无缝切换、数字保持及DCO模式(频率步进<0.001ppb),适用于精密时钟校准。

- 参考监控:内置输入故障检测模块,最小化参考时钟丢失时的输出扰动。

5. 封装与版本

- 封装:48引脚VQFN(7mm×7mm)。

- 版本更新:2021年6月修订版优化了抖动性能(如APLL2在155.52MHz下从130fs降至125fs)并扩展了输出频率上限至1250MHz。

6. 设计支持

- 提供详细的布局指南、热管理建议及典型应用电路(如电源去耦、PCB层叠设计)。

- 支持TICS Pro软件配置DPLL带宽,确保闭环抖动峰值≤0.1dB。

附件说明

本文档为TI(德州仪器)LMK05318B时钟发生器数据手册的核心内容摘要,完整技术细节需参考原文档中的图表(如相位噪声曲线、PSNR测试配置)及寄存器配置说明。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索LMK05318B:以太网网络同步的卓越之选2026-02-08 269

-

LMK5B12212网络同步器:以太网网络应用的高性能解决方案2026-02-06 304

-

LMK05318 带BAW的超低抖动单通道网络同步器时钟技术手册2025-09-12 1036

-

LMK05318B-Q1 芯片技术文档总结2025-09-10 1065

-

LMK05318B EVM用户指南2024-12-06 444

-

LMK05318具有两个频域的超低抖动网络同步器时钟数据表2024-08-23 434

-

LMK05318B超低抖动时钟发生器数据表2024-08-21 460

-

BAW谐振器技术的优势2021-01-25 2751

全部0条评论

快来发表一下你的评论吧 !