LMK00804B-Q1 1.5V至3.3V 1:4高性能LVCMOS扇出缓冲器与电平转换器技术文档总结

描述

LMK00804B-Q1是一款高性能时钟扇出缓冲器和电平转换器,可从两个可选择输入之一分配多达四个LVCMOS/LVTTL输出(3.3V、2.5V、1.8V或1.5V电平),这些输入可以接受差分或单端输入。时钟使能输入在内部同步,以消除时钟使能端子置位或取消置位时输出上的欠幅或毛刺脉冲。当时钟被禁用时,输出保持在逻辑低电平状态。LMK00804B-Q1 还可以在四个收发器上分配低抖动时钟,并可以提高级联毫米波雷达系统中的整体目标检测和分辨率。

*附件:lmk00804b-q1.pdf

特性

- AEC-Q100 符合以下标准:

- 器件温度等级 1:–40°C 至 +125°C,T

一个

- 器件温度等级 1:–40°C 至 +125°C,T

- 四个LVCMOS/LVTTL输出,支持1.5V至3.3V电平

- 附加抖动:40 MHz时为0.1 ps RMS(典型值)

- 本底噪声:40 MHz时–168 dBc/Hz(典型值)

- 输出频率:350 MHz(最大值)

- 输出偏斜:35 ps(最大)

- 零件间偏斜:550 ps(最大)

- 两个可选输入

- CLK_P,CLK_N对接受 LVPECL、LVDS、HCSL、SSTL、LVHSTL 或 LVCMOS/LVTTL

- LVCMOS_CLK接受LVCMOS/LVTTL

- 同步时钟使能

- 核心/输出电源:

- 3.3 伏/3.3 伏

- 3.3 伏/2.5 伏

- 3.3 伏/1.8 伏

- 3.3 伏/1.5 伏

- 封装:16引脚VQFN

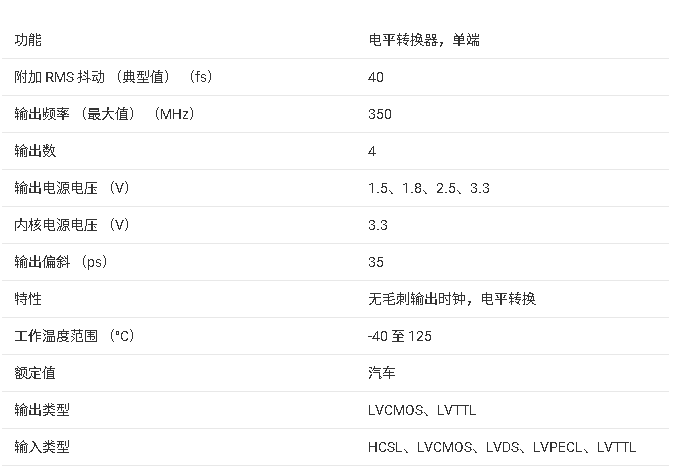

参数

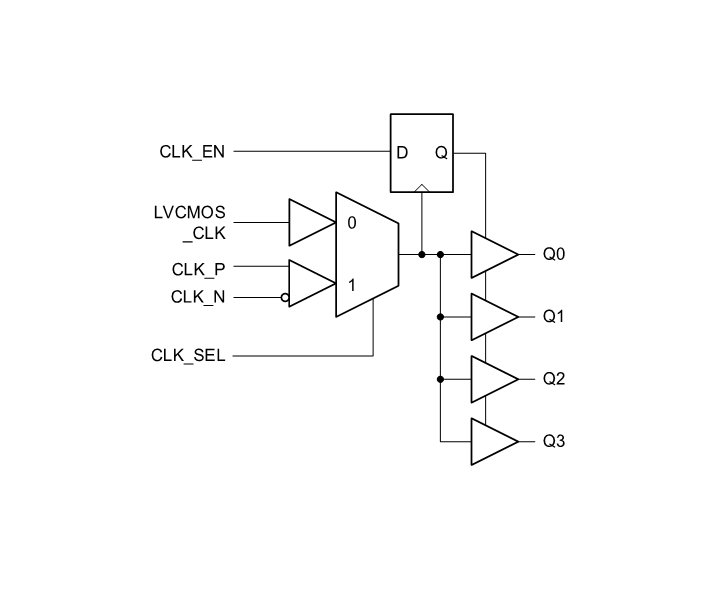

方框图

1. 核心特性

- AEC-Q100认证:支持-40°C至+125°C工作温度(车规级)。

- 多电压输出:4路LVCMOS/LVTTL输出,支持1.5V至3.3V电平,最大输出频率350 MHz。

- 低抖动与噪声:典型附加抖动0.1 ps RMS(40 MHz),噪声底噪-168 dBc/Hz。

- 双输入选择:支持差分输入(LVPECL/LVDS/HCSL等)或单端LVCMOS输入,通过CLK_SEL引脚切换。

- 同步时钟使能:CLK_EN引脚可同步启停输出,避免毛刺。

- 电源灵活性:支持3.3V核心供电,输出电源可独立配置(3.3V/2.5V/1.8V/1.5V)。

2. 关键参数

- 时序性能:传播延迟310 ns(LVCMOS输入)、115 ns(差分输入),输出偏斜≤35 ps。

- 功耗:静态电流21 mA(VDD)、5 mA(VDDO),动态功耗与负载电容相关。

- 封装:16引脚VQFN(3mm×3mm),带裸露焊盘增强散热。

3. 典型应用

- 汽车雷达系统:如ADAS中的前向长距/中短距雷达。

- 时钟分配:为多收发器提供低抖动时钟,提升毫米波雷达系统分辨率。

4. 设计要点

- 布局建议:

- 使用多层板与密集地过孔降低阻抗。

- 输入/输出端靠近放置匹配电阻(如43Ω串联终端)。

- 差分输入推荐高摆率(>3 V/ns)以优化抖动性能。

- 电源滤波:每电源引脚配置0.1μF去耦电容,建议添加铁氧体磁珠隔离高频噪声。

- 热管理:最大结温125°C,需通过PCB散热设计控制温升。

5. 修订历史

- 关键变更:部件间偏斜从700 ps降至550 ps,优化了热管理布局指南,增强ESD防护(CDM等级提升至±750V)。

6. 文档支持

- 包含完整引脚定义、电气特性、典型应用电路及封装尺寸图,参考设计文件(如SCAA082高速布局指南)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析LMK00105:超低抖动LVCMOS扇出缓冲器与电平转换器2026-02-09 310

-

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器2026-02-08 304

-

探索LMK1C110xA:高性能LVCMOS时钟缓冲器的理想选择2026-02-06 326

-

LMK00105 超低抖动LVCMOS扇出缓冲器与电平转换器技术文档总结2025-09-15 1167

-

LMK00804B 低偏斜1:4多路复用差分/LVCMOS至LVCMOS/TTL扇出缓冲器技术文档总结2025-09-14 1230

-

LMK00804B低偏移1到4多路复用差动/LVCMOS到LVCMOS/TTL扇出缓冲器数据表2024-08-23 511

-

LMK00804B-Q1 1.5V至3.3V、1路至4路高性能LVCMOS扇出缓冲器和电平转换器数据表2024-08-22 462

-

LMK1C110x 1.8V、2.5V和3.3V LVCMOS时钟缓冲器系列数据表2024-08-20 590

全部0条评论

快来发表一下你的评论吧 !