TPS7A15超低压差LDO稳压器技术解析与应用指南

描述

Texas Instruments TPS7A15 LDO稳压器提供出色的瞬态响应和400mA拉电流,具有出色的交流性能(负载和线路瞬态响应)。该器件具有0.7V至2.2V输入电压范围和0.5V至2.05V输出范围,在整个负载、线路和温度范围内具有非常高的精度(1%)。

数据手册:*附件:Texas Instruments TPS7A15 LDO稳压器数据手册.pdf

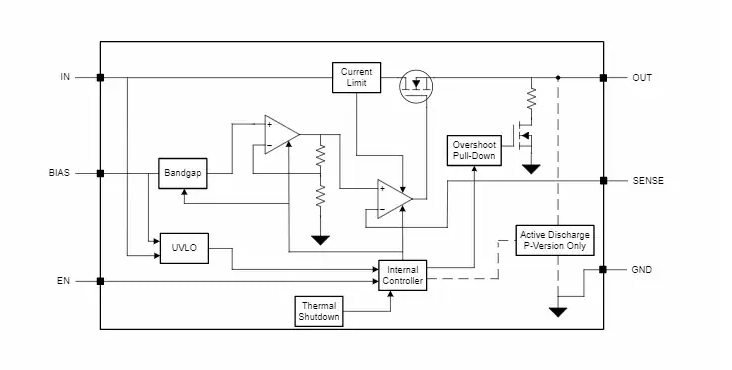

该器件的主电源路径通过IN引脚,可连接至电压至少高于输出电压50mV的电源。所有电气特性(包括出色的输出电压容差、瞬态响应和PSRR)均针对输入电压(比输出电压高100mV)进行规定,可实现高效率。TPS7A15使用一个为LDO内部电路供电的外部较高VBIAS电压轨,支持很低的输入电压。

TPS7A15配备了一个有源下拉电路,用于在输出处于禁用状态时使其快速放电,并提供已知的启动状态

TPS7A15采用超小型0.71mm × 1.0mm 、6凸点DSBGA封装,设计用于空间受限的应用。

特性

- 超低输入电压范围:0.7V至2.2V

- 高效率:

- 压差:80mV(最大值,400mA时)

- 额定V

IN= VOUT+ 100 mV

- 出色的负载瞬态响应(20mV,I

LOAD1mA至250mA,10μs) - +1%,–1.1%精度(负载、线路、温度)

- 高PSRR:84dB(1kHz时)

- 提供固定输出电压:0.5V至2.05V(阶跃25mV)

- V

BIAS范围:2.2V至5.5V - 6引脚、1mm x 0.71 mm DSBGA封装

- 有源输出放电

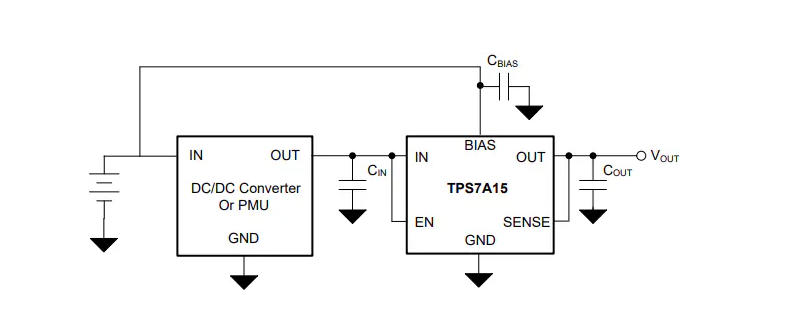

典型应用电路

框图

TPS7A15超低压差LDO稳压器技术解析与应用指南

一、产品概述

TPS7A15是德州仪器(TI)推出的一款超低输入电压、超低压差的线性稳压器(LDO),具有以下突出特性:

- 超宽输入范围:0.7V至2.2V工作电压

- 超低压差:400mA负载时仅80mV(最大值)

- 超高精度:全温度范围内±1.1%输出精度

- 双电源架构:支持VBIAS(2.2-5.5V)辅助供电

- 微型封装:提供1mm×0.71mm WCSP和2mm×2mm WSON封装

典型应用场景:

- 智能穿戴设备(手表/耳机)

- 手机/平板相机模块

- 便携式医疗设备

- SSD固态硬盘供电

二、关键技术创新

2.1 双电源架构设计

TPS7A15采用创新的双电源架构:

- 主电源路径(IN引脚):支持低至VOUT+50mV的输入电压

- 偏置电源(BIAS引脚):为内部电路提供独立供电

- 优势:主路径可采用高效DC/DC输出,BIAS接电池,实现最佳能效

2.2 超低压差性能

在400mA负载时:

- VIN压差:典型值31mV(最大值80mV)

- VBIAS压差:典型值1V(最大值1.3V)

- 效率优势:VIN仅需比VOUT高100mV即可维持全性能

2.3 动态响应优化

- 负载瞬态响应:1mA→250mA阶跃仅20mV波动

- PSRR性能:

- 1kHz时84dB(3mA负载)

- 1MHz时仍保持65dB

- 快速启动:EN使能至95%VOUT仅需200μs

三、引脚功能详解

6引脚配置(WCSP/WSON封装) :

| 引脚 | 名称 | 功能描述 |

|---|---|---|

| OUT | 输出 | 需接≥1μF陶瓷电容(推荐2.2μF),布局时尽量靠近引脚 |

| IN | 输入 | 需接≥0.75μF陶瓷电容,建议使用2.2μF以上电容优化瞬态响应 |

| SENSE | 检测 | 连接至负载端可消除走线电阻导致的压降误差 |

| EN | 使能 | 高电平有效(≥0.6V),不用时可接IN或BIAS |

| GND | 地 | 必须良好接地,WSON封装的热焊盘需连接至地平面 |

| BIAS | 偏置 | 建议接0.1μF陶瓷电容,布局时尽量靠近引脚 |

四、典型应用设计

4.1 电源方案设计

推荐参数:

- 输入电容(CIN):≥2.2μF X7R/X5R陶瓷电容

- 输出电容(COUT):≥2.2μF 低ESR陶瓷电容

- 偏置电容(CBIAS):0.1μF陶瓷电容

- PCB布局:所有去耦电容需在3mm范围内

4.3 保护功能配置

- 电流限制:450-1100mA可折返式保护

- 热关断:165°C触发,140°C恢复

- 主动放电:EN禁用时36Ω下拉电阻(仅P版本)

- UVLO保护:

- VIN欠压锁定:584-623mV(上升/下降)

- VBIAS欠压锁定:1.15-1.7V(上升/下降)

五、设计注意事项

- 压差模式操作:

- 当VIN < VOUT + VDO时进入压差模式

- 此时PSRR和瞬态性能会下降

- 恢复时可能出现输出电压过冲

- 启动时序要求:

- VIN/VBIAS/EN可任意顺序上电

- 建议EN最后使能以优化启动特性

- 布局指南:

- 采用完整地平面

- 关键信号远离高频干扰源

- WSON封装需充分利用热焊盘

- 电容选择:

- 避免使用Y5V材质电容

- 实际有效容量按标称值50%计算

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

超低压差稳压器TPS7A14的技术解析与应用指南2025-09-25 889

-

德州仪器TPS7A13超低压差稳压器技术解析与应用指南2025-09-12 815

-

TPS7A53A-Q1超低压差稳压器的技术解析与应用指南2025-08-27 1179

-

Texas Instruments TPS7A53B超低压降 (LDO) 稳压器数据手册2025-08-03 1566

-

Texas Instruments TPS7N53超低压差(LDO)线性稳压器数据手册2025-07-11 952

-

TPS7A15 400mA、低输入和输出电压、超低压差 (LDO) 稳压器数据手册2025-02-27 1288

-

TPS7A94低噪声、低压差(LDO)稳压器手册2024-11-18 806

-

TPS7A20超小型低压差(LDO)线性稳压器手册2024-11-15 861

-

1.5V至7V输入3A耐辐射 、超低压差 (LDO) 稳压器TPS7H1101-SP数据表2024-04-03 623

-

TPS7A15 400mA 低输入电压、低输出电压、超低压差稳压器数据表2024-02-28 495

-

用于LT1431超低压差稳压器的简单超低压差稳压器2019-06-12 1969

-

AZ2940 1A超低压差线性稳压器的典型应用2019-04-24 2867

-

奥地利微电子推出400mA低输入电压、超低压差稳压器2009-11-12 1074

-

超低压差稳压技术2009-07-10 3366

全部0条评论

快来发表一下你的评论吧 !