关于FPGA的功耗评估需要知道些什么

可编程逻辑

描述

经常接到工程师的电话,问所选择的FPGA或SOC的功耗情况,有没有典型值。其实针对功耗设计,工程师可以在设计的各个阶段更加准确把握,以xilinx FPGA为例:

1.项目设计初期

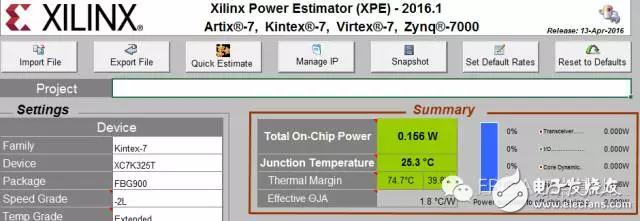

项目设计初期会选型,工程师根据资源、IO、硬核、IP等选择对应型号的FPGA。功耗部分xilinx提供了XPE表格(Xilinx PowerEstimator),这个XPE支持zynq、目前也有各个系列的器件列表,包括最新的ultrascale + 。

图1.XPE的表格界面

这是比较容易使用的表格、图形化,包括器件、散热条件、PCB层数、主要IP和硬核资源的占用情况。当然再设计的初期,工程师是很难精确把握资源占用率的。硬核和IP的占用情况比较好评估,比如是否使用DDR的MIG等。

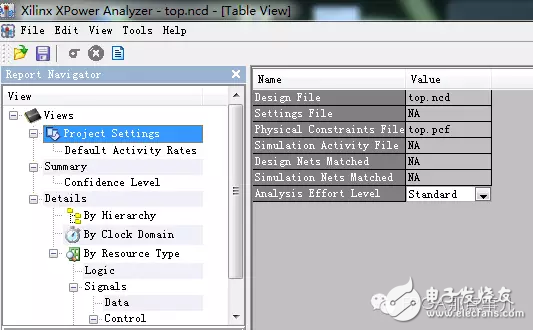

2. 当完成设计的工程版本后,ISE和vivado都支持比较准确的功耗评估工具。ISE对应的XPA小插件,在完成布局布线的bit文件后打开xilinx XPoweranalyzer ,能够看到detail的资源报告,注意修改环境参数,需要更新power结果。

图2.XPA的界面

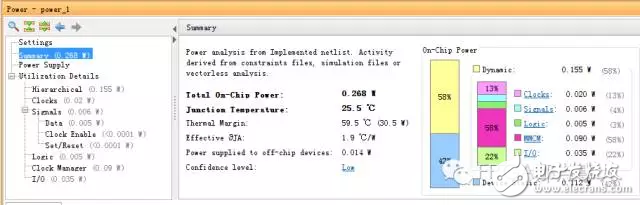

相比ISE,vivado 的report power更加准确,可以设置更多的环境条件。

图3.vivado power setting

Vivado中针对power的图形化分类更加准确和详细,动态功耗、静态功耗都有清晰描述。这也是工程师降低功耗的优化方向。

图4.vivado report power 结果

3. 上板调试阶段

在完成工程后,很多工程师都希望实测FPGA的功耗;但实际上FPGA分为vccint、VCCO、VCCAUX等电压,PCB板子上有很多器件,如DSP、ADC、memory等。比较难估算和测试单独FPGA的功耗。可以通过FPGA JTAG加载前后电流变化对比动态功耗的增加情况。

降低和评估功耗是FPGA硬件设计的工作之一,在设计初期的预估功耗、设计后期的降低功耗都是FPGA工程师的设计挑战和难点。这也是产品量产的关键因素之一,因为功耗影响产品的稳定性、可靠性和结构设计等。

-

关于低功耗蓝牙连接功耗的评估2025-04-26 561

-

CAN报文解析需要知道DBC的哪些信息排序方式2022-01-12 2841

-

关于 EMC 损失你需要知道的2022-06-18 3390

-

关于Android需要知道的一些事2017-09-25 676

-

程序员需要知道的那些定理和法则2019-05-17 3942

-

电气人需要知道的10个常识2020-07-03 4428

-

关于PCB设计,需要知道的几个EMI指南2021-01-25 1137

-

关于伺服电机有哪些需要知道的呢?资料下载2021-04-21 996

-

关于隔离器件,你需要知道的三件事2022-10-28 838

-

您需要知道的CMRR——运算放大器(第1部分)2022-11-02 722

-

对于汽车中的Bluetooth Smart,你需要知道的内容2022-11-04 578

-

每个Linux用户都需要知道的重要Bash shell变量2023-02-13 1793

-

关于步进电机你需要知道的一切2023-03-07 3193

-

弹簧拉压试验机需要知道的小知识2023-08-24 1540

-

贴片电容型号除了要知道参数规格外还有哪些要知道2024-09-21 1189

全部0条评论

快来发表一下你的评论吧 !