CDCLVP111-SP 低电压1:10 LVPECL可选择性输入时钟驱动器技术文档总结

描述

CDCLVP111-SP时钟驱动器将1对LVPECL输入差分时钟(CLK0、CLK1)分配到10对差分LVPECL时钟(Q0、Q9)输出,时钟分配偏斜最小。CDCLVP111-SP可以接受两个时钟源进入输入多路复用器。CDCLVP111-SP 专为驱动 50Ω 传输线而设计。当不使用输出引脚时,建议将引脚保持打开状态以降低功耗。如果仅使用差分对的一个输出引脚,则另一个输出引脚必须相同端接至50Ω。

*附件:cdclvp111-sp.pdf

如果需要单端输入作,则使用VBB基准电压输出。在这种情况下,VBB 引脚必须连接到 CLK0,并使用 10nF 电容器旁路到 GND。

为了获得高速性能,强烈建议使用差分模式。

CDCLVP111-SP 的工作温度为 –55°C 至 125°C。

特性

- 将一个差分时钟输入对LVPECL分配到10个差分LVPECL

- 与 LVECL 和 LVPECL 完全兼容

- 支持2.375V至3.8V的宽电源电压范围

- 通过CLK_SEL可选择时钟输入

- 用于时钟分配应用的低输出偏斜(典型值15ps)

- 附加抖动小于 1ps

- 传播延迟小于355ps

- 打开输入默认状态(Open Input Default State)

- 兼容 LVDS、CML、SSTL 输入

- VBB基准电压输出,用于单端时钟

- 频率范围从直流到3.5GHz

- 支持国防、航空航天和医疗应用

- 受控基线

- 一个组装和测试站点

- 一个制造现场

- 提供军用(–55°C 至 125°C)温度范围^(1)^

- 延长产品生命周期

- 扩展产品变更通知

- 产品可追溯性

参数

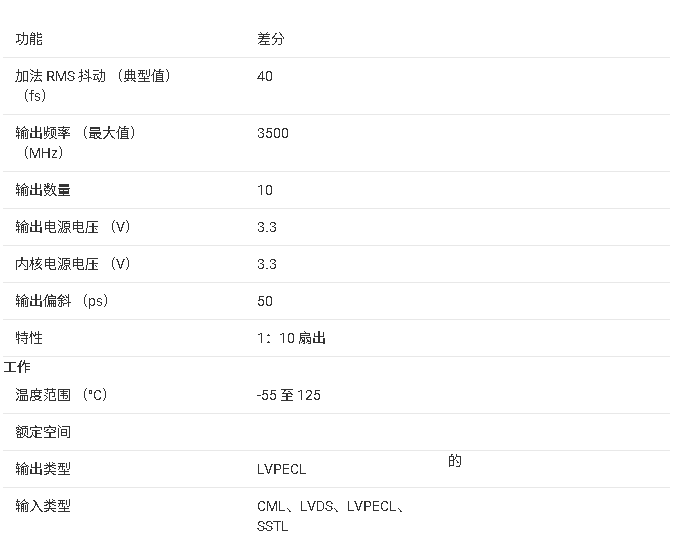

1. 核心特性

- 输入/输出配置:支持1对差分LVPECL输入(CLK0/CLK1)分配至10对差分LVPECL输出(Q0-Q9),支持输入选择(CLK_SEL引脚控制)。

- 电气性能:

- 工作电压范围:2.375V至3.8V(LVPECL模式)或±2.375V至±3.8V(LVECL模式)。

- 低输出偏斜:典型值15ps,最大值50ps。

- 高频率支持:DC至3.5GHz,传播延迟<355ps,附加抖动<1ps。

- 兼容性:支持LVDS、CML、SSTL输入,提供VBB参考电压输出用于单端时钟输入。

2. 关键应用场景

- 高精度时钟分配:适用于国防、航空航天、医疗等严苛环境。

- 传输线驱动:专为50Ω传输线设计,推荐未使用的输出引脚悬空以降低功耗。

- 冗余设计:双输入选择(CLK0/CLK1)增强系统可靠性。

3. 功能模块与引脚

- 功能框图:包含输入多路复用器(IN_MUX)、VBB参考电压生成器及10路LVPECL输出缓冲器。

- 关键引脚:

- CLK_SEL(引脚2):选择输入时钟源(LVTTL/LVCMOS兼容)。

- VBB(引脚5):单端输入时的参考电压输出。

- Q[9:0]/Q[9:0] :差分输出对,需匹配50Ω终端电阻。

4. 电气规格

- 绝对最大额定值:电源电压±4.6V,ESD防护(HBM±2000V,CDM±1000V)。

- 热性能:结至环境热阻95.7°C/W(HFG封装)。

- AC特性:输出上升/下降时间240ps(20%-80%),相位噪声优化设计。

5. 应用设计指南

- 终端匹配:

- LVPECL输出:推荐50Ω至VCC-2V终端(DC耦合)或AC耦合方案(见图7-2/7-3)。

- 输入接口:支持DC耦合(LVCMOS/LVDS)和AC耦合(差分输入),需靠近驱动端布局。

- 电源滤波:建议使用0.1μF高频去耦电容及铁氧体磁珠抑制噪声(见图7-12)。

6. 封装与订购信息

- 封装:36引脚陶瓷扁平封装(HFG),尺寸9.08mm×9.08mm。

- 型号选项:包括工业级(CDCLVP111-SP)和工程样品(CDCLVP111HFG/EM)。

7. 文档支持

- 提供评估模块(EVM)用户指南,可通过TI官网订阅文档更新通知。

总结:CDCLVP111-SP是一款高性能、低抖动的时钟分配器,适用于高可靠性和高频场景,设计时需注意终端匹配、电源去耦及热管理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDCLVP110:高性能低电压时钟驱动器的卓越之选2026-02-10 226

-

低电压 1:10 LVPECL 可选择输入时钟驱动器 CDCLVP111-EP 深度解析2026-02-09 227

-

德州仪器CDCLVP111-SP:高性能时钟驱动解决方案2026-02-08 433

-

深入解析CDCLVP111-SEP:低电压1:10 LVPECL时钟驱动器2026-02-06 353

-

CDCLVP110 1:10 LVPECL/HSTL时钟驱动器技术文档总结2025-09-22 924

-

CDCLVP111 低电压1:10 LVPECL时钟驱动器技术文档总结2025-09-18 822

-

CDCLVP111-EP 低电压1:10 LVPECL时钟驱动器技术文档总结2025-09-15 2627

-

CDCLVP110带可选输入时钟驱动器数据表2024-08-22 364

-

CDCVF111 1:9差分LVPECL时钟驱动器数据表2024-08-21 450

-

CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表2024-08-20 413

-

CDCLVP111-SP CDCLVP111-SP 具有可选输入时钟驱动器的低电压 1:10 LVPECL2018-11-02 664

全部0条评论

快来发表一下你的评论吧 !