NVMe高速传输之摆脱XDMA设计25: NVMe 子系统模型设计

电子说

1.4w人已加入

描述

NVMe 子系统模型是用来模拟 NVMe 子系统的功能仿真模型。 在当前的技术背景下, 单一的存储设备难以满足巨大的存储容量和速度需求, 因此很多存储系统都采用 PCIe 交换机来拓展链路, 或通过 RAID 技术来提升存储性能, 这些都使 PCIe 链路拓扑结构变得更加复杂。 此外基于 PCIe 的 NVMe 协议在执行过程中需要通过 PCIe链路与主机控制器完成大量的指令和数据交互, 这使得如何在仿真环境下模拟复杂拓扑链路中的 NVMe 存储设备功能成为急需解决的关键问题。 因此本IP提出 NVMe子系统模型的设计理念, 并将其整合到验证平台中, 使 NoP 逻辑加速引擎能够在较复杂存储子系统中做系统性的功能验证, 同时降低了设计与验证的迭代成本。

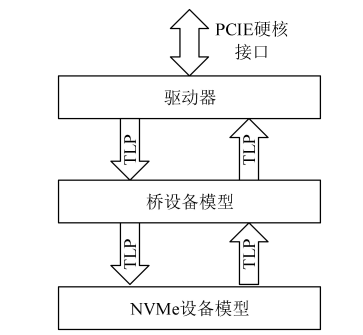

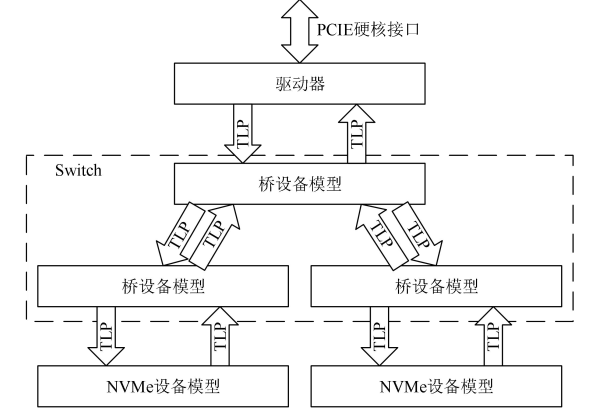

NVMe 子系统模型由模块化的关键组件构成, 主要包含驱动器、 桥设备模型、NVMe 设备模型。 不带交换设备的最小 NVMe 子系统模型如图 1 所示。 带有交换设备的最小 NVMe 子系统模型如图 2 所示。在构建测试平台的过程中, 可以根据需求在最小存储子系统模型的基础上添加组件来构建合适的 PCIe 链路拓扑结构。

图1 最小 NVMe 子系统模型

图2 最小 NVMe 子系统模型

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

NVMe高速传输之摆脱XDMA设计42:DMA 读写功能验证与分析2025-10-27 1058

-

NVMe高速传输之摆脱XDMA设计33:初始化功能验证与分析2025-10-08 1437

-

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计2025-09-29 2605

-

NVMe高速传输之摆脱XDMA设计27: 桥设备模型设计2025-09-18 1908

-

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计2025-08-29 1543

-

NVMe高速传输之摆脱XDMA设计23:UVM验证平台2025-08-26 1049

-

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计2025-08-12 2073

-

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计2025-08-07 1299

-

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计2025-08-04 1501

-

NVMe高速传输之摆脱XDMA设计18:UVM验证平台2025-07-31 14559

-

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化2025-07-26 954

-

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计2025-07-05 1116

-

NVMe高速传输之摆脱XDMA设计之七:系统初始化2025-07-04 1364

-

NVMe IP over PCIe 4.0:摆脱XDMA,实现超高速!2025-04-16 1081

全部0条评论

快来发表一下你的评论吧 !