LMK03318 具有单 PLL 的超低抖动时钟发生器系列技术手册

描述

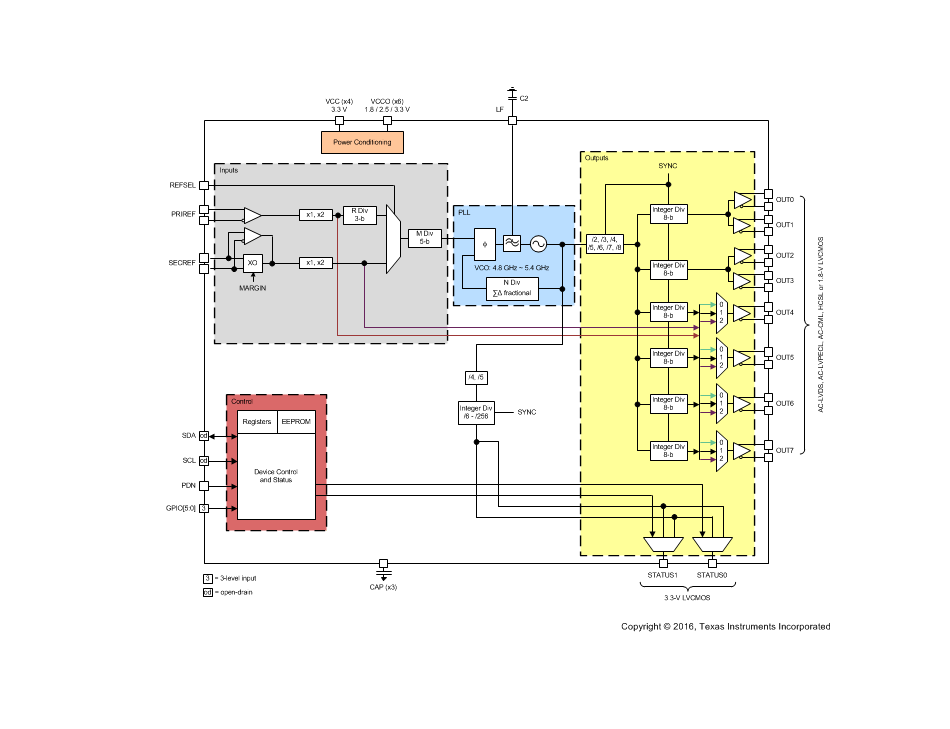

LMK03318器件是一款超低噪声PLLATINUM™时钟发生器,具有一个小数N频率合成器,集成了VCO、灵活的时钟分配和扇出,以及存储在片上EEPROM中的引脚可选配置状态。该器件可以为各种多千兆位串行接口和数字设备生成多个时钟,从而降低BOM成本和电路板面积,并通过替代多个振荡器和时钟分配设备来提高可靠性。超低抖动可降低高速串行链路中的误码率 (BER)。

对于PLL,可以选择差分时钟、单端时钟或晶体输入作为参考时钟。选定的基准输入可用于将VCO频率锁定在基准输入频率的整数或小数倍。VCO 频率可在 4.8 GHz 至 5.4 GHz 之间调谐。PLL 可以根据应用的需要灵活地选择预定义或用户定义的环路带宽。PLL 有一个后分频器,可以在除频 2、3、4、5、6、7 或 8 之间进行选择。

*附件:lmk03318.pdf

所有输出通道都可以从PLL中选择分频VCO时钟作为输出分频器的源,以设置最终输出频率。一些输出通道还可以独立选择PLL的基准输入作为旁路到相应输出缓冲器的替代源。8位输出分频器支持1至256(偶数或奇数)的分频范围、高达1 GHz的输出频率以及输出相位同步功能。

所有输出对都是以地为基准的CML驱动器,具有可编程摆幅,可通过交流耦合连接到LVDS、LVPECL或CML接收器。所有输出对也可以独立配置为 HCSL 输出或 2 × 1.8V LVCMOS 输出。与压基准驱动器设计(如传统 LVDS 和 LVPECL 驱动器)相比,这些输出在 1.8 V 时具有更低的功耗、更高的性能和电源抗噪性以及更低的 EMI。可以通过STATUS引脚获得两个额外的3.3V LVCMOS输出。这是一项可选功能,如果需要 3.3V LVCMOS 输出并且不需要器件状态信号。

该器件具有从片上可编程EEPROM或预定义ROM存储器自启动的功能,可提供多种自定义器件模式,可通过引脚控制选择,无需串行编程。器件寄存器和片内EEPROM设置可通过I进行完全编程^2^C 兼容串行接口。器件从地址可在EEPROM中进行编程,LSB可以通过3态引脚进行设置。

该器件提供两种频率裕度选项,具有无毛刺作,以支持系统设计验证测试 (DVT),例如标准合规性和系统时序裕度测试。通过在内部晶体振荡器(XO)上使用低成本的可拉式晶体,并选择该输入作为PLL频率合成器的基准电压源,可以支持精细的频率裕量(以ppm为单位)。频率裕度范围由晶体的微调灵敏度和片内变容极管范围决定。XO 频率裕度可通过引脚或 I 进行控制^2^C 控制,易于使用且具有高灵活性。通过通过I更改输出分频值,可以在任何输出通道上获得粗频率裕度(以%)为单位^2^C 接口,同步停止和重新启动输出时钟,以防止分频器发生变化时出现毛刺或欠幅脉冲。

内部电源调节提供出色的电源噪声抑制 (PSNR),从而降低供电网络的成本和复杂性。模拟和数字内核模块采用3.3V±5%电源供电,输出模块采用1.8V、2.5V或3.3V±5%电源供电。

特性

- 超低噪音、高性能

- 抖动:100-fs RMS(典型值),F

外> 100 兆赫 - PSNR:–80 dBc,稳健的电源抗噪性

- 抖动:100-fs RMS(典型值),F

- 灵活的设备选项

- 多达 8 个 AC-LVPECL、AC-LVDS、AC-CML、HCSL 或 LVCMOS 输出,或任意组合

- 引脚模式,I^2^C 模式、EEPROM 模式

- 71引脚可选预编程默认启动选项

- 双输入,自动或手动选择

- 晶体输入:10 至 52 MHz

- 外部输入:1 至 300 MHz

- 频率裕量选项

- 使用低成本可拉取晶体基准电压源实现精细频率裕度

- 使用输出分频器的无毛刺粗频裕度 (%)

- 其他功能

- 电源:3.3V内核、1.8V、2.5V或3.3V输出电源

- 工业温度范围(–40ºC 至 85ºC)

参数

方框图

1. 产品概述

LMK03318是德州仪器(TI)推出的超低噪声抖动时钟发生器系列产品,具有以下关键特性:

- 超低噪声性能:典型抖动为100-fs RMS (输出频率>100MHz)

- 灵活配置:支持8路AC-LVPECL/AC-LVDS/AC-CML/HCSL/LVCMOS输出组合

- 双输入设计:支持晶体输入(10-52MHz)和外部时钟输入(1-300MHz)

- 频率微调功能:可通过晶体负载微调或输出分频器实现精细/粗调

- 工作温度范围:-40°C至85°C工业级

2. 主要特性

2.1 时钟性能

- 支持4.8-5.4GHz VCO频率范围

- 集成分数/整数PLL

- 输出频率可达1GHz

- 支持PCIe Gen1/2/3/4时钟规范

2.2 接口与控制

- 三种工作模式:引脚模式(ROM)、I2C模式(EEPROM)和寄存器默认模式

- 可通过I2C接口(支持100/400kHz)编程配置

- 提供状态监控输出(STATUS0/1)

2.3 电源特性

- 核心电源:3.3V ±5%

- 输出电源:1.8V/2.5V/3.3V ±5%可选

- 优异的电源噪声抑制(PSNR)性能

3. 应用领域

- 交换机和路由器

- 网络和电信线路卡

- 服务器和存储系统

- 无线基站

- 测试测量设备

- 广播基础设施

4. 功能描述

LMK03318采用单PLL架构,包含:

- 灵活的时钟分配和扇出

- 可编程输出分频器(1-256)

- 片上EEPROM存储配置

- 自动输入切换功能

5. 封装信息

- 48引脚WQFN封装(7mm×7mm)

- 热阻特性:θJA=26.47°C/W(无气流)

6. 技术规格

- 相位噪声:典型-164dBc/Hz @156.25MHz(AC-LVPECL)

- 随机抖动:典型100fs RMS(12kHz-20MHz积分带宽)

- 功耗:典型158mA(全功能工作)

文档还包含详细的寄存器映射表、电气特性参数、典型应用电路和布局指南等内容。

-

LMK03806 具有 14 个输出的超低抖动时钟发生器技术手册2025-09-16 646

-

LMK03328 具有两个独立 PLL 的超低抖动时钟发生器系列技术手册2025-09-14 863

-

LMK03318如何使用TICS将程序烧录进ROM?2025-07-07 5227

-

使用LMK03318进行设计,LF引脚PLL loop filter电容值选择多少值,对输出抖动影响最小?2024-11-11 404

-

具有两个独立PLL、八路输出、集成EEPROM的LMK03328超低抖动时钟发生器数据表2024-08-21 360

-

具有14个可编程输出的LMK03806超低抖动时钟发生器数据表2024-08-20 380

-

评估低抖动PLL时钟发生器的电源噪声抑制2023-04-11 2439

-

超低抖动时钟发生器如何优化串行链路系统性能2022-11-04 619

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1103

-

超低抖动时钟发生器与串行链路系统性能的优化2018-09-05 2201

-

MAX3625B 抖动仅为0.36ps的PLL时钟发生器2010-03-01 1609

-

评估低抖动PLL时钟发生器的电源噪声抑制性能2009-09-18 1852

全部0条评论

快来发表一下你的评论吧 !