CDCM6208V1F 时钟发生器与抖动清除器技术文档总结

描述

该CDCM6208V1F是一款高度通用、低抖动、低功耗频率合成器,具有以下特点: 可产生八个低抖动时钟输出,可在类似LVPECL的高摆幅CML之间进行选择, 正常摆幅 CML、类似 LVDS 的低功耗 CML、HCSL 或 LVCMOS,来自两个输入之一,可具有 用于各种无线的低频晶体或 CML、LVPECL、LVDS 或 LVCMOS 信号 基础设施基带、有线数据通信、计算、低功耗医学成像和 便携式测试和测量应用。该CDCM6208V1F还具有创新的小数分频器架构,适用于其四个 可以生成任何频率的输出,频率精度优于 1ppm。The CDCM6208V1F 可以通过 I 轻松配置^2^C 或 SPI 编程接口和 没有串行接口,也提供引脚模式,可以将设备设置为 1 中的 32 使用控制引脚的不同预编程配置。

*附件:cdcm6208v1f.pdf

在 合成器模式下 ,整体输出抖动性能小于 0.5 ps-rms (10 k – 20 MHz) 或 20 ps-pp (无绑定)在使用整数分频器的输出上,在使用 分数分频器取决于预分频器输出频率。

在 抖动清除模式下 ,输出上的总输出抖动小于 2.1 ps-rms (10 k – 20 MHz) 或 40 ps-pp 使用整数分频器,在使用分数分频器的输出上小于 70 ps 至 240 ps-pp。这 CDCM6208V1F采用小型 48 引脚 7 mm × 7 mm QFN 封装。

特性

- 低功耗的卓越性能:

- 低噪声合成器(265 fs-rms典型

抖动)或低噪声抖动清除器(1.6 ps-rms

典型抖动) - 0.5 W 典型功耗

- 高通道间隔离和

出色的PSRR - 器件性能可通过灵活的 1.8 V、2.5 V 和 3.3 V 电源

进行

定制,允许混合输出电压

- 低噪声合成器(265 fs-rms典型

- 灵活的频率规划:

- 4 个整数下分差分时钟

输出,支持 LVPECL、CML 或

LVDS 信号 - 4 个分数或整分差分

时钟输出,支持 HCSL、类

LVDS 信号或 8 个 CMOS 输出 - 分数输出分压器实现 0 ppm 至 < 1

ppm 频率误差,

无需晶体振荡器和其他时钟发生器 - 输出频率高达 800 MHz

- 4 个整数下分差分时钟

- 两个差分输入,XTAL支持,智能切换能力

- SPI,我^2^C™ 和引脚可编程

- 专业用户 GUI 可快速完成设计

周转 - 7 × 7 mm 48-QFN 封装 (RGZ)

- –40 °C 至 85 °C 温度范围

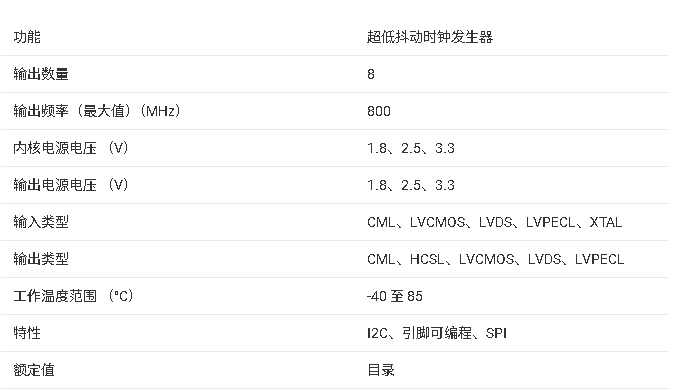

参数

方框图

1. 产品概述

CDCM6208V1F是德州仪器(TI)推出的高性能低功耗时钟发生器与抖动清除器,支持2:8时钟输出配置,集成分数分频器。关键特性包括:

- 低噪声性能:合成器模式下典型抖动265 fs-rms(整数分频)或1.6 ps-rms(抖动清除模式)。

- 灵活频率规划:支持LVPECL、CML、LVDS、HCSL和LVCMOS多种输出信号类型,输出频率最高达800 MHz。

- 多协议接口:支持SPI、I2C和引脚编程,提供32种预配置模式。

2. 主要应用场景

- 无线基础设施基带时钟

- 网络与数据通信

- 医疗影像及高端音视频设备

- Keystone C66x多核DSP时钟

3. 核心功能模块

- 输入接口:双差分输入(PRI_REF/SEC_REF),支持晶体振荡器(10-50 MHz)和外部参考时钟(8 kHz-250 MHz)。

- PLL架构:集成VCO(2.39-2.55 GHz)、可编程电荷泵(0.5-4 mA)及部分外部环路滤波器。

- 输出分频器:

- 整数分频(Y0-Y3):1.55-800 MHz,低抖动。

- 分数分频(Y4-Y7):0.78-400 MHz,精度优于1 ppm。

4. 关键性能参数

- 抖动性能:

- 合成器模式:整数分频输出抖动<0.5 ps-rms,分数分频50-220 ps-pp。

- 抖动清除模式:整数分频<2.1 ps-rms,分数分频70-240 ps-pp。

- 电源管理:典型功耗0.5 W,支持1.8 V/2.5 V/3.3 V混合供电。

5. 封装与工作条件

- 封装:48引脚7×7 mm QFN(RGZ),工作温度-40°C至85°C。

- 热阻:结到环境热阻30.27°C/W(无气流)。

6. 设计支持

- 提供用户GUI工具简化频率规划和环路滤波器配置。

- 支持输出同步(SYNCN引脚)和多器件级联,确保系统时钟对齐。

7. 典型应用示例

- SERDES系统:通过低通滤波适配DSP的TX PLL带宽,满足10GbE链路抖动预算。

- ADC/DAC时钟:实测支持100 MHz中频信号,SNR性能媲美实验室级时钟源。

-

CDCM6208:多功能时钟发生器与抖动清理器的深度解析2026-02-09 300

-

CDCM6208V2G:高度灵活的时钟生成与抖动清理利器2026-02-08 667

-

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结2025-09-17 1003

-

CDCM6208 2:8时钟发生器与分数分频器的抖动清除器总结2025-09-15 892

-

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表2024-08-22 967

-

CDCM6208V1F具有小数分频器的2:8时钟生成器/抖动消除器数据表2024-08-20 543

-

CDCM6208 2:8 超低功耗、低抖动时钟发生器2019-04-18 2268

-

双环路时钟发生器可清除抖动并提供多个高频输出2016-01-04 695

全部0条评论

快来发表一下你的评论吧 !