LMK04821 超低抖动合成器和抖动清除器技术手册

描述

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B 转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK0482x 系列具有高性能,加上在功率或性能之间权衡的能力、双 VCO、动态数字延迟、保持和无毛刺模拟延迟等功能,是提供灵活的高性能时钟树的理想选择。

*附件:lmk04821.pdf

特性

- JEDEC JESD204B支持

- 超低 RMS 抖动

- 88 fs RMS 抖动(12 kHz 至 20 MHz)

- 91 fs RMS 抖动(100 Hz 至 20 MHz)

- 245.76 MHz时–162.5 dBc/Hz本底噪声

- PLL2 提供多达 14 个差分器件时钟

- 多达 7 个 SYSREF 时钟

- 最大时钟输出频率 3.1 GHz

- 来自 PLL2 的 LVPECL、LVDS、HSDS、LCPECL 可编程输出

- PLL1 多达 1 个缓冲 VCXO/晶体输出

- LVPECL、LVDS、2xLVCMOS 可编程

- 双环路PLLatinum™ PLL架构

- PLL1

- 多达 3 个冗余输入时钟

- 自动和手动切换模式

- 无中断开关和LOS

- 集成低噪声晶体振荡器电路

- 输入时钟丢失时的保持模式

- 多达 3 个冗余输入时钟

- PLL2

- 归一化 [1 Hz] PLL 本底噪声为

–227 dBc/Hz - 相位检测器速率高达 155 MHz

- OSCin 倍频器

- 两个集成低噪声VCO

- 归一化 [1 Hz] PLL 本底噪声为

- 50% 占空比输出分频,1 至 32

(偶数和奇数) - 精密数字延迟,动态可调

- 25 ps 步进模拟延迟

- 多模:双 PLL、单 PLL 和时钟分配

- 工业温度范围:–40 至 85°C

- 支持 105°C PCB 温度(在导热垫处测量)

- 3.15V 至 3.45V 工作电压

- 封装:64引脚QFN(9.0 mm × 9.0 mm × 0.8 mm)

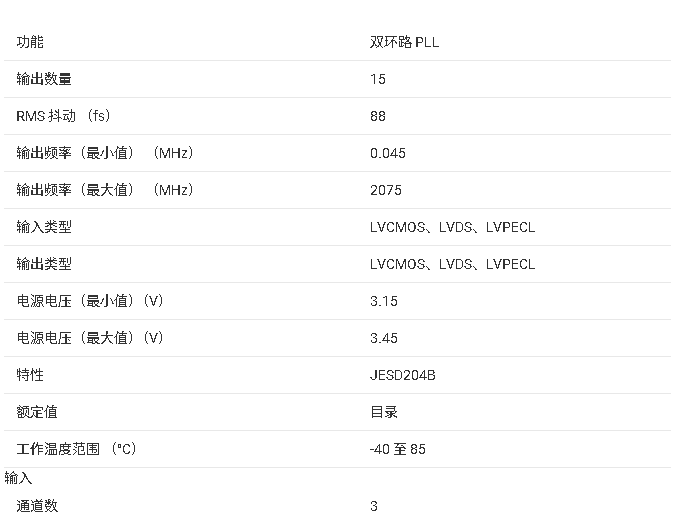

参数

1. 产品概述

LMK04821/LMK04826/LMK04828是德州仪器(TI)推出的高性能双锁相环(PLL)时钟调节器,专为无线基础设施、数据转换器时钟、医疗/军事/航空航天等应用设计。核心特性包括:

- 超低抖动性能:RMS抖动低至88 fs(12 kHz–20 MHz带宽)。

- JESD204B支持:提供14路可配置差分时钟输出(7组设备时钟+7组SYSREF时钟),支持多通道同步。

- 双PLL架构:

- PLL1:支持3路冗余参考输入,集成VCXO/晶体振荡器电路,具备自动/手动切换和保持模式(Holdover)。

- PLL2:集成双VCO(频率范围1.84–3.08 GHz),支持动态数字延迟和模拟延迟调整。

- 灵活输出配置:支持LVDS、LVPECL、HSDS、LCPECL等多种格式,最高输出频率3.1 GHz。

2. 关键特性

- 低噪声设计:噪声底低至-162.5 dBc/Hz(245.76 MHz)。

- 高集成度:内置可编程环路滤波器、数字延迟模块(25 ps步进)及频率保持功能。

- 工作条件:3.15–3.45 V供电,工业级温度范围(-40°C至85°C)。

3. 应用场景

- 无线通信:基站时钟同步。

- 高速数据转换:JESD204B接口ADC/DAC的时钟分配。

- 测试测量:高精度仪器时钟生成。

4. 文档结构

- 电气特性:详细列出各模块参数(如VCO调谐范围、相位噪声、功耗等)。

- 功能描述:包括PLL工作原理、时钟分配路径及零延迟模式配置。

- 寄存器配置:提供SPI编程指南及典型应用寄存器设置示例。

5. 设计支持

- 工具推荐:PLLatinum Sim用于环路滤波器设计,TICS Pro生成寄存器配置。

- 布局建议:强调电源去耦、信号隔离以优化噪声性能。

注:具体型号差异(如LMK04821的VCO1分频器)需参考设备选型表。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析2026-02-09 199

-

低噪声时钟抖动清除器LMK04610:技术拆解与应用设计2026-02-08 712

-

LMK5C33414A:高性能网络同步器与抖动清除器的深度剖析2026-02-06 477

-

LMK04610 超低噪声和低功耗 JESD204B 兼容时钟抖动清除器技术手册2025-09-13 1296

-

LMK04821遇到的问题求解2024-11-11 372

-

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表2024-08-20 425

-

超低抖动时钟频率合成器的设计挑战2023-01-16 2389

-

LMK04832-SP时钟抖动清除器2021-03-24 1492

-

能有效降低高速网络误码率的超低抖动时钟合成器2018-10-31 4859

-

超低抖动时钟合成器的设计挑战2009-04-21 1067

全部0条评论

快来发表一下你的评论吧 !