LMK00804B 低偏斜1:4多路复用差分/LVCMOS至LVCMOS/TTL扇出缓冲器技术文档总结

描述

LMK00804B是一个低偏斜、高性能的时钟扇出缓冲器,可以向上分布 从两个可选电平之一到四个LVCMOS/LVTTL输出(3.3V、2.5V、1.8V或1.5V电平) 输入,可以接受差分或单端输入。时钟使能输入为 内部同步,以消除时钟使能时输出上的欠幅或毛刺脉冲 终端被断言或取消断言。当时钟为时钟时,输出保持在逻辑低电平状态 禁用。单独的输出使能端子控制输出是处于活动状态还是 高阻抗状态。低附加抖动和相位本底噪声,并保证输出和 零件间偏斜特性使该LMK00804B非常适合要求高 性能和可重复性。

*附件:lmk00804b.pdf

特性

- 4个LVCMOS/LVTTL输出,输出阻抗为7 Ω

- 附加抖动:0.04 ps RMS(典型值)@ 125 MHz

- 本底噪声:–166 dBc/Hz(典型值)@ 125 MHz

- 输出频率:350 MHz(最大值)

- 输出偏斜:35 ps(最大值)

- 零件间偏斜:700 ps(最大值)

- 两个可选输入

- CLK、nCLK 对接受 LVPECL、LVDS、

HCSL、SSTL、LVHSTL 或 LVCMOS/LVTTL - LVCMOS_CLK 接受 LVCMOS/LVTTL

- CLK、nCLK 对接受 LVPECL、LVDS、

- 同步时钟使能

- 核心/输出电源:

- 3.3 伏/3.3 伏

- 3.3 伏/2.5 伏

- 3.3 伏/1.8 伏

- 3.3 伏/1.5 伏

- 封装:16引脚TSSOP

- 工业温度范围:–40ºC 至 +85ºC

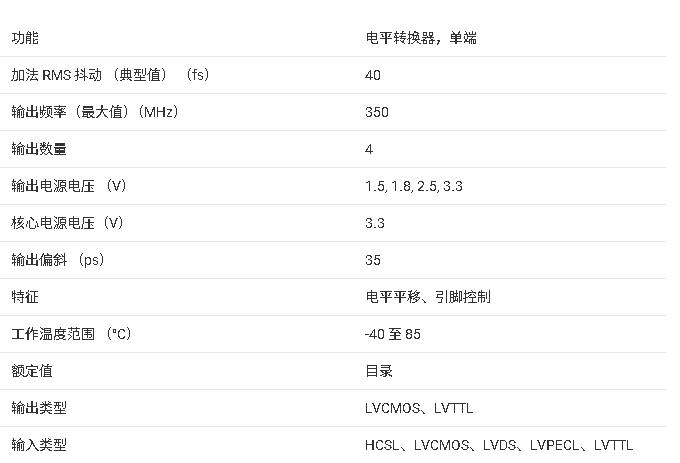

参数

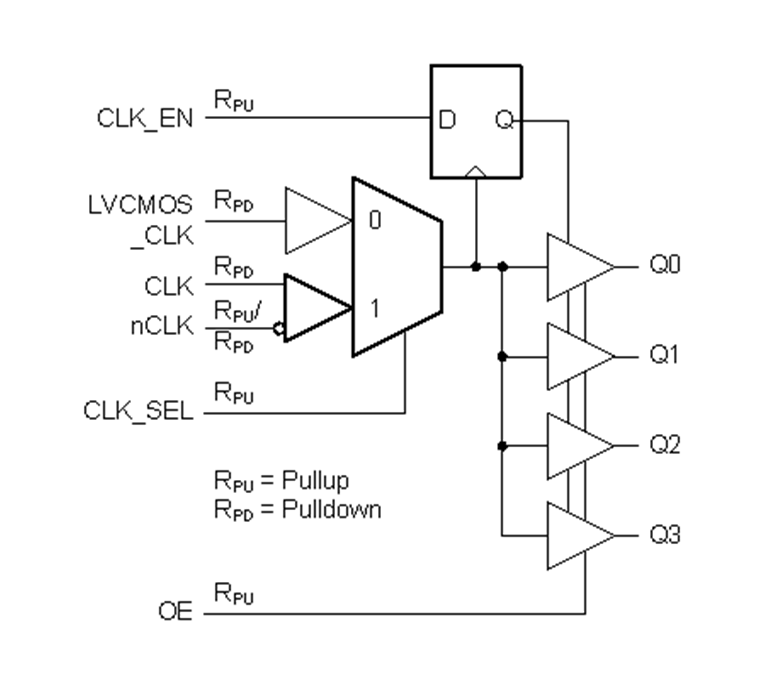

方框图

1. 核心特性

- 输出配置:4路LVCMOS/LVTTL输出,阻抗7Ω,支持3.3V/2.5V/1.8V/1.5V电平。

- 关键性能:

- 附加抖动:0.04 ps RMS(典型值,125 MHz)

- 噪声基底:-166 dBc/Hz(典型值,125 MHz)

- 最大输出频率:350 MHz

- 输出偏斜:35 ps(最大值)

- 器件间偏斜:700 ps(最大值)

- 关键性能:

- 输入选择:

- 双路可选输入(CLK/nCLK对支持LVPECL/LVDS/HCSL等差分信号,LVCMOS_CLK支持单端LVCMOS/LVTTL)。

- 同步使能:时钟使能信号(CLK_EN)可消除输出端的毛刺脉冲。

- 电源配置:支持多电压组合(如3.3V核心/3.3V输出、3.3V核心/1.5V输出等)。

- 封装:16引脚TSSOP,工业级温度范围(-40°C至+85°C)。

2. 应用领域

- 无线/有线基础设施、网络通信、服务器、医疗成像、高端音视频设备及便携测试仪器。

3. 功能描述

- 低抖动设计:优化相位噪声和附加抖动,适合高精度时钟分配。

- 灵活输入接口:支持差分或单端输入,内部同步逻辑确保输出稳定性。

- 电源管理:独立核心与输出电源引脚,支持动态功耗控制。

4. 关键参数

- 电气特性:

- 传播延迟:1.1~2.3 ns(取决于温度与输入类型)。

- 上升/下降时间:≤700 ps(20%~80%阈值)。

- 热性能:结至空气热阻116°C/W,需注意散热设计。

5. 设计建议

- 布局优化:

- 使用多层板与完整地平面,减少阻抗不连续。

- 输入终端电阻靠近引脚放置,避免过孔干扰。

- 电源滤波:推荐每电源引脚配置0.1 µF去耦电容,必要时串联铁氧体磁珠。

- 未用引脚处理:CLK_SEL/OE等可悬空(内部上拉),输出端未使用时建议浮空。

6. 典型应用电路

- 输入配置:提供LVPECL/LVDS/LVCMOS等接口的详细匹配电路(如HCSL需33Ω终端电阻)。

- 输出配置:43Ω串联电阻靠近输出引脚,匹配50Ω传输线。

7. 文档结构

- 包含特性、引脚定义、电气规格、热参数、应用电路及布局示例(参考EVM设计)。

注:本文档为德州仪器(TI)发布的LMK00804B数据手册精简版,完整信息需参考原文件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析LMK00105:超低抖动LVCMOS扇出缓冲器与电平转换器2026-02-09 300

-

深入剖析 LMK1C110x 系列 LVCMOS 时钟缓冲器2026-02-08 439

-

探索LMK1C110xA:高性能LVCMOS时钟缓冲器的理想选择2026-02-06 317

-

CDCLVD1212 2:12低附加抖动LVDS缓冲器技术文档总结2025-09-16 841

-

LMK00105 超低抖动LVCMOS扇出缓冲器与电平转换器技术文档总结2025-09-15 1163

-

LMK00804B-Q1 1.5V至3.3V 1:4高性能LVCMOS扇出缓冲器与电平转换器技术文档总结2025-09-12 1082

-

LMK1D121x系列低附加抖动LVDS缓冲器技术文档总结2025-09-11 951

-

LMK1C1108低附加相位噪声LVCMOS时钟缓冲器评估板2024-11-16 377

-

LMK00804B低偏移1到4多路复用差动/LVCMOS到LVCMOS/TTL扇出缓冲器数据表2024-08-23 508

-

LMK00804B-Q1 1.5V至3.3V、1路至4路高性能LVCMOS扇出缓冲器和电平转换器数据表2024-08-22 456

全部0条评论

快来发表一下你的评论吧 !